I2C总线是PHLIPS公司在20世纪80年代推出的一种串行总线。具有引脚少,硬件实现简单,可扩展性强的优点。I2C总线的另一优点是支持多主控,总线上任何能够进行发送/接收数据的设备都可以占领总线。当然,任意时间点上只能存在一个主控。

I2C即是一种总线,也是一种通讯协议。在嵌入式开发中,通讯协议可分为两层:物理层和协议层。物理层是数据在物理媒介传输的保障;协议层主要是规定通讯逻辑,同一收发双方的数据打包、解包标准。打个比方,物理层相当于现实中的公路,而协议层则是交通规则,汽车可以在路上行驶,但是需要交通规则对行驶规则进行约束,不然将出现危险,也就是数据传输紊乱、丢包。

1. 物理层

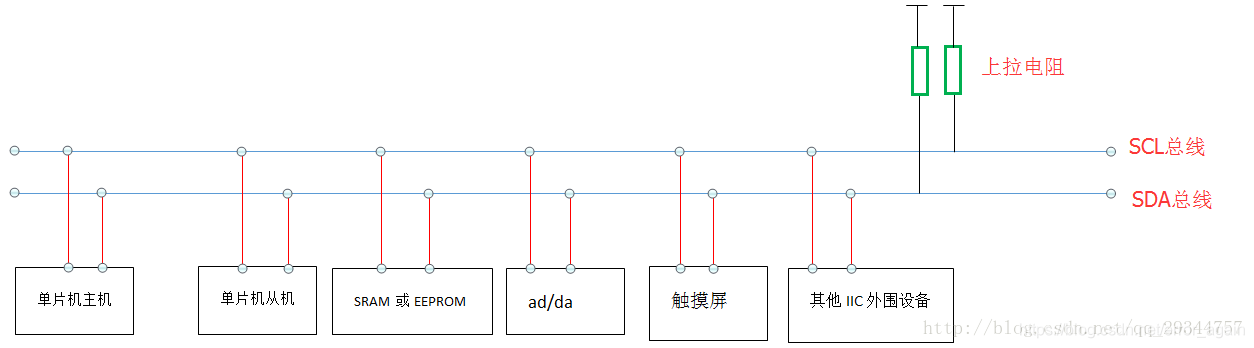

I2C通讯系统接线图如下:

(1) 在I2C通讯总线上,可连接多个I2C通讯设备,支持多个通讯主机和多个通讯从机

(2) I2C通讯只需要两条双向总线:串行数据线(SDA),串行时钟线(SCL)。数据线用于传输数据,时钟线用于同步数据收发

(3) 每个连接到总线的设备都有一个独立的地址,主机正是利用该地址对设备进行访问

(4) SDA和SCL总线都需要接上上拉电阻,当总线空闲时,两根线均为高电平。连接到总线上的任意器件输出低电平都会将总线信号拉低。即各器件的SDA和SCL都是线与的关系

(5) 多个主机同时使用总线时,需要用仲裁方式决定哪个设备占用总线,不然数据将会产生冲突

(6) 串行的8位双向数据传输位速率在标准模式下可达100kbps,快速模式下可达400kbps,高速模式下可达3.4Mbps(目前大多数I2C设备还不支持高速)

2. 协议层

协议层规约了通讯的起始、停止信号,数据有效性、响应、冲裁同步、地址广播等。

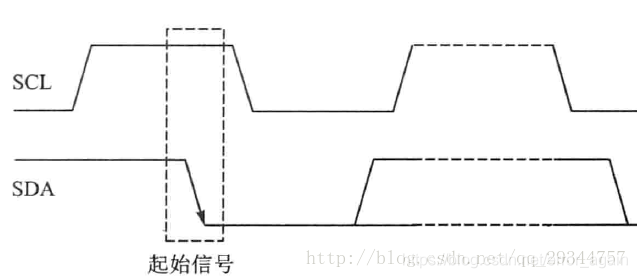

2.1 通讯的起始信号/结束信号

在SCL线为高电平期间,SDA线由高电平向低电平转换表是起始信号。

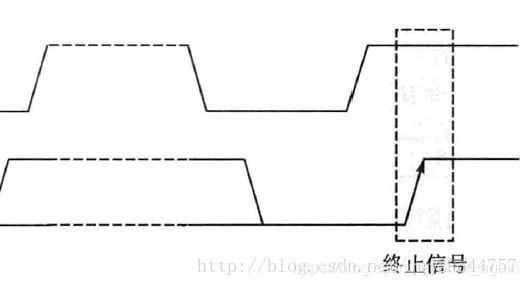

在SCL线为高电平期间,SDA线由低电平向高电平转换表是结束信号。

起始/结束信号都是由主机发出的,在起始信号产生后,总线就处于被占用的状态;在结束信号产生后,总线就处于空闲状态。

需要注意的两点:

(1) 接收器件接收到一个完整的数据字节后,可能需要完成一些其他工作,如处理内部接收中断服务函数等,这就无法立即接收下一字节的数据,这时接收器件可将SCL线拉成低电平,从而使得主机处于等待状态。直至接收器件准备好接收下一字节数据时再释放SCL线使之为高电平。

(2) 连接到I2C总线上的器件,若具有I2C总线控制器那么很硬件会自动检测到起始、结束信号,而对于不具备I2C总线控制器的器件(单片机)来说,需要在每个时钟周期内保证对数据线SDA采样两次,捕获是否接收到起始/结束信号。

2.2 数据传输

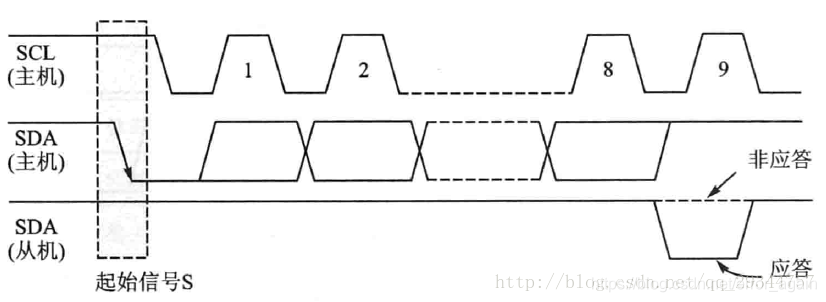

(1) 起始信号后,总线上所有的从机开始等待主机紧接下来的从机地址广播。因为总线上每个设备的地址都是唯一的,当主机广播的地址与某个设备地址相同时,该设备就被选中,并向主机发出应答(ACK)或者非应答(NACK),主机只有在接收到应答信号后继续发送/接收数据,没选中的设备将会忽略之后的数据信号。根据I2C协议,从机地址可以是7位或者10位。

(2) I2C总线上传输的数据包括上述的地址信号,又包括真正的数据信号。在起始信号后需传送一个从机地址(7位),第8位是数据的传输方向(接收/发送),“0”表示主机发送数据,“1”表示主机接收数据。每次数据的传输总是由主机产生结束信号以结束传输,但若主机希望继续占用总线进行新的数据传输时,则可以不产生结束信号,而是再次发送起始信号对另一从机地址寻址。

(3) 若配置为写数据方向,主机开始向从机传输数据,数据包大小为8位,主机每发送完1字节数据都有等到从机的应答信号(ACK),多字节数据发送时重复此过程。传输结束后,主机向从机发送一个停止信号表不再传输数据。

(4) 若配置为读方向,从机开始向主机返回数据,数据包大小还是8位。同理,从机每发送完一字节数据都要等到主机的应答信号(ACK),重复此过程可以返回多个数据。当主机希望停止接收数据时就向返回一个非应答信号(NACK),数据传输将结束。

(5) 实际I2C通讯采用的是读写复合的格式。传输过程中主机需要发出2次起始信号:第一次传输主机通过从机地址找到从机设备,发送一段数据,这个数据是从设备内部寄存器或者存储器地址;第二次传输是对该地址进行读/写。主机要读取从机数据时,主机会释放对SDA总线的控制,由从机控制SDA总线,主机负责接收信号;主机要向从机设备写数据时,SDA由主机控制,从机负责接收信号。

3913

3913

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?