模块程序:

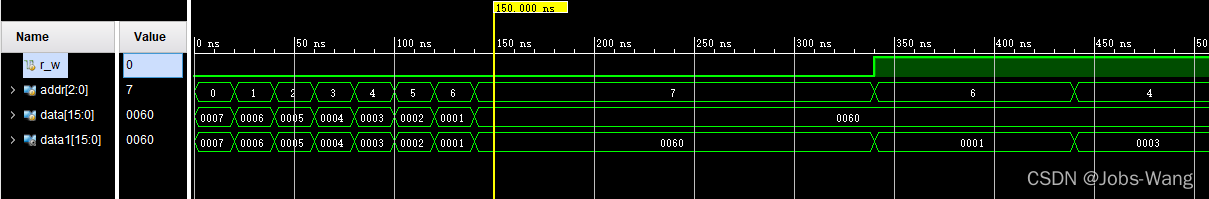

实例化一个8*16的可读写ram,单地址线,双数据线,写入数据马上体现在输出数据线上。

`timescale 1ns / 1ps

module ram1(

input r_w,//读写选控1为读,0为写。

input [2:0] addr,//地址线

input [15:0] data_i,//输入数据

output [15:0] data_o//输出数据

);

reg [15:0] ram [7:0]; //例化8个16位的存储空间

assign data_o=ram[addr];//读操作。

always @(r_w or addr)//当地址和控制线变化时运行,写操作。

if(~r_w)

ram[addr]<=data_i;

endmodule

激励:

`timescale 1ns / 1ps

module test_ram();

reg r_w;

reg [2:0] addr;

reg [15:0] data;

wire [15:0] data1;

ram1 test_rom1(

.r_w(r_w),

.addr(addr),

.data_i(data),

.data_o(data1)

);

initial

begin

r_w=0;

addr=3'b000;

data=16'b0000_0000_0000_0111;

#20

r_w=0;

addr=3'b001;

data=16'b0000_0000_0000_0110;

#20;

r_w=0;

addr=3'b010;

data=16'b0000_0000_0000_0101;

#20

r_w=0;

addr=3'b011;

data=16'b0000_0000_0000_0100;

#20;

r_w=0;

addr=3'b100;

data=16'b0000_0000_0000_0011;

#20

r_w=0;

addr=3'b101;

data=16'b0000_0000_0000_0010;

#20;

r_w=0;

addr=3'b110;

data=16'b0000_0000_0000_0001;

#20

r_w=0;

addr=3'b111;

data=16'b0000_0000_0110_0000;

#200;

r_w=1;

addr=3'b110;

#100;

addr=3'b100;

#100;

end

endmodule

该博客介绍了如何使用VHDL语言设计一个8位地址、16位数据线的可读写RAM模块。模块包含读写控制、地址线和数据输入输出。同时,给出了测试激励,详细展示了如何向RAM写入数据并在不同地址读取,验证了RAM的功能正确性。

该博客介绍了如何使用VHDL语言设计一个8位地址、16位数据线的可读写RAM模块。模块包含读写控制、地址线和数据输入输出。同时,给出了测试激励,详细展示了如何向RAM写入数据并在不同地址读取,验证了RAM的功能正确性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?