Cortex-A运行模型

Cortex-A 处理器运行模型是基于 ARM 架构设计的运行机制,包含处理器的模式、状态、特权级以及指令集的运行方式。Cortex-A 系列处理器是 ARM 的高性能应用处理器,支持复杂操作系统(如 Linux 和 Android),通常用于消费电子、汽车和工业等领域。

1. Cortex-A 处理器的主要运行模式

Cortex-A 处理器在运行过程中,根据任务或事件(如中断或异常)切换不同的模式。每种模式有特定的寄存器访问权限和功能。

1.1 模式分类

ARM 处理器的运行模式可以分为以下几类:

| 模式名称 | 描述 | 典型用途 |

|---|---|---|

| User 模式 | 非特权模式,应用程序运行所在的模式。 | 运行普通用户应用程序。 |

| FIQ 模式 | 快速中断模式,支持高优先级中断服务。 | 处理时间敏感的中断请求。 |

| IRQ 模式 | 普通中断模式,处理标准中断请求。 | 处理外设中断。 |

| Supervisor 模式 | 管理模式,操作系统内核通常运行在此模式。 | 操作系统内核运行,处理系统调用。 |

| Abort 模式 | 数据或指令访问异常模式。 | 用于捕获内存访问错误。 |

| Undefined 模式 | 未定义指令异常模式。 | 捕获未定义指令错误。 |

| System 模式 | 特权模式,和 User 模式寄存器共享。 | 用于操作系统访问硬件资源。 |

| Monitor 模式 | TrustZone 安全扩展模式,提供安全上下文切换。 | 运行安全监控代码。 |

1.2 模式切换

- 异常触发切换: Cortex-A 处理器在接收到中断、异常或系统调用时,从用户模式切换到特定的异常模式(如 FIQ、IRQ、Supervisor)。

- 手动切换: 通过特权指令(如

MSR和MRS)修改控制寄存器来切换模式。

2. 运行状态

Cortex-A 支持两种主要运行状态,用于管理指令集和上下文:

2.1 ARM 状态

- 指令集: 使用 ARM 指令集(32 位)。

- 指令长度: 每条指令固定为 32 位宽。

- 运行特点: 高性能、特定于计算密集型任务。

2.2 Thumb 状态

- 指令集: 使用 Thumb 指令集(16 位)。

- 指令长度: 每条指令固定为 16 位宽。

- 运行特点: 更高的代码密度,适用于内存受限的环境。

- 状态切换: 通过

BX指令或相关状态位切换。

3. 特权级

Cortex-A 处理器的特权模型定义了访问系统资源的权限,分为以下两种级别:

3.1 特权模式

- 描述: 可访问所有寄存器和系统资源。

- 典型模式: Supervisor、FIQ、IRQ 等。

- 用途: 操作系统内核、异常处理程序。

3.2 非特权模式

- 描述: 受限访问,仅能使用部分寄存器和资源。

- 典型模式: User 模式。

- 用途: 用户态应用程序。

4. 内存模型

Cortex-A 的内存模型通过虚拟地址和物理地址管理内存访问,支持复杂的多任务操作系统。

4.1 虚拟地址与物理地址

- 使用 MMU(Memory Management Unit) 实现虚拟内存管理。

- 操作系统内核通过页表映射虚拟地址到物理地址。

4.2 缓存系统

- L1 缓存: 包括指令缓存和数据缓存,大小通常为 32KB 或 64KB。

- L2 缓存: 提供共享缓存,可选配置,大小为 256KB 到几 MB。

5. 异常和中断模型

Cortex-A 处理器支持多种异常,用于处理运行过程中的错误或特定事件。

5.1 异常类型

- Reset(复位异常): 处理器启动时进入。

- Undefined Instruction(未定义指令异常): 捕获未定义指令。

- Supervisor Call(系统调用异常): 操作系统使用系统调用触发。

- Prefetch Abort(指令预取异常): 指令访问无效地址。

- Data Abort(数据访问异常): 数据访问无效地址。

- IRQ(普通中断): 响应外部设备中断。

- FIQ(快速中断): 响应高优先级中断。

5.2 异常处理流程

- 当前指令执行完成后,自动跳转到异常向量表对应的地址。

- 保存当前状态到特定寄存器(如

SPSR和LR)。 - 处理异常或中断。

- 使用

SUBS PC, LR, #4或MOVS PC, LR返回异常前的状态。

6. TrustZone 安全扩展

Cortex-A 处理器支持 TrustZone 技术,实现安全运行环境。

- 安全状态:

- Secure World(安全世界): 运行敏感任务或数据(如加密密钥)。

- Non-secure World(非安全世界): 运行常规任务。

- 切换方式: 通过

SMC指令或特定异常机制切换。

7. 多核与对称多处理(SMP)

Cortex-A 系列处理器通常支持多核对称处理模式:

- 特点:

- 所有内核共享统一的内存空间。

- 缓存一致性由硬件(如 AMBA 总线)保证。

- 应用:

- 提高任务并行性,适用于多任务操作系统。

ARM Cortex-A 处理器在引入虚拟化扩展(Virtualization Extensions)后增加了 Hyp 模式(Hypervisor Mode)。该模式是为了支持硬件虚拟化而设计的,主要用于运行虚拟机管理程序(Hypervisor)。

8. Hyp 模式简介

Hyp 模式是 ARMv7-A 和 ARMv8 架构的一部分,专为虚拟化需求而设计。它允许处理器直接支持虚拟化,将虚拟机管理程序(hypervisor)置于一个高特权模式下,从而增强性能和安全性。

- ARMv7-A 引入: 从 Cortex-A15 开始支持。

- ARMv8-A 延续: 在 AArch32 和 AArch64 中均提供该模式。

Cortex-A 寄存器组

Cortex-A 处理器的寄存器组分为多个层次,涵盖通用寄存器、控制寄存器、异常模式寄存器等,支持 ARM 处理器的多模式运行、异常处理和虚拟化功能。

1. 总体分类

Cortex-A 的寄存器可以分为以下几类:

| 类别 | 描述 |

|---|---|

| 通用寄存器 | 包括 R0-R15,一般用于数据操作、地址存储和程序计数。 |

| 程序状态寄存器(PSR) | 包括 CPSR 和 SPSR,存储当前和异常模式下的状态信息。 |

| 特殊寄存器 | 包括控制寄存器、调试寄存器、虚拟化寄存器等。 |

| 异常模式寄存器 | 各种异常模式下(如 FIQ、IRQ)的特定寄存器组,用于高效处理异常和中断。 |

| 浮点和 SIMD 寄存器 | 支持浮点运算和向量运算的扩展寄存器组(如 NEON 寄存器)。 |

2. 通用寄存器

通用寄存器用于数据运算和存储操作。ARM 寄存器是 32 位宽,部分寄存器在特定模式下会被重命名或替换。

2.1 通用寄存器分组

| 寄存器名称 | 用途 |

|---|---|

| R0-R12 | 通用寄存器,可用于存储数据或指针。 |

| R13 (SP) | 堆栈指针(Stack Pointer)。 |

| R14 (LR) | 链接寄存器(Link Register),存储子程序返回地址。 |

| R15 (PC) | 程序计数器(Program Counter),指向当前指令地址。 |

2.2 模式相关寄存器

一些寄存器在处理器进入特定模式后会被替换为专用版本。例如:

- R13(SP): 每种模式拥有独立的堆栈指针(SP)。

- R14(LR): 每种模式拥有独立的链接寄存器(LR)。

3. 程序状态寄存器(PSR)

程序状态寄存器用于存储处理器的当前状态信息,包括条件标志、模式设置和中断状态。

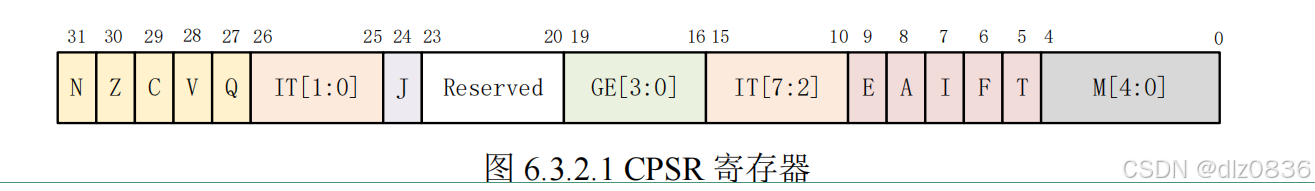

3.1 Current Program Status Register (CPSR)

| 位区间 | 名称 | 描述 |

|---|---|---|

| 31-28 | 条件标志位 | N(负)、Z(零)、C(进位)、V(溢出)。 |

| 27-8 | 保留 | 未定义或特定扩展用途。 |

| 7 | I 位 | 禁止普通中断(IRQ)。 |

| 6 | F 位 | 禁止快速中断(FIQ)。 |

| 5 | T 位 | 表示当前是否运行在 Thumb 状态。 |

| 4-0 | 模式位 | 指示当前运行模式(如 User、Supervisor、FIQ)。 |

3.2 Saved Program Status Register (SPSR)

- 用于保存异常模式进入之前的 CPSR 值。

- 各种异常模式(如 FIQ、IRQ、Abort、Undefined)都有自己的 SPSR。

4. 特殊寄存器

特殊寄存器提供处理器的控制和状态功能,常用于系统初始化、调试和虚拟化。

| 寄存器名称 | 描述 |

|---|---|

| SCR | 安全配置寄存器(Secure Configuration Register),控制安全模式和非安全模式切换。 |

| TTBR0/TTBR1 | 页表基地址寄存器(Translation Table Base Registers),用于内存管理单元(MMU)。 |

| DACR | 域访问控制寄存器(Domain Access Control Register),控制内存域的访问权限。 |

| VBAR | 向量基址寄存器(Vector Base Address Register),存储异常向量表的起始地址。 |

| HCR | Hyp 配置寄存器(Hypervisor Configuration Register),用于管理虚拟化操作。 |

5. 异常模式寄存器

为了提高异常处理效率,Cortex-A 为每种异常模式分配了专用的寄存器组,避免在模式切换时保存和恢复通用寄存器的开销。

| 寄存器 | 描述 |

|---|---|

| R13_sp_mode | 各模式独立的堆栈指针。 |

| R14_lr_mode | 各模式独立的链接寄存器,保存异常返回地址。 |

| SPSR_mode | 各模式独立的保存程序状态寄存器,记录异常进入时的 CPSR 值。 |

6. 浮点与 SIMD 寄存器

Cortex-A 处理器支持 NEON 技术和浮点运算,通过一组扩展寄存器实现高性能的数学运算和多媒体处理。

| 寄存器名称 | 描述 |

|---|---|

| D0-D31 | 双精度浮点寄存器,也可作为 32 个单精度浮点寄存器(S0-S31)。 |

| Q0-Q15 | 128 位向量寄存器,用于 SIMD 运算。 |

| FPSCR | 浮点状态和控制寄存器,存储浮点运算的状态(如异常标志)。 |

7. Cortex-A 的虚拟化寄存器

在支持虚拟化的处理器上,Hyp 模式引入了专用寄存器,用于管理虚拟机和异常处理。

| 寄存器名称 | 描述 |

|---|---|

| HCR | Hyp 配置寄存器,控制虚拟化功能。 |

| HSR | Hyp Syndrome 寄存器,记录虚拟化异常的具体信息。 |

| HTTBR | Hyp Translation Table Base Register,存储虚拟机管理程序的页表基地址。 |

总结

Cortex-A 的寄存器组设计灵活、高效,既支持普通应用程序运行所需的通用寄存器,又提供了异常处理、虚拟化和浮点运算的专用寄存器。根据应用场景的不同,可以高效地利用这些寄存器满足性能和功能需求。

进一步了解通用寄存器

在 ARM Cortex-A 处理器中,通用寄存器(R0-R15)的设计体现了灵活性和高效性,通过划分为 未备份寄存器、备份寄存器和程序计数器,满足了不同的功能需求。以下是对这些寄存器的详细探讨:

1. 未备份寄存器(R0~R7)

1.1 定义与特性

- 未备份寄存器是 R0 至 R7,共 8 个寄存器。

- 它们在模式切换时不会自动保存或恢复,需要在程序中手动管理。

1.2 主要用途

- 函数参数传递:

- 在 ARM 的 AAPCS(ARM Architecture Procedure Call Standard) 调用约定中,R0~R3 用于传递函数参数。

- 超过 4 个参数时,额外参数通过堆栈传递。

- 函数返回值:

- R0 通常用于存储函数返回值(整数或指针类型)。

- 临时数据存储:

- 用作临时变量的存储位置,方便快速访问和操作。

1.3 使用注意

- 由于 R0~R7 的值可能会被函数调用或中断破坏,因此调用者(caller)需在需要时备份这些寄存器。

2. 备份寄存器(R8~R14)

2.1 定义与特性

- 备份寄存器是 R8 至 R14,共 7 个寄存器。

- 它们在特权模式(如 FIQ、IRQ、Supervisor)下会有独立的备份版本,避免与其他模式共享,从而提高异常处理效率。

2.2 特殊用途

-

R13(堆栈指针,SP):

- 用于指向当前栈顶,管理函数调用和局部变量。

- 每种模式有独立的堆栈指针(如

R13_svc、R13_irq等)。

-

R14(链接寄存器,LR):

- 保存函数或异常返回地址。

- 在子程序调用时,LR 会自动存储返回地址,函数结束时可通过

MOV PC, LR返回。

2.3 异常模式下的备份

- 在异常模式(如 IRQ 和 FIQ)下,R8~R14 会切换为专用寄存器,避免与普通模式共享,提高异常处理速度:

- FIQ 模式: 备份寄存器扩展至 R8~R14,用于快速上下文切换。

- IRQ 模式: 通常只使用独立的 R13 和 R14。

2.4 使用注意

- 备份寄存器的值在异常模式之间是隔离的,不需要手动保存。

- 在普通模式下,R8~R12 由被调用者(callee)负责保存。

3. 程序计数器(R15 / PC)

3.1 定义与特性

- R15 / PC(Program Counter) 用于存储当前执行指令的地址。

- PC 是 32 位宽,但在 ARM 状态和 Thumb 状态下的行为有所不同:

- ARM 状态: 指向当前指令的地址 + 8 字节(预取队列的偏移)。

- Thumb 状态: 指向当前指令的地址 + 4 字节(预取队列的偏移)。

3.2 特殊用途

-

控制程序流:

- 通过修改 PC,可以实现跳转(

B指令)或函数调用(BL指令)。

- 通过修改 PC,可以实现跳转(

-

异常处理:

- 异常发生时,PC 的值会被保存到对应模式的 LR 中,便于返回异常发生点。

-

分支和跳转:

- PC 在许多指令中可以作为目标寄存器,直接修改程序的执行地址。

3.3 使用注意

- 修改 PC 时需确保地址对齐:

- ARM 状态:地址需为 4 字节对齐。

- Thumb 状态:地址需为 2 字节对齐。

- 预取队列偏移需要考虑,避免错误的计算和跳转。

4. 总结对比

| 类型 | 寄存器范围 | 主要作用 | 管理方式 |

|---|---|---|---|

| 未备份寄存器 | R0~R7 | 函数参数传递、返回值存储、临时数据存储 | 需调用者(caller)手动备份。 |

| 备份寄存器 | R8~R14 | 存储局部变量、函数返回地址,支持异常模式切换。 | 异常模式独立,普通模式需被调用者(callee)备份。 |

| 程序计数器(PC) | R15 | 存储当前指令地址,控制程序流和异常返回。 | 自动管理,但需注意对齐和预取偏移。 |

4294

4294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?