名称:串行和并行转换器的开发设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

设计项目

该项目将涉及VHDL中并行到串行和串行到并行转换器的开发和仿真。数字系统通常获取并行字节的数据,并通过单根导线传输它们,以节省导线面积,减少串扰效应,提高时钟速度或保持设备之间的兼容性。该练习将介绍组件实例化以及在单个项目中使用多个VHDL模块文件。在VHDL中设计复杂的系统时,优良作法是将系统的功能块分布在多个VHDL模块上,从而增加了代码的易用性和功能性。

整个系统的原理图如图1所示。首先,该图的VHDL模块,实体,组件,端口和信号可能会令人困惑,因此在开始练习之前了解层次结构非常重要。在本实验中,我们将使用计数器,串行化转换器和反序列化转换器。计数器用于控制在串行线上放置数据或从串行线上删除数据的速率和时间,它将成为串行化实体的组成部分。为了实现这一目标,您应该完成以下任务序列:

1.创建一个新的Quartus Prime项目,并将其命名为Lab_1。首先,我们将创建一个4位计数器,该计数器将用作序列化和反序列化模块的计时器。将新的VHDL文件添加到项目。将此模块计数器命名。如有必要,请参考上一个实验室的指导。创建一个测试平台以检查代码的功能

2.确定计数器工作正常后,以与创建计数器相同的方式创建一个名为parallelToSerial的新VHDL模块。在此模块中,我们将这个实体设计为采用8位并行输入信号并将其转换为串行输出格式,以便每个位将在8个时钟周期内通过1位宽的输出线传输。为了给传输计时,我们将使用之前创建的计数器模块。 parallelToSerial模块应具有一个8位输入端口,一个clk输入和一个std_logic串行输出

3.为了整理并行到串行转换所需的时序,可以在此模块中实例化第1部分中创建的计数器。在这段代码中,我们通过定义不同的二进制模式并使用case语句在状态之间进行切换来有效地创建状态机。鉴于计数器模块具有16种可能的状态,并且在其计数端口上按顺序递增计数,因此我们可以在每个二进制计数的不同情况之间切换。例如:

state 1, “0001”:我们取第一个并行位input_port(0)并将其放置在串行输出端口output_port上。

state 2, “0010”:我们将第二个并行位input_port(1),在输出上等等

4.一旦创建了转换代码,就生成一个测试平台,将并行输入端口加载为字节“ 01010101”作为激励,并且没有初始延迟,以确保代码正常工作并在8个周期内观察串行输出。

5.最后一步是通过添加一个称为serialToParallel的新VHDL模块来创建反序列化模块。这将与parallelToSerial模块几乎相同,不同的是,您将在计数器信号提供的每个顺序case语句中,将串行输入线上的当前位值分配给不同的并行输出位。为防止输出端口显示不完整的数据,应定义一个单独的信号,以便在分配了8位之后将并行输出信号加载到物理输出端口。生成VHDL模块后,复制行为并行描述可能是一个好的开始。在仿真中验证您的设计。创建一个测试平台,并按如下所示加载串行输入线:

Process begin

wait until clk_input = '1'; wait for clk_period;

data_input <= ‘0’; wait for clk_period;;

data_input <= ‘0’; wait for clk_period;

data_input <= ‘0’; wait for clk_period;

data_input <= ‘0’; wait for clk_period;

data_input <= ‘0’; wait for clk_period;

data_input <= ‘1’; end process;

6.现在,您的项目中具有单独的测试平台,其中包括序列化,反序列化和计数器模块。下一步是创建另一个称为Combination的VHDL模块,它将连接您创建的两个序列化模块。这

样,您可以创建一个测试平台,该测试平台将加载模块组合的8位并行输入并将其传输到parallelToSerial模块的输入。数据包将被序列化,然后根据连接到serialToParallel模块的信号发送出去。该数据包将重新创建为并行信号,并在Combination模块的8位输出端口上发送出去,如图1所示。

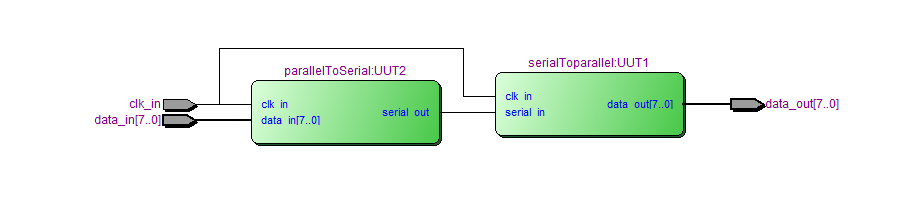

图1.在一个名为Combination的VHDL模块中,将串行到并行和并行到串行模块组合在一起。

Combination模块需要一个公共的clk端口以及一个8位输入和8位输出并行端口。实例化parallelToSerial和serialToParallel模块。然后,您只需要创建将Combination模块的输入连接到parallelToSerial模块的输入,将该模块的输出连接到serialToParallel模块的输入,最后将该模块的输出连接到组合的输出端口的信号。

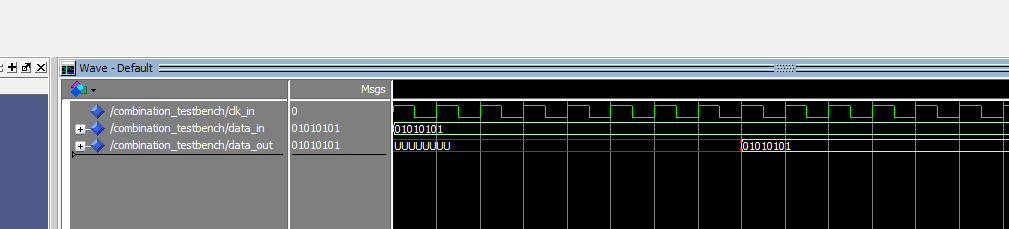

7.完成后,为组合模块创建测试台,只需为输入端口提供“ 01010101”,然后在8个周期后应观察到相同的输出。

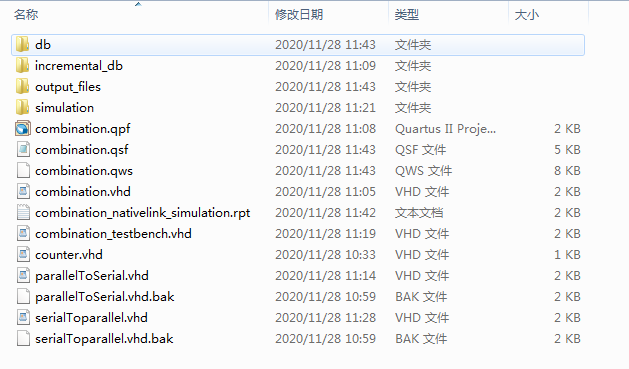

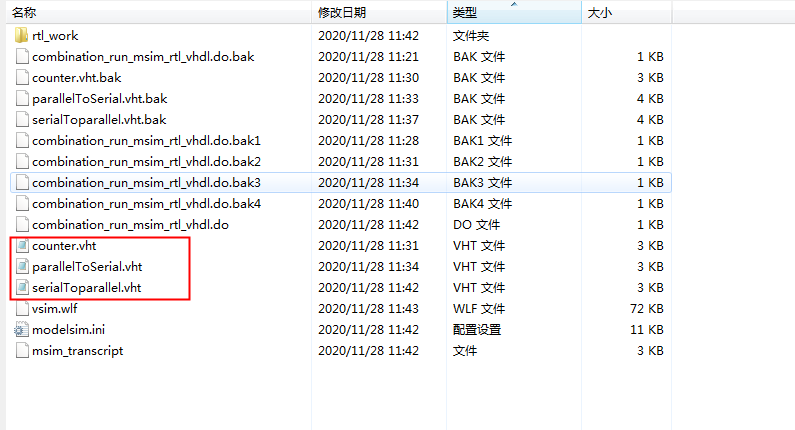

1. 工程文件

2. 程序文件

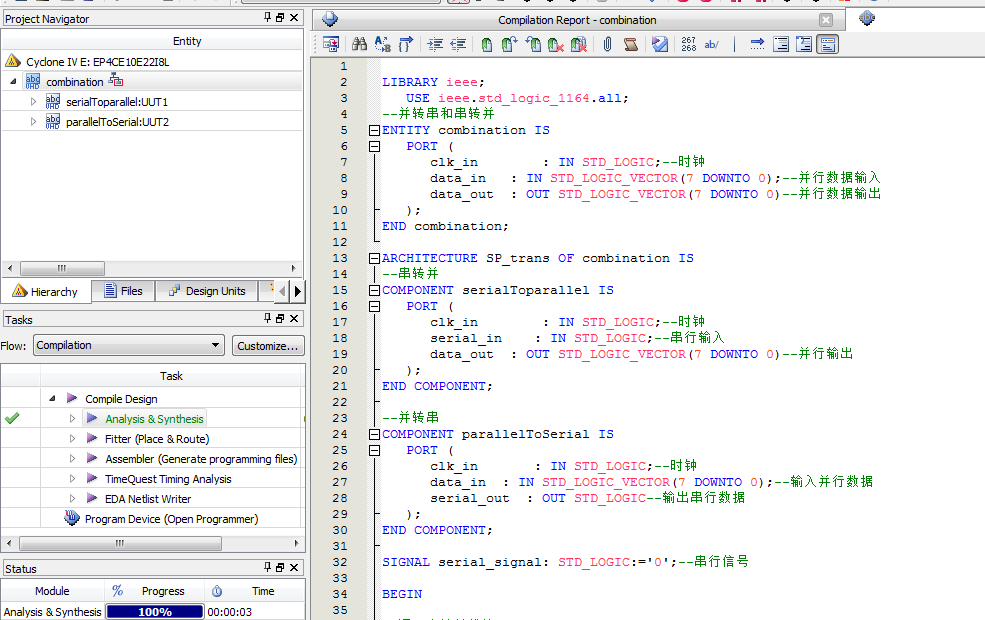

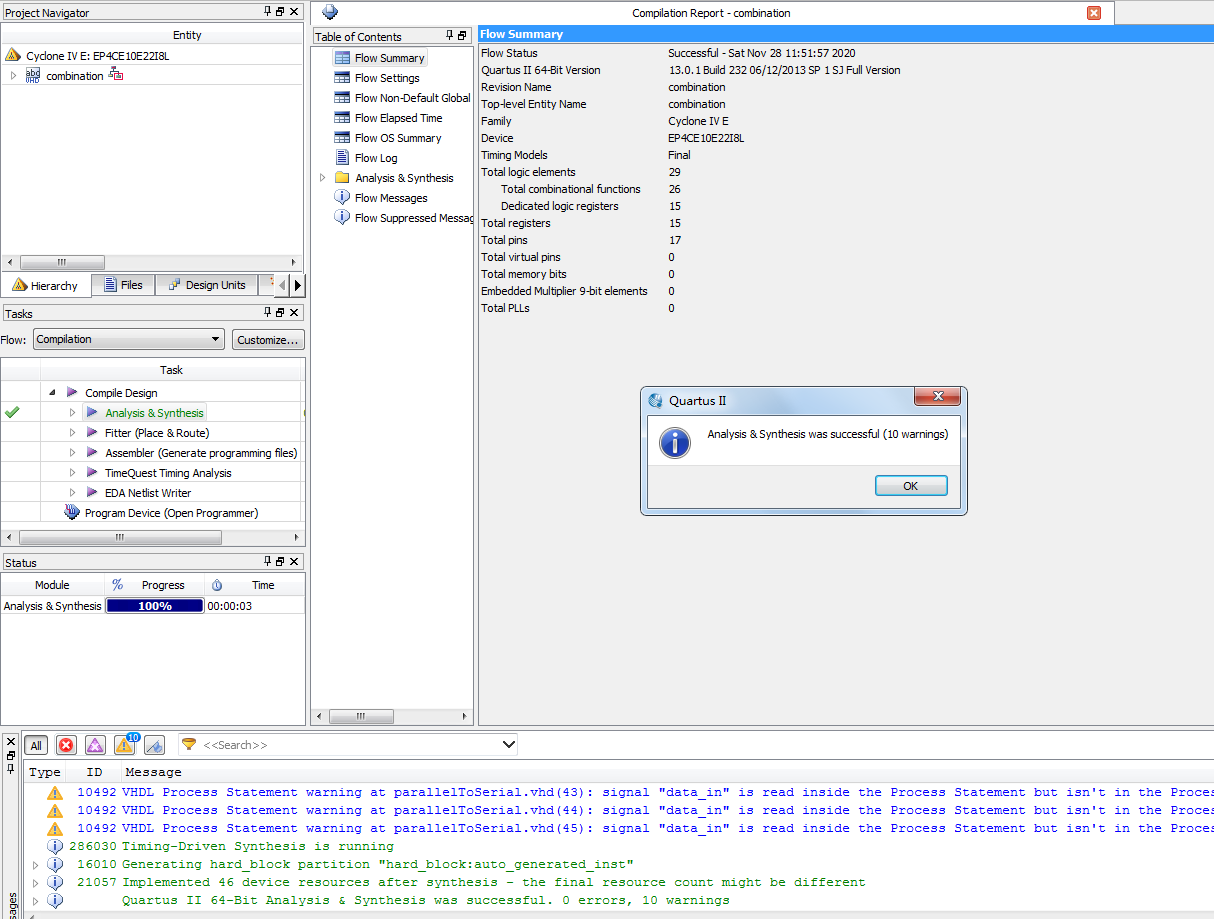

3. 程序编译

4. RTL图

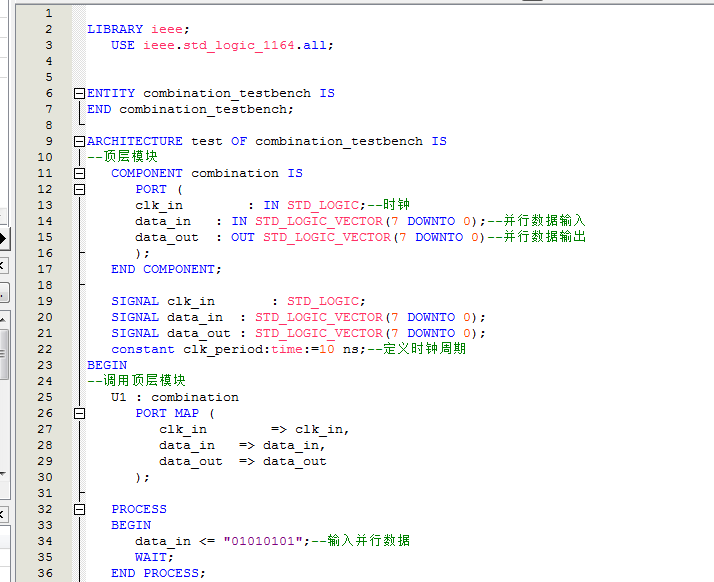

5. Testbench

6. 仿真图

整体仿真图

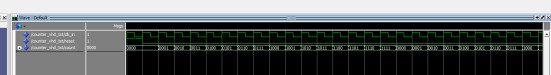

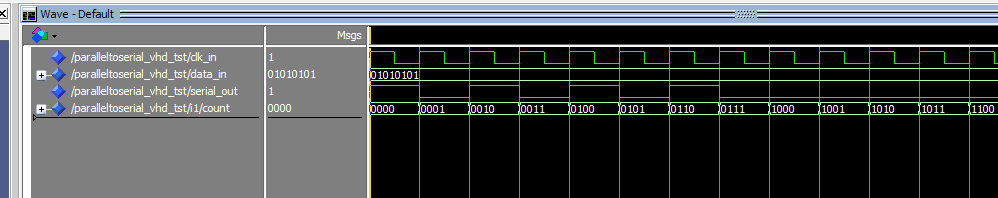

Count仿真图

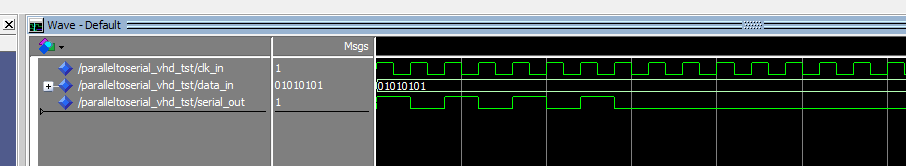

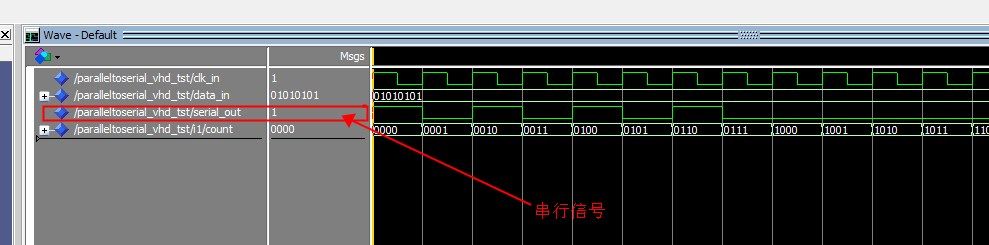

parallelToSerial仿真图

serialToparallel仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --并转串和串转并 ENTITY combination IS PORT ( clk_in : IN STD_LOGIC;--时钟 data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--并行数据输入 data_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--并行数据输出 ); END combination; ARCHITECTURE SP_trans OF combination IS --串转并 COMPONENT serialToparallel IS PORT ( clk_in : IN STD_LOGIC;--时钟 serial_in : IN STD_LOGIC;--串行输入 data_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--并行输出 ); END COMPONENT; --并转串 COMPONENT parallelToSerial IS PORT ( clk_in : IN STD_LOGIC;--时钟 data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--输入并行数据 serial_out : OUT STD_LOGIC--输出串行数据 ); END COMPONENT; SIGNAL serial_signal: STD_LOGIC:='0';--串行信号 BEGIN --调用串转并模块 UUT1: serialToparallel PORT MAP ( clk_in => clk_in, data_out => data_out, serial_in => serial_signal--串行信号 );

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?