1.2 LD-FAM

1.2.1 MLD

1.2.1.1 MLD简介

- MLD 的资源划分与设备类型:type3 型多逻辑设备(MLD)可将资源划分为最多 16 个隔离的逻辑设备(LD),每个 LD 通过 LD-ID 在 CXL.io 和 CXL.mem 协议中识别。对虚拟层级(VH)可见的每个 LD 都作为 3 型设备运行,且 LD-ID 对访问 VH 的软件透明。由于 LD-ID 功能仅存在于上述两种协议中,MLD 仅限于 3 型设备。

- LD 的分配与 FM 的作用:MLD 有一个 LD 预留给管理器(FM),最多 15 个 LD 可供主机绑定。FM 拥有的 LD(FMLD)可让 FM 配置跨 LD 的资源分配,并管理与多个虚拟 CXL 交换机(VCS)共享的物理链路,其总线主控能力仅限于生成错误消息,且这些消息只能路由给 FM。

- MLD DVSEC 与 LD-ID:MLD 组件包含一个仅 FM 可访问的 MLD DVSEC,可通过在 CXL LD-ID TLP 前缀中携带 LD-ID 为 FFFFh 的请求进行寻址。交换机必须保证只有 FM 能使用 FFFFh 这个 LD-ID。

- LD 的配置方式:MLD 组件可使用 FM API 配置 LD 或采用静态配置。在这两种配置中,已配置的 LD 资源分配都通过 MLD DVSEC 公布。此外,FMLD 的 MLD DVSEC LD-ID 热复位向量寄存器也可被 CXL 交换机用于触发一个或多个 LD 的热复位,详情见 8.1.10.2 节。

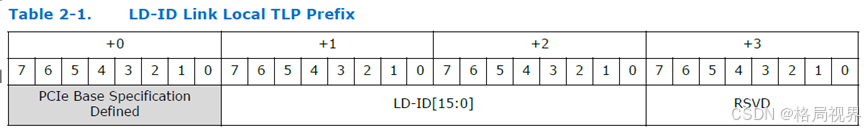

1.2.1.2 CXL.io 和 CXL.mem 中的 LD-ID

- LD-ID 概述:LD-ID 是一个 16 位的逻辑设备标识符,适用于 CXL.io 和 CXL.mem 的请求和响应。所有针对多逻辑设备(MLD)的请求以及 MLD 返回的响应都必须包含 LD-ID。关于在 CXL.mem 报头格式中携带 LD-ID 字段的内容,可参考 3.3.5 节和 3.3.6 节。

- CXL.mem 中的 LD-ID:CXL.mem 仅支持 LD-ID 的低 4 位,因此在链路上最多可支持 16 个唯一的 LD-ID 值。通过 MLD 端口转发的请求和响应都带有 LD-ID 标签。

- CXL.io 中的 LD-ID:

- CXL.io 支持在通过 MLD 端口转发的所有请求和响应中携带 16 位的 LD-ID。其中,LD-ID 为 FFFFh 是保留值,始终由固件管理器(FM)使用。

- CXL.io 利用供应商定义的本地事务层数据包(TLP)前缀来携带 16 位的 LD-ID 值。供应商定义的本地 TLP 前缀格式使用 VendPrefixL0 本地 TLP 前缀类型。

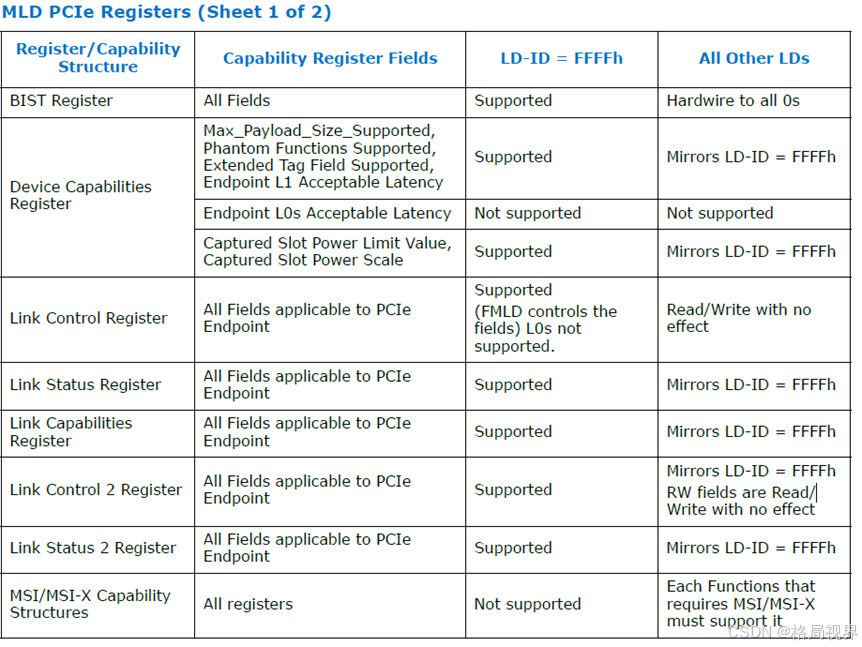

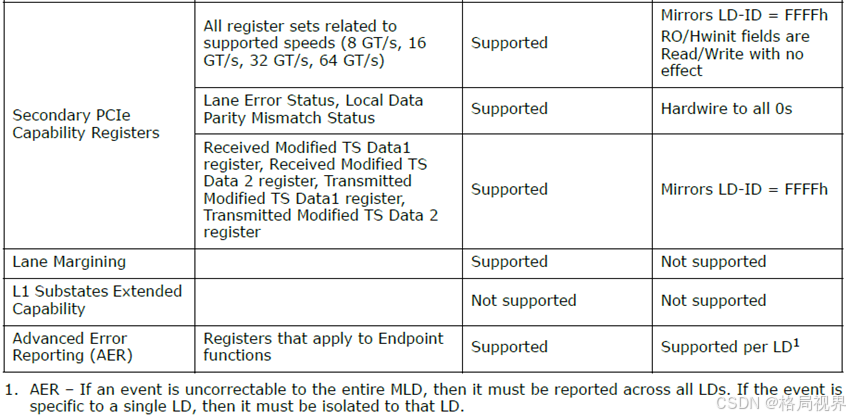

1.2.1.3 池化内存设备配置寄存器

- LD 与软件的关系及配置寄存器基础:每个逻辑设备(LD)对于软件而言表现为一个或多个 PCIe 端点(EP)功能。虽然 LD 功能支持所有的配置寄存器,但一些影响通用链路行为的控制寄存器是虚拟化的,并且对链路没有直接影响。每个 LD 的功能都必须按照 PCIe 基本规范中所描述的那样实现配置寄存器。除非另有规定,配置寄存器的作用范围如 PCIe 基本规范中所述。例如,命令寄存器中的内存空间启用(MSE)位控制着一个功能对内存空间的响应。

- 与 PCIe 基本规范有差异的寄存器字段:表 2-2 列出了与 PCIe 基本规范相比,行为有所修改的一组寄存器字段。

1.2.2 池化内存和共享 FAM

- FAM 的分类及定义:从支持多个主机的设备中暴露出来的主机管理设备内存(HDM)被称为Fabric-Attached Memory(FAM)。通过逻辑设备(LDs)暴露的 FAM 称为 LD-FAM;使用基于端口的路由(PBR)链路以更具扩展性的方式暴露的 FAM 称为全局 FAM(G-FAM)。

- 每个 HDM 区域专用于单个主机接口的 FAM 被称为 “池化内存” 或 “池化 FAM”。

- 多个主机接口被配置为可同时访问单个 HDM 区域的 FAM 被称为 “共享 FAM”,并且不同的共享 FAM 区域可以被配置为支持不同的主机接口集。

- LD-FAM 的设备变体:

- 多逻辑设备(MLD)通过单个共享链路暴露多个 LD。

- 多头单逻辑设备(MH-SLD)暴露多个 LD,每个 LD 都有专用链路。

- 多头 MLD(MH-MLD)包含多个链路,其中每个链路支持 MLD 或 SLD 操作(可选择配置),并且至少有一个链路支持 MLD 操作。更多详细信息请参阅 2.5 节 “多头设备”。

- G-FAM 设备(GFD):当前,G-FAM 设备的架构包含一个或多个支持多个主机 / 对等接口的链路,传入的 CXL.mem 或 UIO 请求的主机接口由 PBR 消息中包含的源 PBR ID(SPID)字段确定(更多详细信息请参阅 7.7.2 节)。

- 区分设备类型:MH-SLD 和 MH-MLD 应与任意的多端口 3 型组件(如 9.11.7.2 节中所述的那些)区分开来,后者在单个操作系统域中支持多 CPU 拓扑结构。

1.2.3 共享 FAM 的一致性模型

- 一致性模型的指定:每个共享的 HDM-DB(主机管理设备内存 - 设备内存块)区域的一致性模型由固件管理器(FM)指定,分为多主机硬件一致性模型或软件管理一致性模型。

- 多主机硬件一致性模型

- 硬件跟踪要求:多主机硬件一致性要求 MLD(多逻辑设备)硬件根据其特定的实现跟踪机制,在一定程度上跟踪每个缓存行的主机一致性状态(如表格 3-37 所定义),该机制通常可分为嗅探过滤器或全目录类型。

- 原子操作执行:每个主机可以通过获取对一个缓存行的独占访问权,在其缓存内对该缓存行执行其指令集架构(ISA)所支持的任意原子操作。数据通过缓存一致性在全局范围内可见,并遵循正常的硬件缓存逐出流程。

- 内存写操作要求:对该内存区域的 MemWr(内存写)命令必须将 SnpType(嗅探类型)字段设置为 No-Op(无操作)以防止死锁。这要求主机在发出 MemWr 命令之前必须使用 M2S(主设备到从设备)请求通道获取所有权,从而导致完成一次写入需要两个阶段(与未共享且分配给单个主机根端口、可使用单阶段可嗅探写入的 HDM-DB 区域相比)。

- 软件管理一致性模型

- 硬件跟踪情况:软件管理一致性不需要 MLD 硬件跟踪主机一致性状态。

- 软件协调机制:相反,每个主机上的软件使用特定于软件的机制来协调每个缓存行的软件所有权。软件可以选择依靠其他 HDM 区域中的多主机硬件一致性来协调软件管理一致性 HDM 区域中缓存行的软件所有权。其他用于软件协调缓存行所有权的机制超出了本规范的范围。

- 共享 FAM 对主机的内存暴露形式:共享 FAM 也可以将内存作为简单的 HDM-H(主机管理设备内存 - 主机)暴露给主机,但这仅支持主机之间的软件一致性模型。

- 实现说明

- 软件管理一致性的依赖条件与潜在问题

- 依赖机制:软件管理一致性依赖于软件具备使缓存层次结构无效和 / 或刷新的机制,并且依赖缓存代理仅在本地软件对缓存行进行显式修改时才发出写回操作。

- 性能优化与预取问题:为了进行性能优化,许多处理器会在软件无法直接控制预取算法的情况下预取数据。由于各种特定实现原因,一些缓存代理可能会自发地写回那些由硬件预取但从未被本地软件修改过的干净缓存行(例如,在没有执行存储指令的情况下将缓存行从独占状态(E)提升为修改状态(M))。任何主机或设备中仅打算读取某缓存行的缓存代理对该缓存行的干净写回操作,都可能覆盖其他已对该缓存行执行写入操作的主机或设备所做的更新,从而破坏软件管理的一致性。需注意,由零长度写事务导致的写回操作不被视为干净写回。另外,主机和 / 或设备的内部缓存行大小可能大于 64 字节,一次写回操作可能需要多次 CXL 写入才能完成。如果这些 CXL 写入操作中包含软件修改过的数据,则该写回操作不被视为干净写回。

- 解决干净写回问题的能力位

- 能力位设置位置:在 CXL 系统描述结构(CSDS,见 9.18.1.6 节)中为主机提供了一个 “无干净写回(No Clean Writebacks)” 能力位,在 DVSEC CXL 能力 2 寄存器(见 8.1.3.7 节)中为设备提供了该能力位。如果缓存代理保证永远不会产生干净写回操作,则可设置该位。

- 向后兼容性与结果可靠性:出于向后兼容性考虑,该位被清零并不一定意味着任何相关的缓存代理会产生干净写回操作。当为所有可能访问共享 FAM 范围的缓存代理都设置了该位时,针对该范围的软件管理一致性协议能够提供可靠的结果。对于硬件一致性内存范围,软件应忽略该位。

3480

3480

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?