基于0.18微米CMOS工艺的累积模式BDJ APS像素电路设计

摘要

本文提出了一种用于X‐FAB XH018 CMOS工艺中BDJ光电探测器的有源像素传感器(APS)结构。该像素架构将用于设计BDJ有源像素的矩阵阵列,以开发芯片实验室酶联免疫吸附测定(ELISA)。提出了一种解决BDJ结构中电容不平衡问题的方案,可实现对埋入式双PN结光电流的简便且精确的测量。已进行噪声分析,本设计将跟随器噪声降低至60μVrms。所设计的BDJ有源像素在100微米×100微米的有源区下具有61%的填充因子。

关键词

芯片实验室,酶联免疫吸附测定,有源像素传感器,埋层结,光电二极管

I. 引言

随着人口老龄化和冠状病毒(COVID19)等传染病的演变,开发用于即时检测或家庭先进诊断的创新设备以及预防方法[1]变得尤为紧迫。将即时检测测试(POCT)或快速诊断测试(RDT)作为一线紧急诊断工具,可对重症病例实现及时治疗实施,并迅速落实预防措施,以中断和阻止污染及疾病传播。

文献中报道的大部分系统采用光学方法,并依赖比色ELISA格式来检测蛋白质或生物制剂[1],[2]。单克隆抗体(mAb)和新型标记技术的应用,以及传感器和测量系统领域的进展,使得在2毫米光程下可达到约0.5 10^-12 mol/l(0.5pM)的检测限(LOD)[2]。然而,这些系统中大多使用常规光电探测器(光电二极管、光敏电阻、电荷耦合器件),并且需要空白测量进行校准,从而产生不确定性,影响其测量精度。

我们开发了一种测量方法,可提高诊断设备的检测限(LOD)。利用埋入式双PN结(BDJ)作为光电探测器,并结合该测量方法,我们在仅1 mm的光程下实现了100飞摩尔的检测限。该方法无需空白测量即可完成校准。我们研究项目的总体目标是设计一种由BDJ光电探测器矩阵阵列和简单微流控系统组成的芯片实验室传感器,以显著提升诊断系统的性能。该BDJ矩阵阵列需具备足够精度,以实现100飞摩尔的检测限。

积累模式(电荷积分)有源像素传感器(APS)读出架构在灵敏度、填充因子和噪声之间具有良好的折衷。但此类架构在与BDJ结合使用时面临挑战,因为两个光电探测器电容之间的不平衡。这一挑战在亚微米技术中尤为突出。本文重点研究在0.18微米CMOS工艺下设计一种电荷积分APS架构,以解决该问题,并实现对BDJ光电流的高精度读出电路。

II. 像素电路设计

A. 光电探测器描述

BDJ光电探测器结构由两个PN结光电二极管垂直堆叠而成,共用一个阴极。在标准CMOS工艺中,第一个结(浅结D1)形成于P区(例如P+扩散区)与N阱之间;第二个结(深结D2)形成于N阱与P衬底[3],[4],[5]之间。

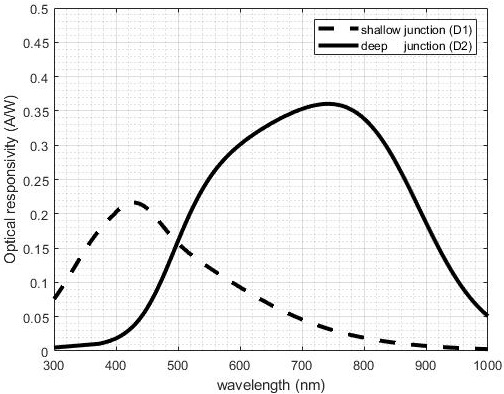

在光照下且两个光电二极管处于反向偏置时,D1在阳极1(A1)产生光电流I1,D2在阳极2(A2)产生光电流I2。阴极(C)中的电流是这两个光电流之和(I1+I2)。两个堆叠的光电二极管分别通过施加到D1和D2的电位V1和V2, 进行反向偏置。BDJ器件的工作原理基于硅吸收系数对波长的强烈依赖性。浅结吸收300纳米至550纳米之间的最短波长,而位于较深位置的第二个结吸收500纳米至900纳米之间的波长。光谱响应如图2所示。

在此工作中,我们希望在XH018技术中实现我们的BDJ APS架构。该技术提供了BDJ的参数化结构。根据我们微流控系统的尺寸限制,BDJ的有源区尺寸为100μm×100μm。由于存在阱连接器,该BDJ单独的填充因子并非100%。BDJ的特性如表I所示。

表I BDJ 特性

| 描述 | 值 |

|---|---|

| 有源区长度 | 100μm |

| 有源区宽度 | 100μm |

| 结电容1 | 6.91pF |

| 漏电流1 | 342飞安 |

| 结电容2 | 0.67皮法 |

| 漏电流2 | 153飞安 |

| 填充因子 | 85.71% |

B. 像素原理图描述与分析

文献中已报道了多种用于读取CMOS图像传感器中光电二极管产生的光电流的读出架构,包括无源像素传感器(PPS)、有源像素传感器(3T或4T APS)、对数型以及数字像素传感器(DPS)[6],[7]。

很少有架构被提出用于读取埋层结光电探测器的光电流[8],[9]。累积模式下的BDJ APS在每个像素中使用两个3T结构。第一个将光电流积分到D1的电容上,第二个将光电流积分到D2的电容上。主要挑战在于光电二极管共享同一个阴极。

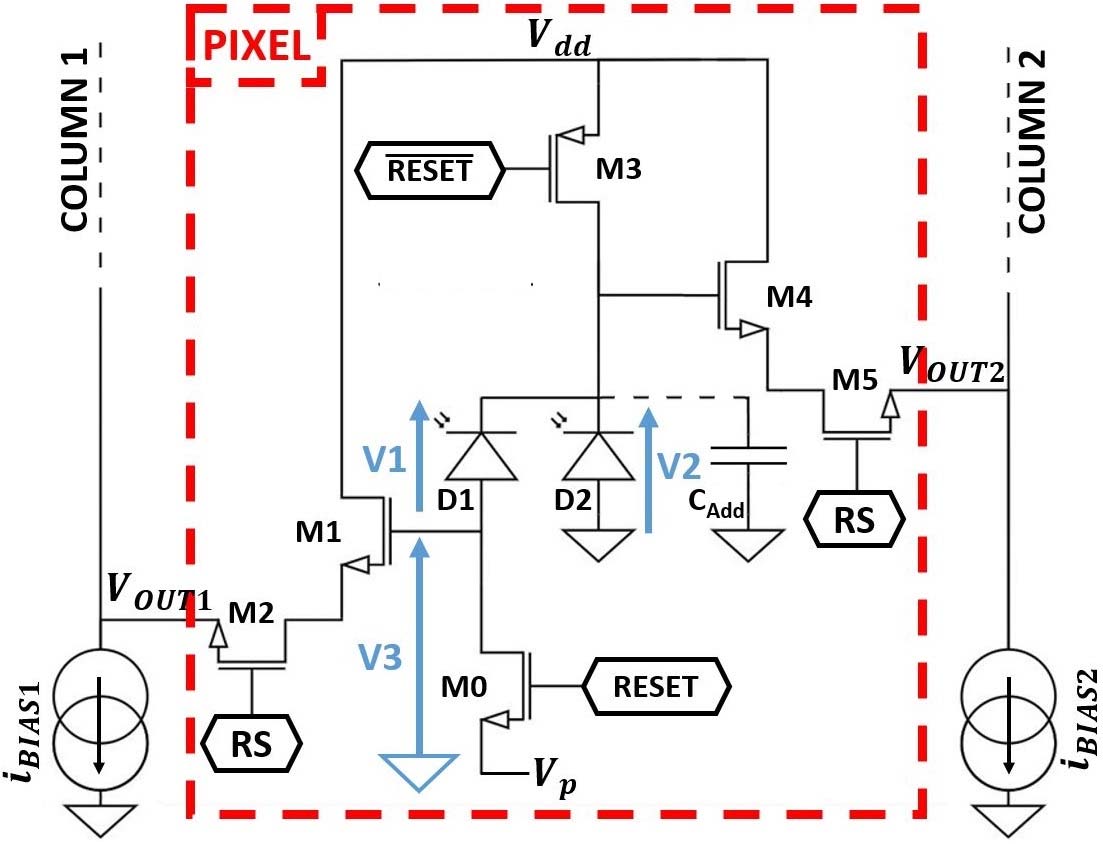

本研究中所采用的像素结构如图3所示。我们使用了两个3T电荷积分APS电路来读取BDJ光电二极管产生的光电流。因此,每个像素需要六个晶体管。在复位阶段,晶体管M0和M3用于将光电二极管D1和D2分别设置为反向偏置(Vdd - Vp)和Vdd。此时,BDJ的两个电容Cj1和Cj2分别充电至(Vdd - Vp)和Vdd。在电荷积分阶段(复位阶段之后),光电流I1将使浅层电容Cj1放电,而I2将使深层结电容Cj2放电。M1和M4是源极跟随器,用于提供高输入阻抗,从而避免BDJ光电二极管与读出电路之间出现电压衰减。源极跟随器是一种简单的NMOS晶体管,采用共漏极连接方式,具有高输入阻抗、极低输出阻抗以及增益接近于1的特点。M2和M5用于行选择。

在电荷积分阶段,我们计算浅层结和深层结上的偏置电压V1(t)和V2(t),以及源极跟随器M1输入端的电压V3(t)。V1(t)和V2(t)由公式(1)和(2)给出。V3(t)由公式(3)给出。

$$ V1(t) = Vdd - Vp - \frac{I1}{Cj1} \times t $$ (1)

$$ V2(t) = Vdd - \frac{I2}{Cj2} \times t $$ (2)

$$ V3(t) = V2(t) - V1(t) = Vp - \left(\frac{I2}{Cj2} - \frac{I1}{Cj1}\right) \times t $$ (3)

转换增益定义为元电荷与电容值的比值。浅层光电二极管的转换增益为23 nV/e⁻,而深层光电二极管的转换增益为240 nV/e⁻。这种转换增益上的巨大差异对准确测量浅结中产生的光电流构成了主要障碍。实际上,由I2引起的电压变化在V3中起着控制作用。

假设这些电流的值相近,深层结端子处的电压V2将比浅层结端子处的电压V1下降得更快。实际上,V1(t)的斜率与I1/Cj1成正比,低于与I2/Cj2成正比的V2(t)的斜率。两个跟随器栅极输入端的电压分别为V2和V3。由于V3(t=0)的初始电压等于Vp,在放电阶段该值低于Vdd。对于值相近的电流I1和I2,I1/Cj1比I2/Cj2低十倍。因此,电压V2和V3的斜率非常相似,且与I2/Cj2成正比。测量电流I1存在困难。此外,V3比V2更快归零。

a) 提出的解决方案

我们建议将一个附加电容与深层光电二极管并联连接,以平衡电容。尽管该方案较为基础,但它提供了一种简单的方法,可使两个BDJ二极管具有相同的转换增益,并有助于光电流的测量。然而,其实现需要仔细设计电容器面积,以优化像素填充因子。附加电容C_add如图3所示,其值等于两个电容C_add = 6之间的差值,为24 pF。

结的电容新值将为6.91 皮法,我们将其记为Cj。转换增益也将被均衡。因此,阴极电压和阳极1电压由公式(4)和(5)给出。

$$ V2(t) = Vdd - \frac{I2}{Cj} \times t $$ (4)

$$ V3(t) = Vp - \frac{(I2 - I1)}{Cj} \times t $$ (5)

Vp 的值固定在 Vdd/2。因此,我们可以在晶体管M1的输入端测量两个电流之间的差值。

C. 噪声分析

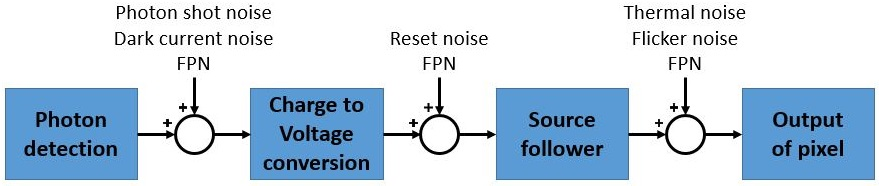

为了提高信噪比SNR,我们进行了噪声分析。在像素中,存在两种类型的噪声。第一种是时间噪声,由光子散粒噪声、暗电流噪声、复位噪声、热噪声和闪烁噪声组成。由于这些噪声源相互独立,总的时间噪声功率等于各个噪声源的噪声功率之和。第二种是空间噪声,即固定模式噪声(FPN)。图4显示了描述噪声源及其在APS结构中位置的模型。

在这项工作中,我们试图通过减小源极跟随器噪声的尺寸来降低热噪声和闪烁噪声,因为该晶体管是噪声较大的一个[10]。

源极跟随器的噪声功率谱密度(PSD)表达式如公式(6)和公式(7)所示。

$$ SV_{FLICKER}(f) = \frac{KF}{COX \times W \times L \times f} \quad [ V²rms/Hz] $$ (6)

其中KF是闪烁噪声系数,COX是氧化层电容,f 是频率。

$$ SV_{THERMAL}(f) = \frac{4 \times k \times T \times \gamma}{GM} \quad [ V²rms/Hz] $$ (7)

其中k是玻尔兹曼常数,γ为长沟道情况下推导出的系数,其值为2/3,T是绝对温度,Gm是晶体管的跨导。

由公式(6)可知,当我们的源极跟随器的W×L较大时,闪烁噪声较低。

由公式(7)可知,跨导随W与L之比的增加而增加,因此热噪声随L与W之比的变化而变化。为了获得最低噪声,应使用最小的L和最大的W,以实现尽可能低的噪声。

因此很明显,为了获得最低的噪声,我们必须使W×L和W/L都非常大。然而,这会降低填充因子。因此,我们在噪声和填充因子之间进行权衡,选择了180纳米的L和10微米的W。偏置电流选择为1μA。

III. 仿真与版图

A. 仿真

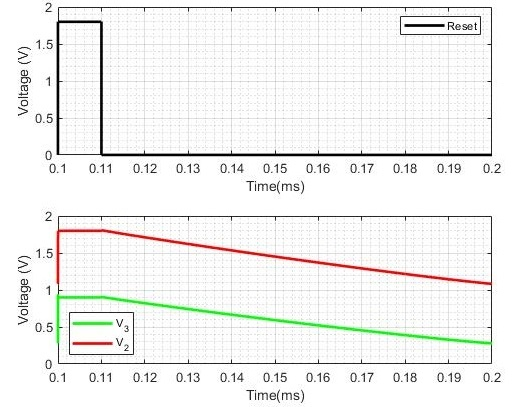

第一次仿真是瞬态仿真,旨在突出电容不平衡的问题。BDJ为每个光电二极管产生相同的电流。

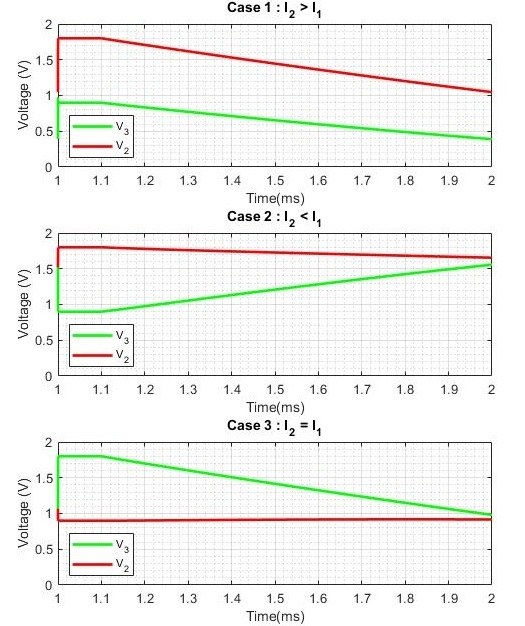

图5 显示绿色的电压 V3 和红色的电压 V2 具有相同的斜率。因此,在这种情况下很难测量电流 I1。此外,如果电流 I2 高于电流 I1,则测量 I1 将变得过于困难。如果电流 I2 高于电流 I1,情况将更糟。

在下一次仿真中,我们添加了一个附加电容以平衡结电容的值。我们模拟了三种不同的情况:第一种是电流 I2 高于电流 I1;第二种是电流 I1 高于电流 I2;最后一种是两个电流具有相同的值。仿真的结果如图6所示。

电压V2和V3分别以红色和绿色表示。对于第一种情况,我们可以注意到V2的斜率比V3的斜率更重要,因此电流I2高于电流I1。对于第二种情况,V3的斜率为正,意味着电流I1大于电流I2,而V2的斜率给出了电流I2的值。对于最后一种情况,V3的斜率为零,意味着两个电流具有相同的值,而斜率V2给出了电流I2的值。因此,我们可以推导出电流I1的值。

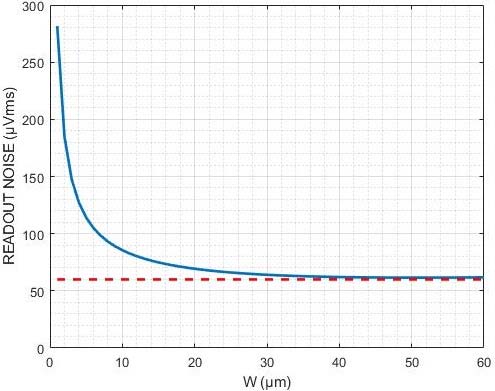

B. 噪声优化

通过改变源极跟随器的宽度,我们得到像素输出端不同的噪声功率谱密度。我们计算了噪声数字信号处理曲线下的面积,从而得到噪声功率。噪声功率的平方根如图7所示。

我们可以注意到,噪声值趋向于60μVrms,并且该噪声值在40μm和60μm之间保持恒定。因此,我们选择40μm以在噪声和填充因子之间取得最佳折衷。

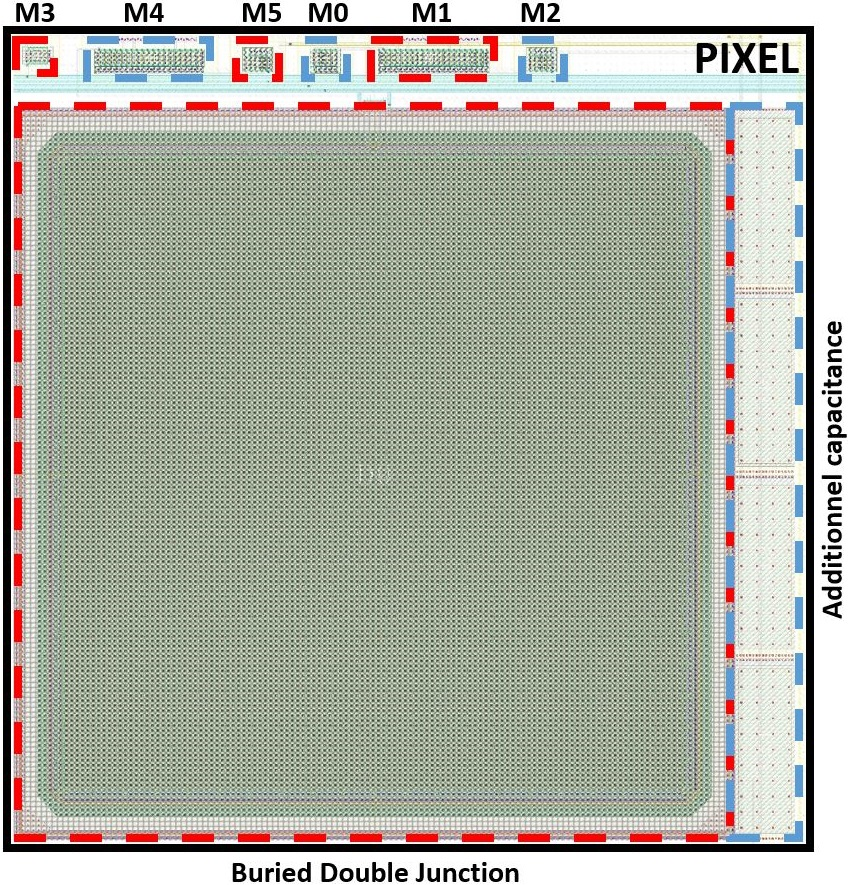

C. 布局

对于布局,我们采用尺寸为100μm×100μm的BDJ,晶体管M0、M2、M3和M5的长度为180nm,宽度为10μm。对于源极跟随器,长度为180nm,宽度为40μm。像素的最终尺寸为128μm×128μm。因此,像素的填充因子为61%。布局如图8所示。

IV. 结论

本文提出了一种用于BDJ光电探测器的电荷积分APS架构,旨在设计用于生物医学诊断的芯片实验室。该BDJ有源像素采用X‐FAB XH018的0.18微米CMOS工艺设计。为了解决BDJ两个光电二极管之间的电容不平衡问题,我们提出了在深层BDJ光电二极管上并联附加电容的方法。通过该方案,我们能够正确且高精度地读取两个光电流I1和I2。我们对BDJ有源像素进行了噪声分析,并将噪声最大的部分——源极跟随器的噪声最小化至60μVrms。我们绘制了BDJ有源像素的布局。在感光面积为100μm×100μm的情况下,BDJ有源像素的面积为128μm×128μm,填充因子为61%。

1413

1413

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?