一、引言

时隔一年多,因某些原因,本人对文章内容进行再次审核并更改。FPGA的时序约束其实和IC中的时序约束是有异曲同工之妙,何为约束,以我目前认知水平来看,就是IC设计或者FPGA设计中, 你需要告诉EDA工具,需要建模成一个怎样的模型。好比FPGA来说,如同乐高积木,你需要去指定你最终要综合成为一个怎样的电路模型,你的每一块乐高积木(cell单元)应该摆放在什么位置,如果都能实现相同功能,你的乐高积木又应该选择多大的一块积木。所以,综合来说,约束,就是为了在综合时候,EDA工具尽量的为满足你的约束条件而努力地通过某些手段(选择合适的cell,优化逻辑算法等)来合成一块电路。而你的约束条件要尽量的与合成后的电路的工作环境相同,让EDA工具综合后的这块电路在跑仿真的时候是与实际工作环境是接近的,这样你跑后仿真出来的结果与实际的烧到FPGA上后,才是接近的。

关于时序分析,各路机构讲解得很多,但本博主希望从Intel官方的指导来学习,官方提供了很多公式,但是实际上,我们不需要记住这些这么多的公式,在本文,我总结了需要记住理解的公式和一些时序分析原理(工程中不需要,内嵌于Intel EDA工具的time quest会自动计算出),但记住的话,会对日后工作帮助较大。

作者:ciscomonkey

二、时序术语terminology

1、数字电路原理

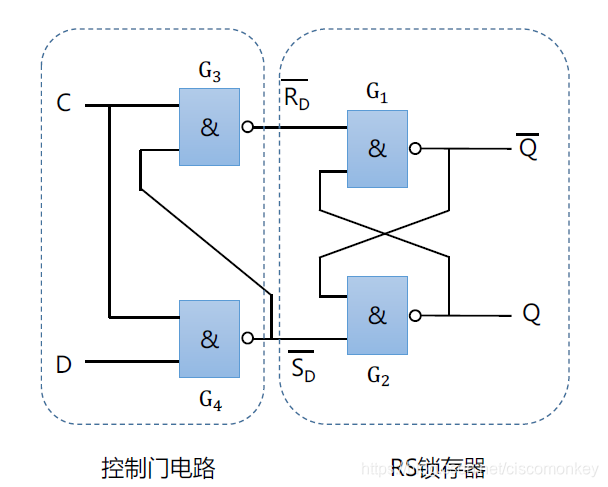

1.1、D锁存器:

能够将输入端的单路数据D存入到锁存器中的电路,此时寄存器的状态是由激励输入端D来确定的,并且D等于什么,寄存器的状态就是什么,也就是说,将单路数据D存入到了锁存器中。

D锁存器的示意图如下:

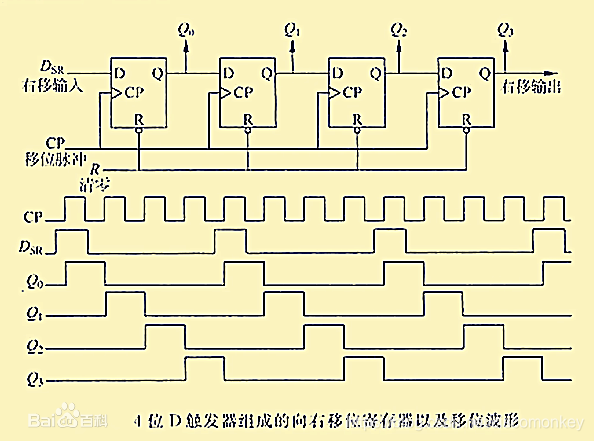

1.2、触发器:

触发器,是数字电路中一种具有记忆功能的逻辑元件。触发器对脉冲边沿敏感的存储单元电路,它只在触发脉冲的上升沿(或下降沿)瞬间改变其状态。在数字电路中,可以记录二进制数字信号“0”和“1”。

D触发器的原理如下图所示:

D锁存器和D触发器的波形图对比如下图所示:

1.3、寄存器:

寄存器电路是数字逻辑电路的基础模块。寄存器用于寄存一组二值代码,它被广泛地用于各类数字系统和数字计算机中。由于一个触发器能够存储一位二值代码,所以用N个触发器能够存储N位二值代码。

由四位D触发器组成的右移寄存器结构如下图所示:

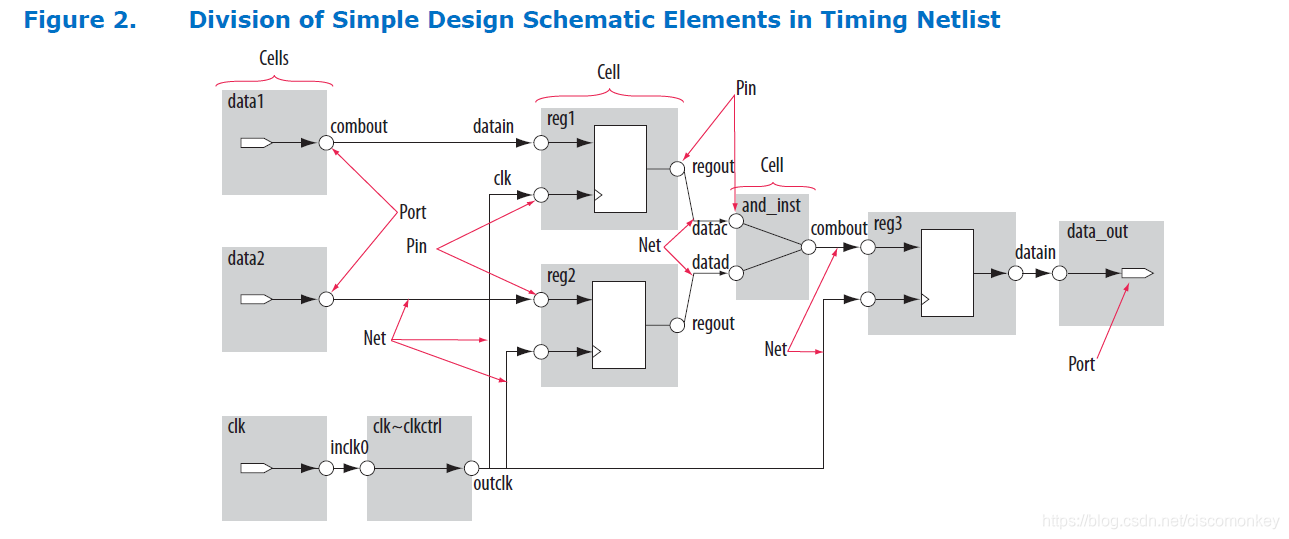

2、时序网表中的元素

时序网表中的各个元素(elements):

elements这个概念包括了网表中的寄存器、线网、pin口等等

2.1、时序路径(Timing paths)

时序路径包括:

1、clock paths:外部或者内部生成的时钟到寄存器的pin的路径

2、Data paths:从一个elements到另一个elements的数据传输的路径

3、Asynchronous path:异步路径,通常是复位信号or清零信号

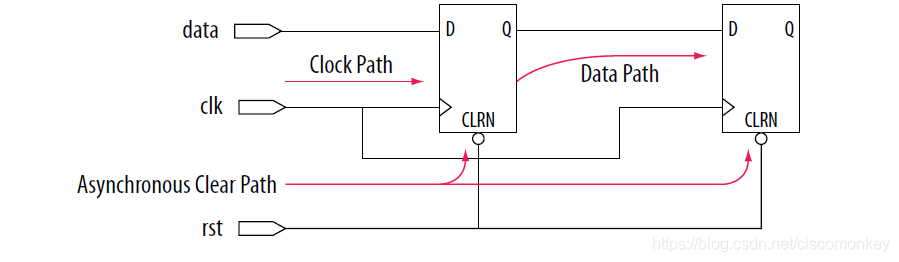

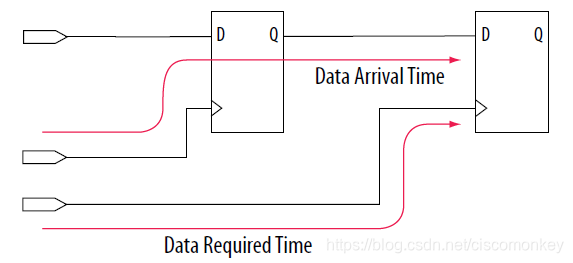

经典的时序分析模型如下图所示,只要存在两个寄存器,之前的数据传输,都可以建立如下的时序分析模型

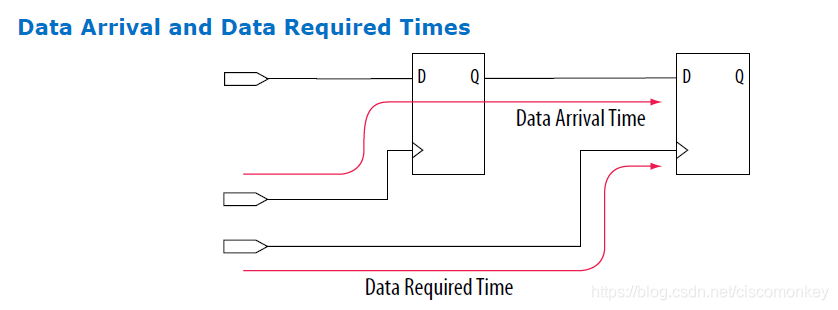

2.2、数据和时钟的抵达时间

时序分析器在确认时序路径后会报告数据和时钟到达寄存器的pin脚的时间。

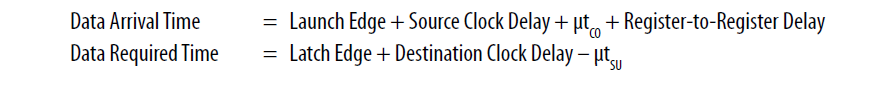

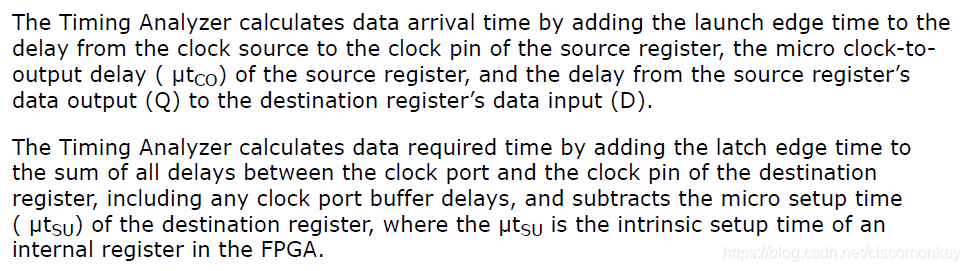

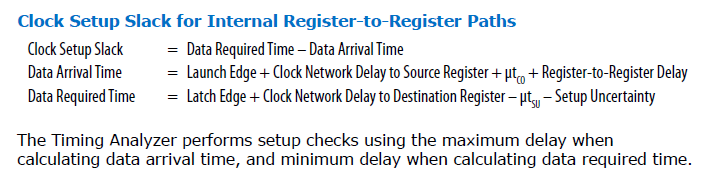

对于Data Arrival Time的理解:

其中Launch Edge指的是发起沿,Source Clock Delay指的是时钟源抵达第一个D触发器的时钟延时,utco比较难理解,就是时钟上升沿到达了第一个D触发器后,要经过第一个D触发器内部的走线,才能真正的去检测出clk上升沿的到来,也就是说才能真正的发起launch,将此时第一个寄存器的数据D端口传到Q端口。regist—to-regist的延时就非常好理解了,就是第一个寄存器的Q到达下一级寄存器的D端口需要走的数据延迟,可能这个延迟经过了组合逻辑运算。

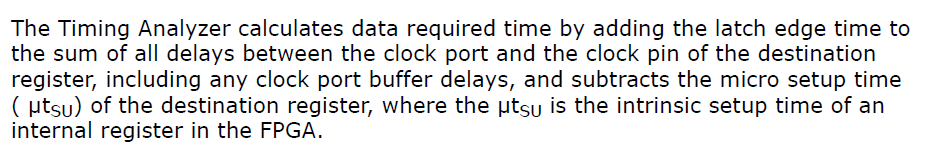

对于Data Required Time的理解:

在Data Require Time中,锁存沿时间+目的时钟延迟 -utsu。首先需要理解的是Latch沿,Latch沿指的是第二个寄存器开始从捕获到第一个寄存器Q端的这个时刻,如上图的理想状态上是一个cycle。destination clock delay是是时钟的到达延迟,也就是说时钟从时钟源到达第二个寄存器的时间延迟,utsu指的是第二级寄存器所需要的建立时间。

综上所述,data arrival time 就是数据实际到达的时间,data required time是数据需要的时间。

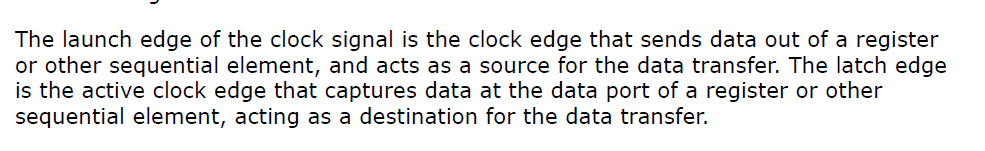

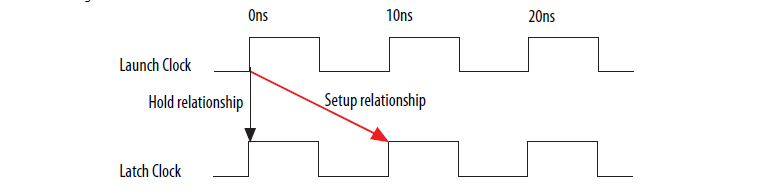

2.3、启动沿和锁存沿Launch and Latch Edges

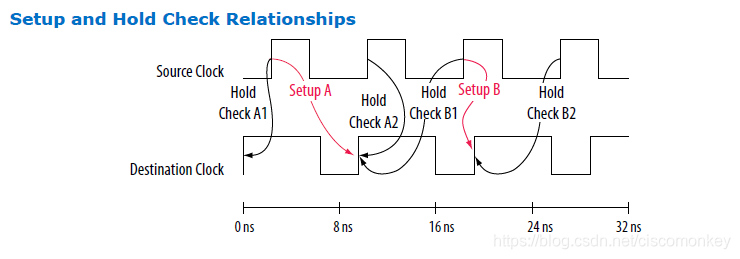

2.4、启动沿和锁存沿的建立关系和保持关系Setup and Hold Relationship for Launch and Latch Edges

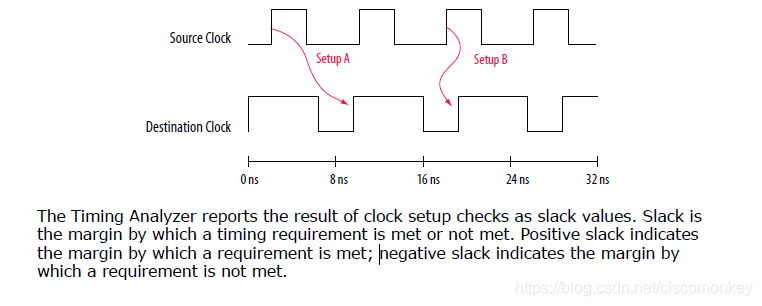

2.5 Slack的概念

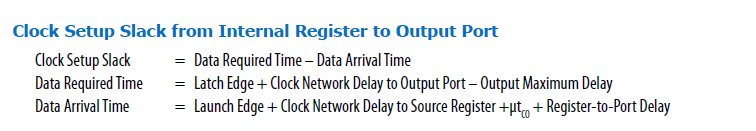

以下是三种常用的时序模型,第一种是最常见的,称之为register to register path(寄存器与寄存器之间)、input to register(输入到寄存器)、register to output(寄存器到输出)

在FPGA内部用的主要是第一中,后面两种同样是建立如2.1的模型,不过是在FPGA外部与FPGA内部建立,或者说是在你的design module与别的mudule之间建立。

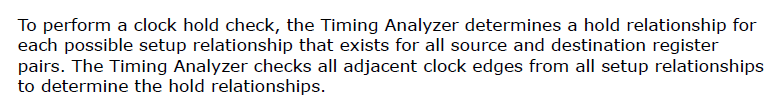

2.5.1 setup and hold check relationship

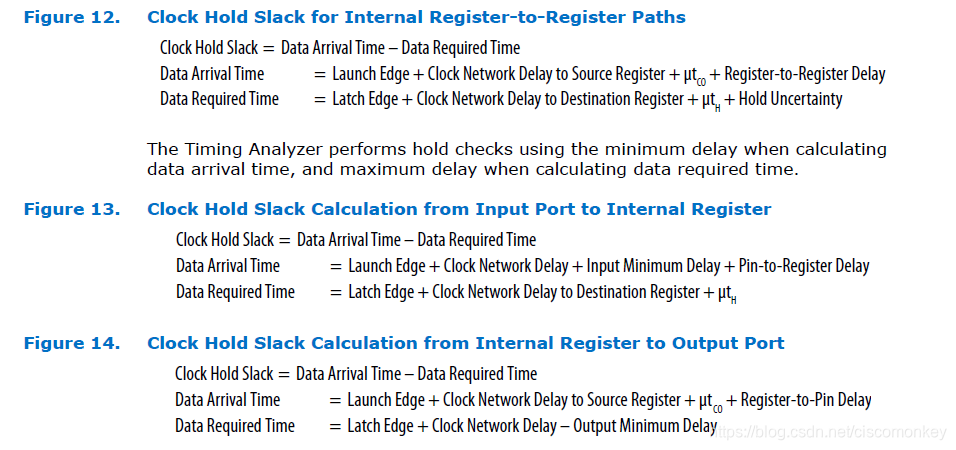

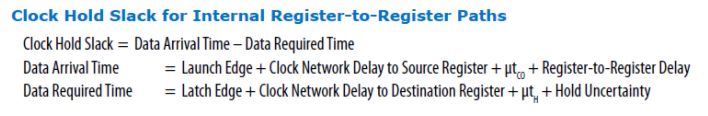

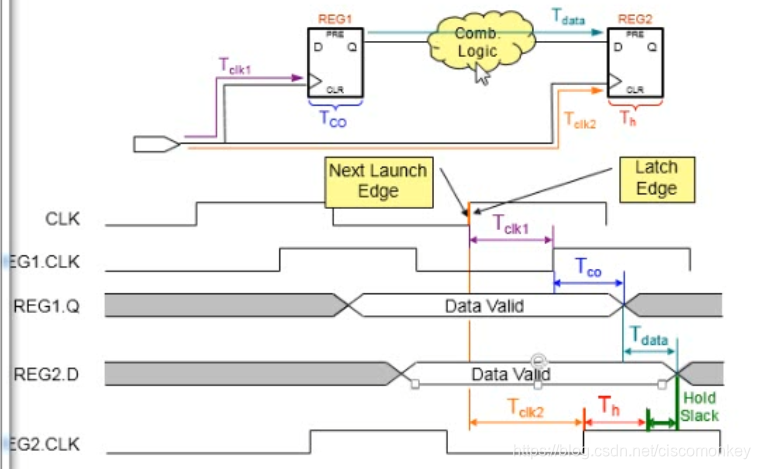

上述公式中,常用的是figure 12,属于寄存器与寄存器之间hold slack的寄存,需要保证hold slack为正。

2.5.2 Recovery and Removal Analysis复位信号的约束

如果异步复位信号来自设备I/O端口,则必须为计时分析器的异步复位端口创建输入延迟约束,以便在路径上执行恢复分析,异步复位信号非常类似与时钟信号的slack和hold的计算。

如果异步复位信号来自设备引脚,则必须分配输入最小延迟时间分配到异步复位针的时间分析器对路径执行复位分析。

这里,我们先暂时不给出公式,pdf里面有。

三、时序约束必备的公式

上述介绍了大量的公式,但是真正需要我们记住的,是如下的,这里已经总结好了。可能会在以后工作中遇到,后续我会再补充一些计算题,供练习。

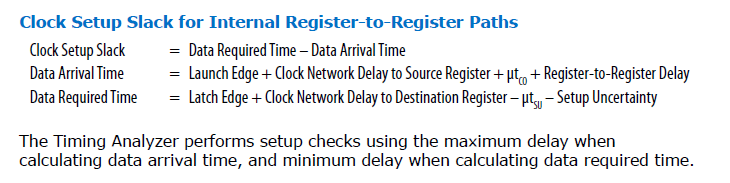

3.1 建立余量:

utco:触发器内部的时钟延时,也就是说数据是在我们的上升沿进行采样的,但是时钟进入我们的触发器件后,还需要一段内部的走线延时,这点可以看触发器的内部结构。

utsu:是数据到来的建立时间门限,也就是说,数据在latch被采样,但是数据至少要在ustu之前到来,utsu这个值是芯片固有的。

下面这个是计算建立余量用到的公式,是需要理解并背下来的。

数据需求时间是要求数据在data arrival time的时间之前到来,数据到达时间(data arrival time)是数据实际到达的时间,那么建立余量slack就是数据需求的时间减去数据到达的时间。剩下的余量,就是数据提前到达的时间,这样就可以保证数据在tsu门限值之前到来了,如果数据传输太慢,register-to-register 的delay太大(组合逻辑太多),那么上一次的数据就会落在tsu的区域以内,导致采样会出问题。

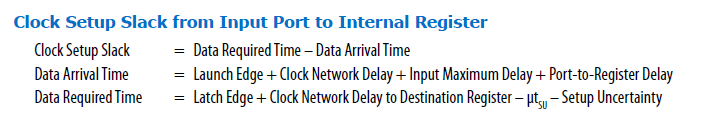

3.2 保持余量:

对于保持余量的分析同样重要,我们再看看保持余量。

以上公式从直观上,只是改变了需求时间,但是注意了,这里的data arrival time 的launch edge并不是刚开始的launch,而是next launch(也相当于latch edge)。所以,我觉得官方这个公式让人容易引起误解,小伙伴们要注意啦。所以,如果数据传输过快了,那么就会导致下个数据的启动沿立即开始,而此时,当前的数据都还没有经过触发器采集数据固有的uth这段时间,导致数据保存失败。

以上两个属于寄存器与寄存器之间的建立余量和保持余量的公式,是非常重要的,其他情况我们暂时不管。建议从图片理解记忆。值得注意的是保持时间的launch指的是next launch,这一点官方文档容易让人引起误会。

四、引用:

ug-qpp-timing-analyzer.pdf

https://download.youkuaiyun.com/download/ciscomonkey/10991222

本文深入解析FPGA时序约束,涵盖数字电路原理、时序路径分析、时序约束公式等内容,强调EDA工具在综合过程中的角色,提供实用公式及时序分析原理,适合FPGA设计人员学习。

本文深入解析FPGA时序约束,涵盖数字电路原理、时序路径分析、时序约束公式等内容,强调EDA工具在综合过程中的角色,提供实用公式及时序分析原理,适合FPGA设计人员学习。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?