如果我们的程序足够复杂,只有一个模块一个模块的写程序,然后进行相关的testbench测试,这样,会有助于我们顺利完成一个较大的工程。如果全部写完后,再去对顶层测试,一旦有错,那么找起来,相当麻烦,也许运行一次就要花费大量时间,效率极低。(后续在此文基础上继续补充,欢迎评论加入你的工程建议)

- suggest-1:分模块测试的好处

先写模块,然后将此模块设为顶层,然后立马针对此模块进行测试。

在setting--->general 下面可以设置顶层

在files里面可以暂时移除某些模块,完成分模块的测试。

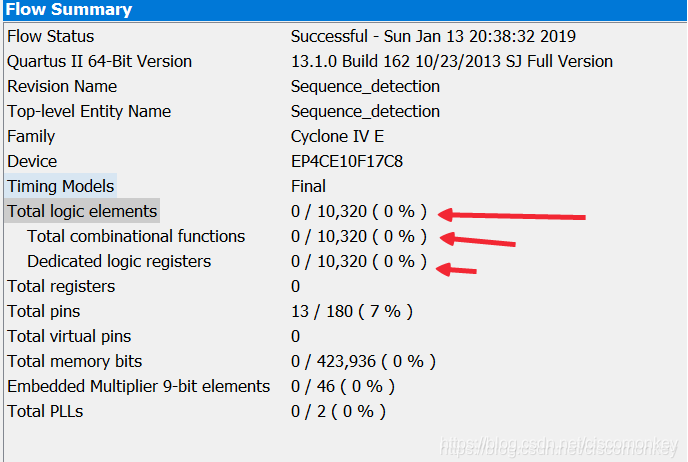

- suggest-2: 综合报告资源为0

如果输出output有部分端口没有赋予值,那么此时综合后产生的报表,消耗资源将显示0.

- suggest-3: 端口错误

在手动更改顶层文件的端口后,请记得更改TB文件中的端口。

- suggest-4: modisim重编译

有时候TB文件可能会出现语法错误,这时候,quartus不会提示的,只有modisim才会提示,所以点击.在 no design下面查看了哪里的语法错误过后,然后不用关闭modisim,在quartus的TB文件下更改,保存。这个时候再返回modisim,他会提示你让你overwrite 还是reload,选择reload即可,然后再work目录下,选择work目录下的文件右键recompile,再点击restart再点击run all。

- suggest-5: 更改modisim run一次的步长

如果点击run,而不是run all,那么向前迈进的长度。

更改此处后,restart即可。

- suggest-6: modisim波形时间显示方式调整

本文分享了FPGA设计中分模块测试的重要性及具体操作方法,包括如何设置顶层模块进行测试,调整综合报告资源显示,修改端口后的同步更新,解决modisim编译错误,以及调整波形时间显示等实用技巧。

本文分享了FPGA设计中分模块测试的重要性及具体操作方法,包括如何设置顶层模块进行测试,调整综合报告资源显示,修改端口后的同步更新,解决modisim编译错误,以及调整波形时间显示等实用技巧。

1718

1718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?