【ASIC】时序分析实例之如何看懂时序报告

背景

本篇文章,是对b站UP主的视频讲解笔记,非常感谢这位UP。

正文

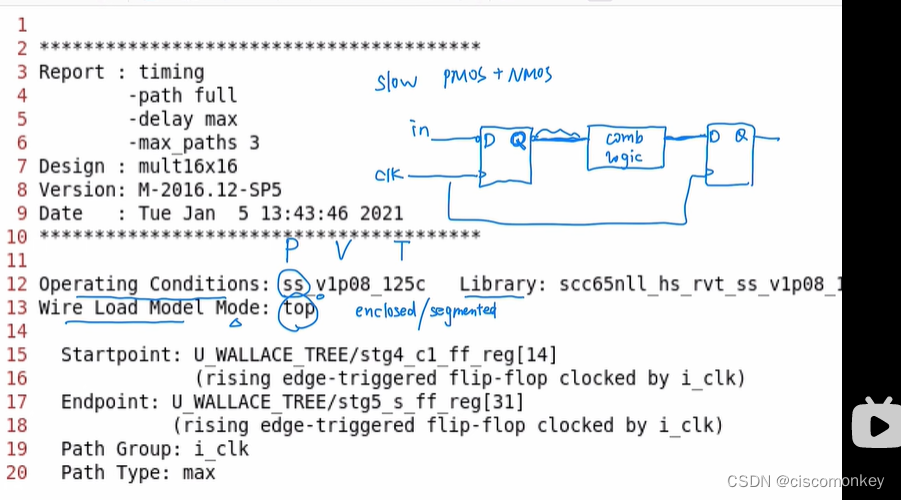

如图所示,其中PVT 代表的是 工艺、电压、温度,如图是slow模型,1.8v电压,125°的高温。

wire load model是用来估算线延迟,而这个mode为top,指的是估计线延迟的时候,是根据design的整个面积大小去估算的,比较保守。此外还有enclosed模式,以及延时最小的segmented模式。(具体可以查PT userguide)

如上图所示,其中r代表rise,f代表falling,因为对于数据而言rising和falling的耗时是不一样的。

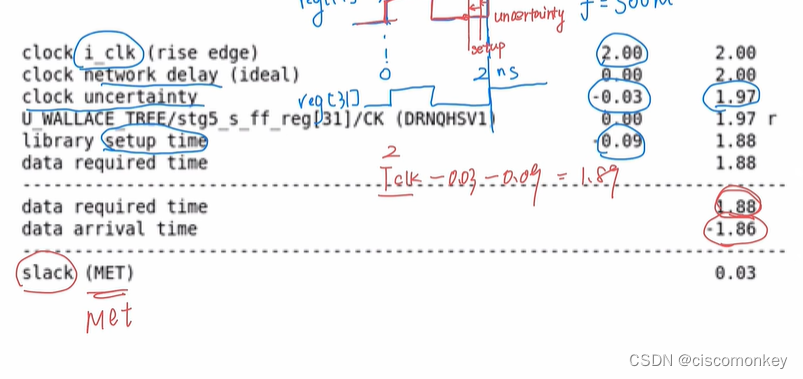

如上图所示,因为电路存在不确定性,所以对于require time来说需要有uncertainty time这一项

本文是关于ASIC时序分析的学习笔记,主要解析如何解读时序报告。PVT代表工艺、电压、温度,文中以slow模型为例,说明1.8v电压和125°高温条件。wireloadmodel用于估算线延迟,top模式基于整个设计面积估计,相对保守。另外提到了enclosed和segmented模式。报告中还关注了上升沿(rise)和下降沿(fall)的不同耗时,以及不确定性时间(uncertaintytime)在电路不确定性中的作用。

本文是关于ASIC时序分析的学习笔记,主要解析如何解读时序报告。PVT代表工艺、电压、温度,文中以slow模型为例,说明1.8v电压和125°高温条件。wireloadmodel用于估算线延迟,top模式基于整个设计面积估计,相对保守。另外提到了enclosed和segmented模式。报告中还关注了上升沿(rise)和下降沿(fall)的不同耗时,以及不确定性时间(uncertaintytime)在电路不确定性中的作用。

3042

3042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?