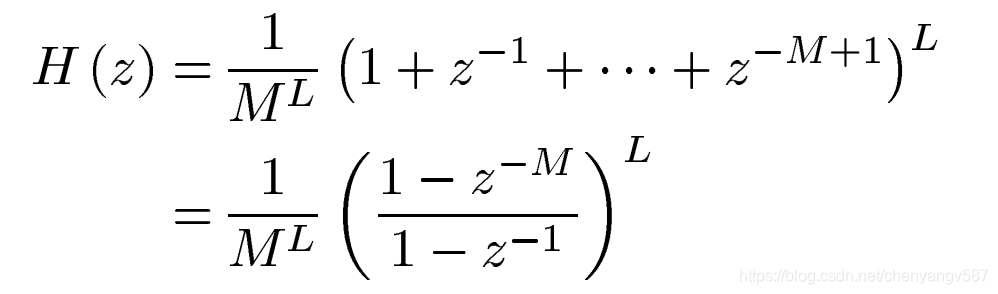

Sinc3滤波器常用在二阶增量式sigma-delta ADC中,其传递函数为

本文实现了一个L=3,M=1600的SINC3滤波器用于一个大约22位的增量式Sigma-Delta ADC中。

下面展示一些 verilog实现sinc3滤波器的代码。

// An highlighted block

module sinc3 (in,clk,clk_clc,en,resu);

input in,clk,clk_clc,en;

output resu;

reg [1600:1] bs; //保存输入

reg [10:0] bs2 [1600:1]; //memory保存第一级输出的值

reg [21:0] bs3 [1600:1]; //memory保存第二级输出的值

reg [10:0] count,count_1;//用来指定memory的地址

reg [10:0] temp2;//临时存储第一级的1600时钟前的数据

reg [21:0] temp3;//临时存储第二级的1600时钟前的数据

reg [32:0] resu;

reg [10:0] count_clc;//用来清零memory时地址计数

always@(posedge clk_clc)//进行memory清零

begin

if(en==1)

count_clc<=11'b0;

else if (count_clc<11'd1600)

count_clc<=count_clc+1'b1;

else

count_clc<=1'b1;

end

always@(posedge clk_clc)

begin

if(en==0)

begin

bs[count_clc]<=0;

bs2[count_clc]<=0;

bs3[count_clc]<=0;

end

end

//寄存器清零结束

always@(posedge clk)

begin

if(en==0)

begin

count<=11'd1;

count_1<=11'd1600;

end

else if (count==11'd1600)

begin

count<=11'd1;

count_1<=count;

end

else

begin

count<=count+1'b1;

count_1<=count;

end

end

always@(posedge clk)

begin

if (en==1)

begin

bs[count]<=in;

end

end

always@(posedge clk)

begin

if(en==0)

temp2<=0;

else

begin

temp2<=bs2[count];

bs2[count]<=bs2[count_1]+in-bs[count];

end

end

always@(posedge clk)

begin

if(en==0)

temp3<=0;

else

begin

temp3<=bs3[count];

bs3[count]<=bs3[count_1]+bs2[count_1]-temp2;

end

end

always@(posedge clk)

begin

if(en==0)

resu<=0;

else

begin

resu<=resu+bs3[count_1]-temp3;

end

end

endmodule

本文介绍了一种用于22位增量式Sigma-DeltaADC的SINC3滤波器的Verilog实现,该滤波器参数为L=3,M=1600。文章提供了详细的Verilog代码,展示了如何通过寄存器和内存操作实现SINC3滤波功能。

本文介绍了一种用于22位增量式Sigma-DeltaADC的SINC3滤波器的Verilog实现,该滤波器参数为L=3,M=1600。文章提供了详细的Verilog代码,展示了如何通过寄存器和内存操作实现SINC3滤波功能。

1333

1333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?