一、实验目的

1.掌握较为综合的数字系统的设计方法,能够采用层次化、模块化设计方法, 使用SSI、MSI、Verilog HDL 等进行综合数字逻辑电路的设计。

2.掌握显示扫描控制电路的设计方法。

3.能够使用Logisim、Vivado仿真工具对设计方案进行仿真分析与论证。

4.能够对设计电路进行测试验证。

二、实验仪器及设备

1.PC机 1台(1G以上内存)

2.Logisim,Vivado 集成开发环境

3. Nexys A7-100T FPGA 综合实验板

三、实验内容

1、 基本要求

1)设计多功能运动秒表:①能够计时;

②能够记录并存储8个赛道成绩;

③能够查看并显示8个赛道成绩。

2)输入输出方案:自主选择,需考虑应用习惯。在 Logisim 环境下实现电 路及测试,要求至少有1-2个模块用自己封装的74161实现。

3)用Verilog HDL 描述电路,编写电路的仿真测试代码。 进阶要求 实现电路的输入输出方案简单、方便,电路实现使用资源较少。

2、拓展要求 运动秒表能适用于100米短跑-3000米长跑竞赛的范围。

四、实验步骤

1、计数器板块制作

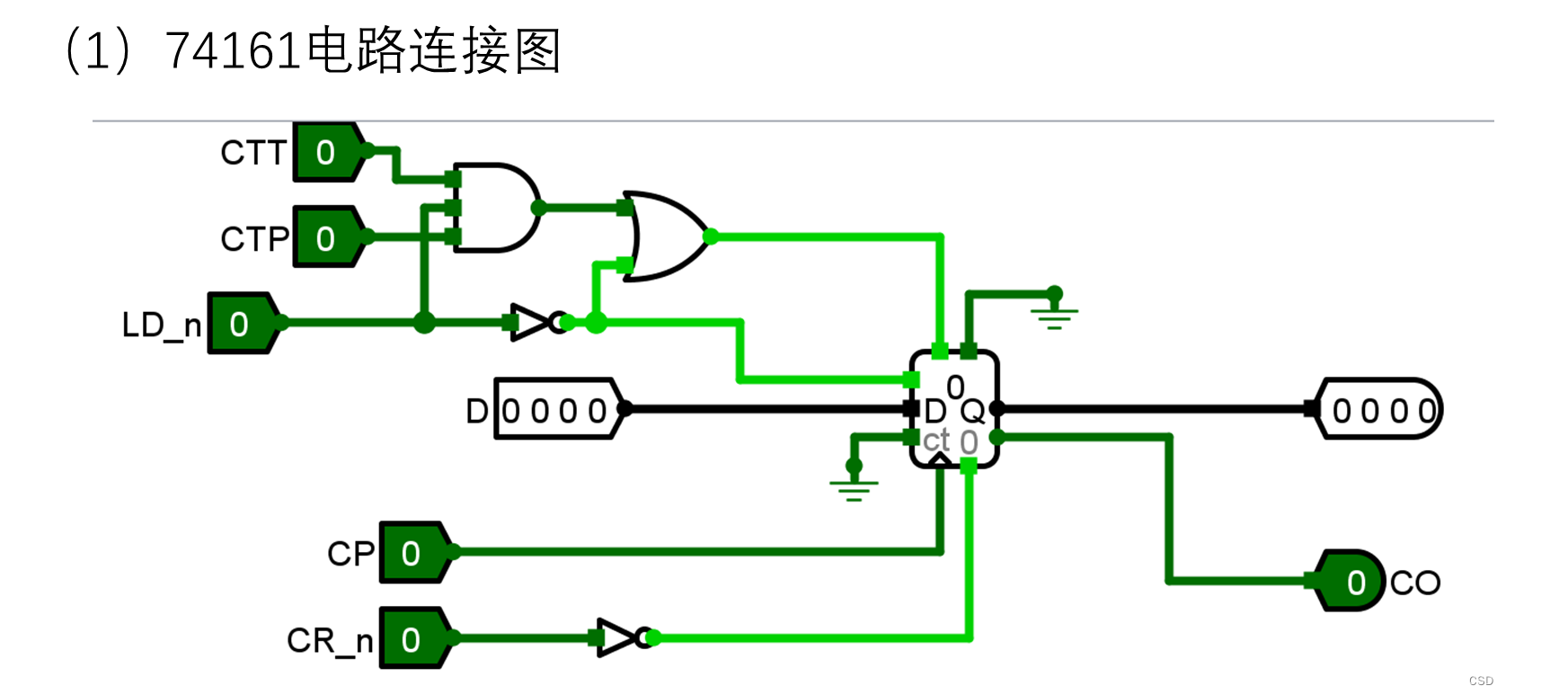

(1)74161电路连接图

(2)利用74161电路组装成模为6的计数器

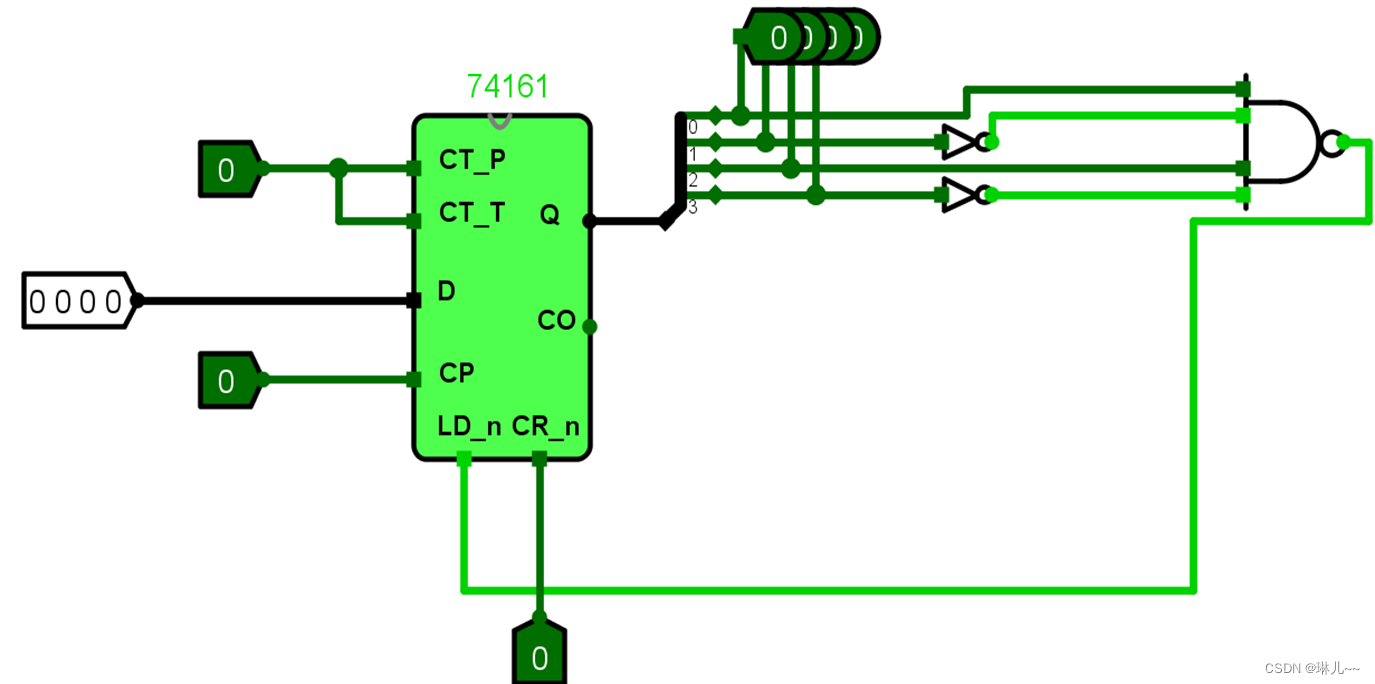

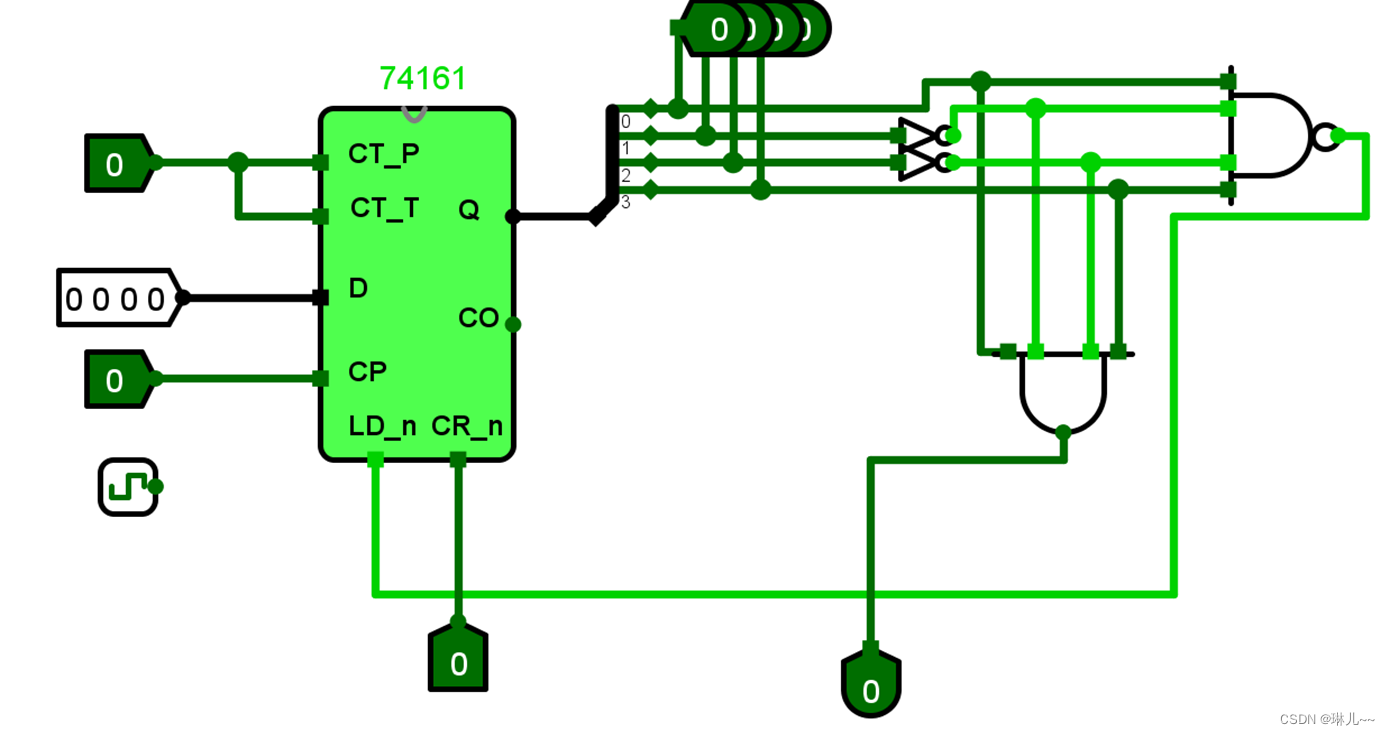

(3)利用74161电路组装成模为10的计数器

(3)利用74161电路组装成模为10的计数器

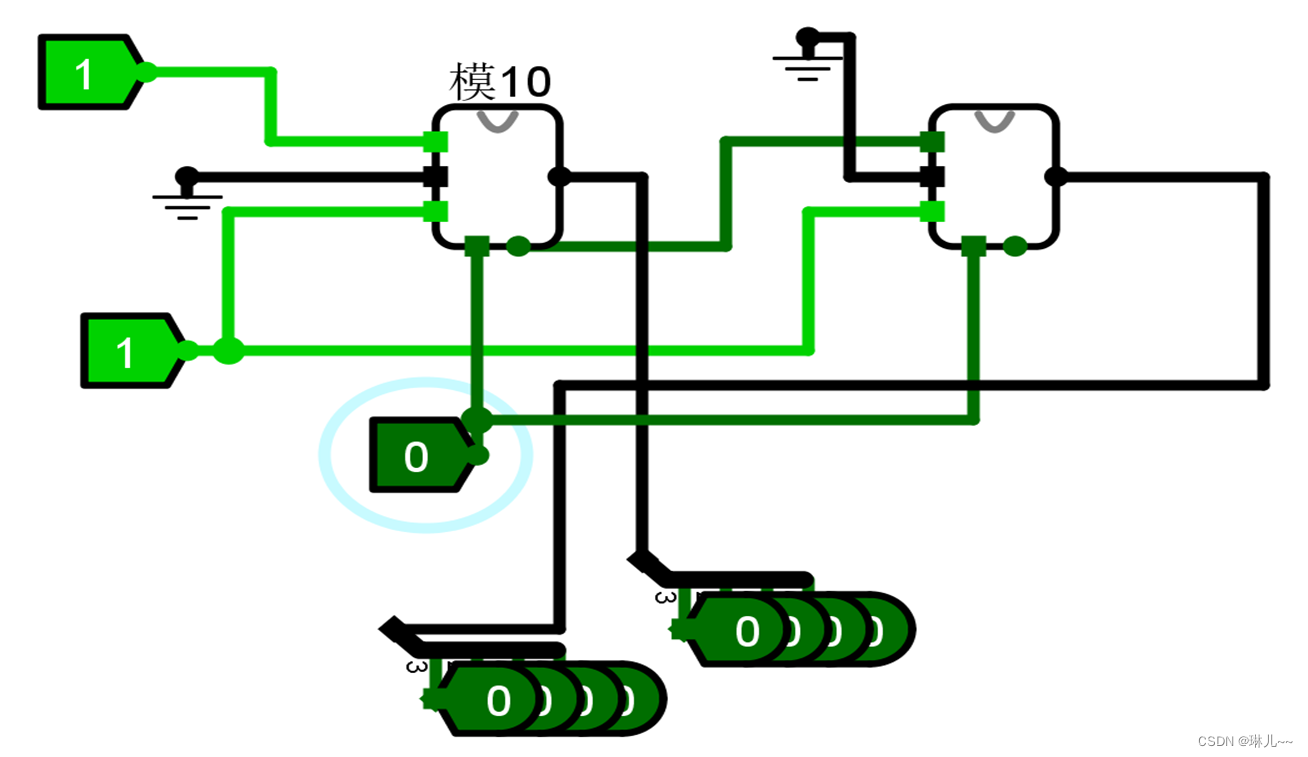

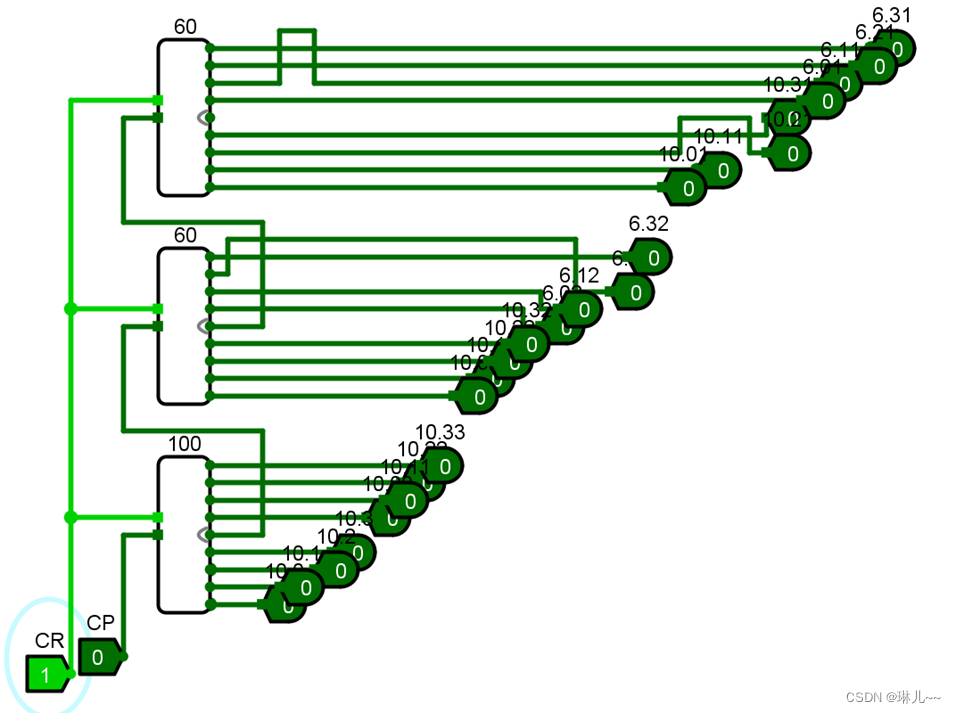

(4)利用模为6和模为10连成模60的计数器

(5)两个模为10连成模60的计数器

(6)两个模60和一个模100级联成计数器板块

将模100的输出进位连接到模60的CP端,将模60的进位连接到模60的CP端,CR为清零端,CR为一时计数清零。

2、存储器板块制作

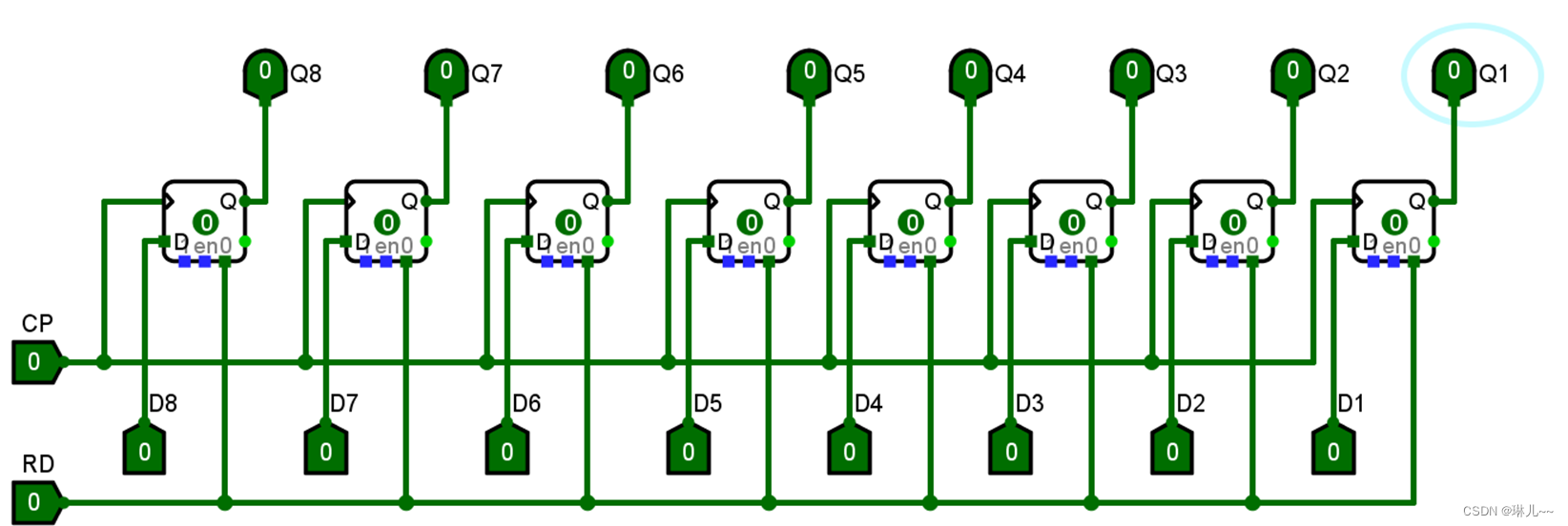

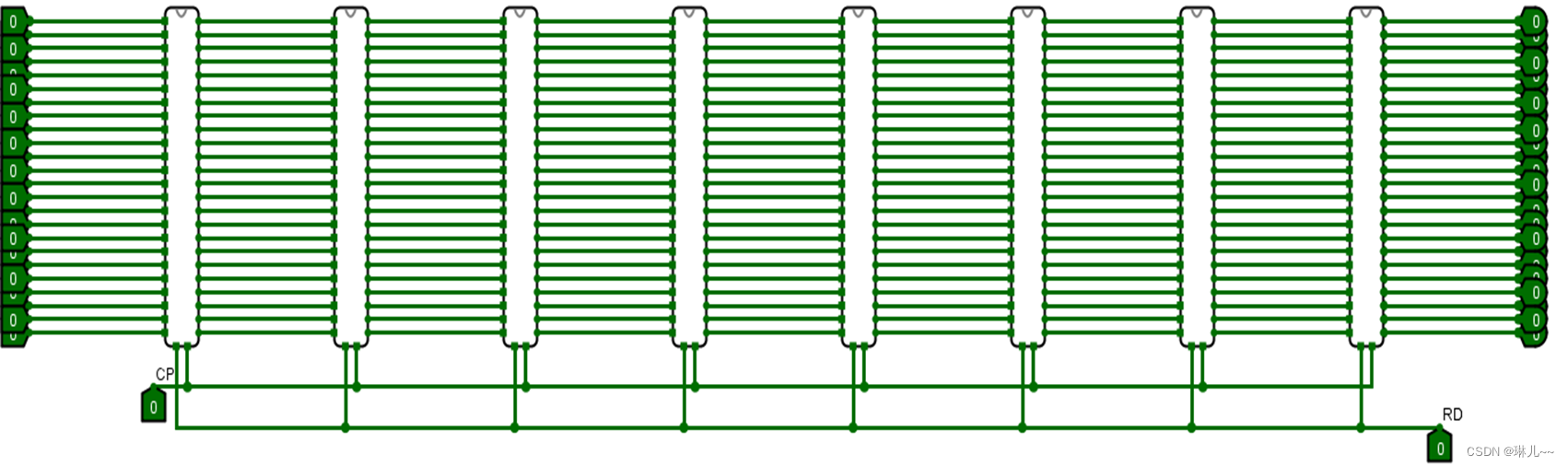

(1)八个D触发器级联组成的寄存器

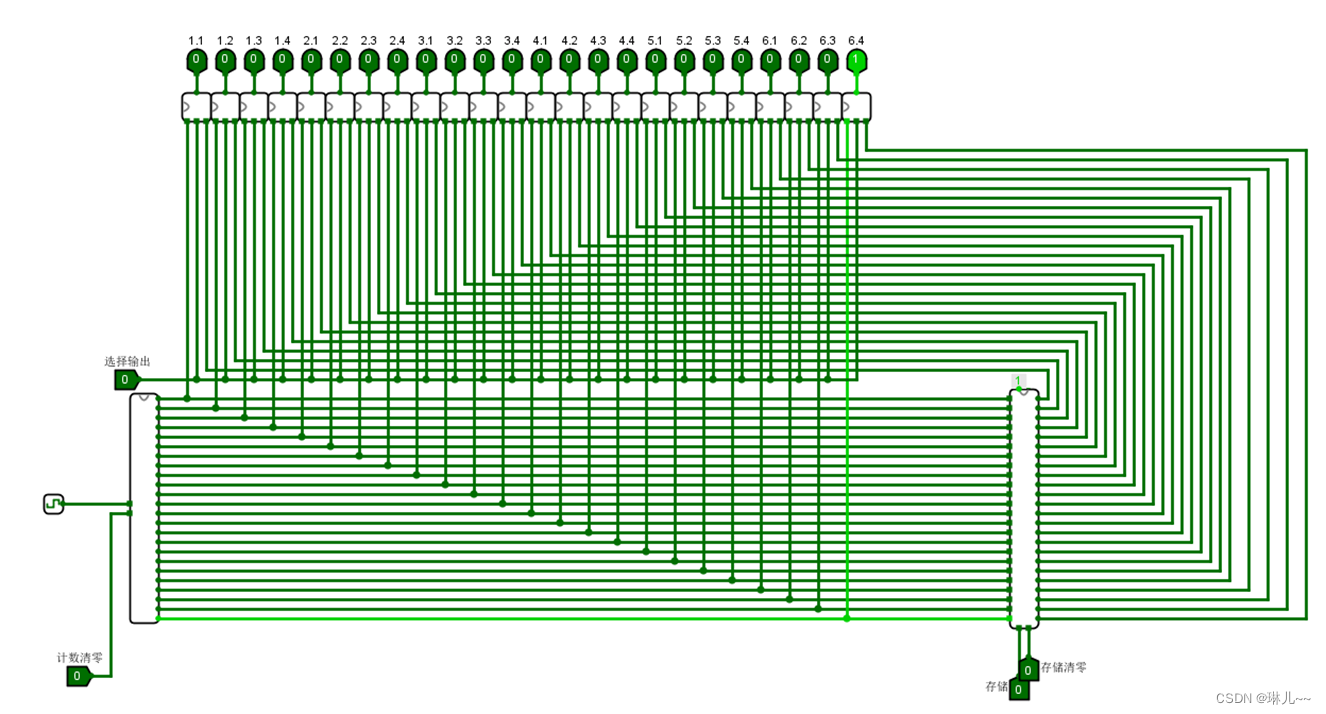

(2)三个寄存器板块组成的一个并行输入的存储一个赛道成绩的板块

在CP上升沿时刻存储计时器计数一次的数值

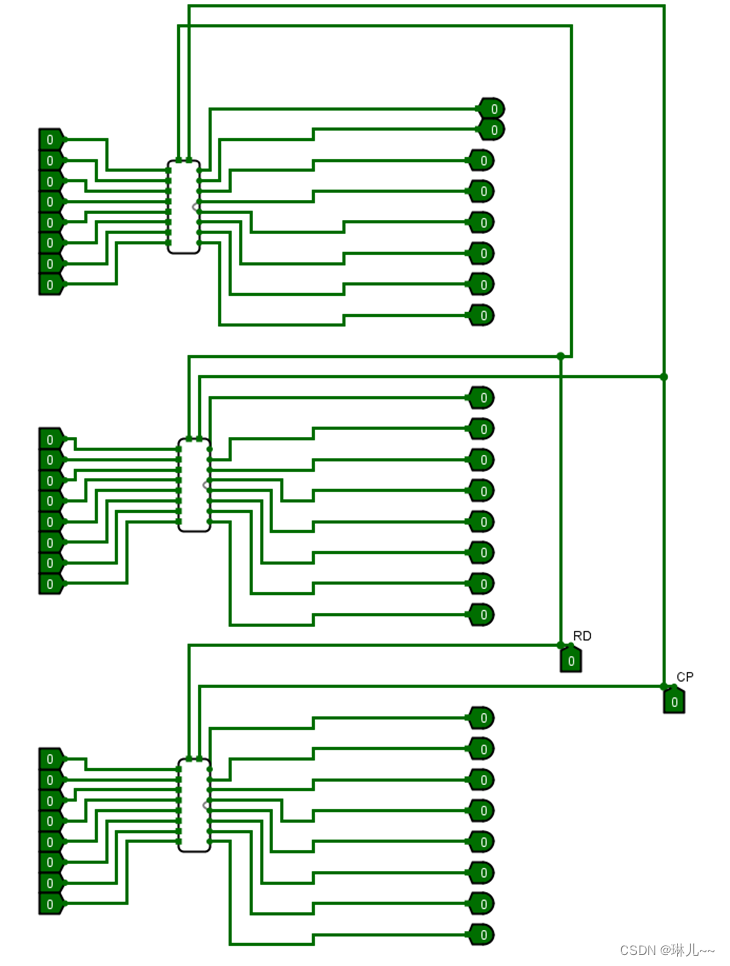

(3)八个一次赛道成绩板块连接在一起组成可以存储八个赛道成绩的板块

3、将计数器板块和存储器板块进行连接寄存和输出

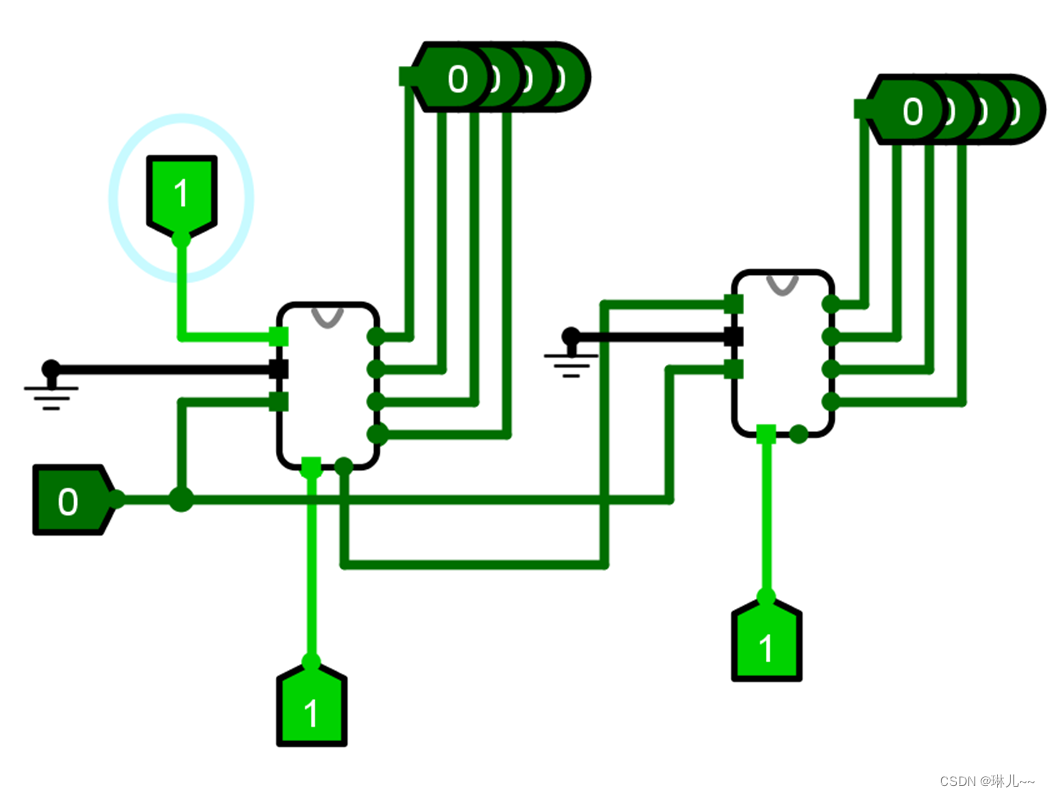

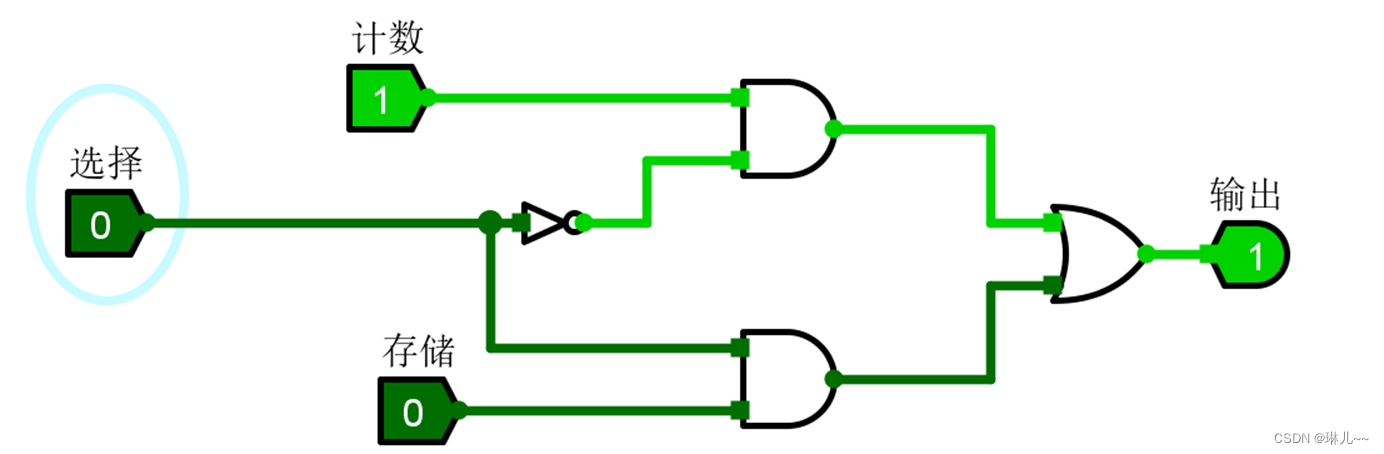

(1)制作2选1选择器

功能:选择是输出计时器模块的数据还是存储模块的数据。当选择端口为1时选择存储模块,当选择端口为0时选择计数模块

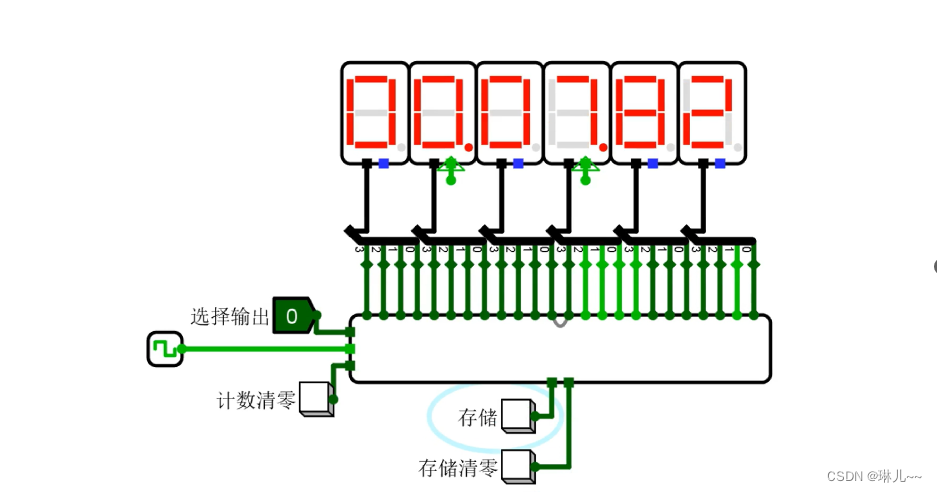

(2)将计数模块和存储模块连接起来用2选1数据选择器选择输出

功能:当选择输出端为0时输出端为计时器计时数据,根据时钟信号实时变化;当选择输出端为1时,通过存储模块的存储按钮存储八次后再依次按下存储按钮会依次输出八次存储的结果。

(3)秒表结果测试:实现计时功能以及把赛道成绩存储及输出

五、实验完成

4660

4660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?