芯片型号:STM32F427VG

软件版本:Stm32CubeMx 5.6.0

库版本:STM32Cube FW_F4 V1.25.0

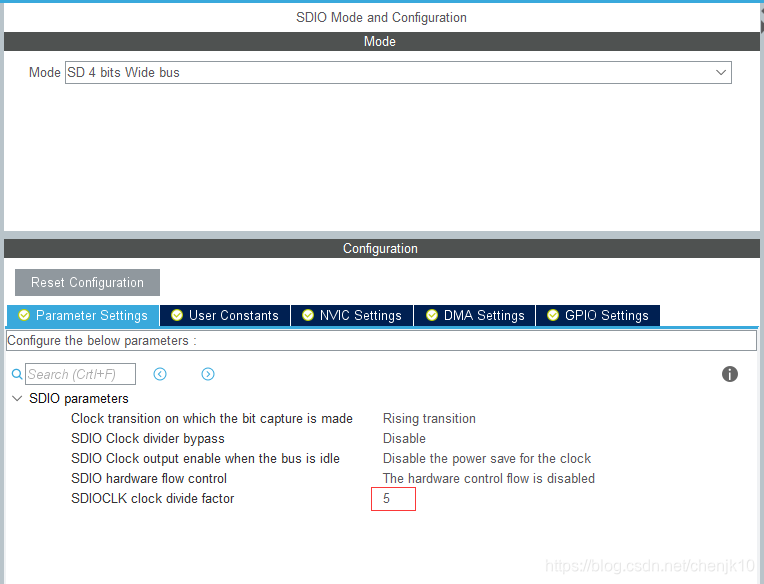

配置SDIO:

卡时钟(SDIO_CK ):每个时钟周期在命令和数据线上传输 1 位命令或数据。对于多媒体卡 V3.31 协议,时钟频率可以在 0MHz 至 20MHz 间变化;对于多媒体卡 V4.0/4.2 协议,时钟频率可以在 0MHz 至 48MHz 间变化;对于 SD 或 SD I/O 卡,时钟频率可以在 0MHz 至 25MHz间变化。

SDIO适配器时钟( SDIOCLK ):该时钟用于驱动 SDIO 适配器,其频率等于 AHB 总线频率( HCLK ),并用于产生 DIO_CK 时钟。

AHB 总线接口时钟( HCLK/2 ):该时钟用于驱动 SDIO 的 AHB 总线接口,其频率为HCLK/2 。

前面提到,我们的SD 卡时钟( SDIO_CK ),根据卡的不同,可能有好几个区间,这就涉及到时钟频率的设置, SDIO_CK 与SDIOCLK 的关系为:

SDIO_CK=SDIOCLK/(2+CLKDIV)

其中,SDIOCLK 为 HCLK ,一般是 72Mhz(F103系列),而 CLKDIV 则是分配系数,可以通过 SDIO的 SDIO_CLKCR 寄存器进行设置(确保 SDIO_CK 不超过卡的最大操作频率)。

在SD 卡刚刚初始化的时候,其时钟频率( SDIO_CK )是不能超过 400Khz的,否则可能无法完成初始化。在初始化以后,就可以设置时钟频率到最大了(但不可超过 SD卡的最大操作时钟频率)。

注:当配置完发现无法moutSD卡,可以尝试加大CLKDIV值

STM32F4 SDIO+FATFS+FREERTOS配置

STM32F4 SDIO+FATFS+FREERTOS配置

本文介绍STM32F427VG芯片使用STM32CubeMx5.6.0配置SDIO接口、FATFS文件系统及FreeRTOS实时操作系统的过程。详细讲解了SD卡时钟配置、DMA启用、中断设置等内容,并提供了测试代码示例。

本文介绍STM32F427VG芯片使用STM32CubeMx5.6.0配置SDIO接口、FATFS文件系统及FreeRTOS实时操作系统的过程。详细讲解了SD卡时钟配置、DMA启用、中断设置等内容,并提供了测试代码示例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4254

4254

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?