✅ 博主简介:擅长数据搜集与处理、建模仿真、程序设计、仿真代码、论文写作与指导,毕业论文、期刊论文经验交流。

✅ 具体问题可以私信或扫描文章底部二维码。

(1)在自由空间光通信系统中,大气湍流是影响系统性能最为关键的环境因素之一。当光信号穿越大气层进行传输时,由于温度、湿度和气压的不均匀分布,导致空气折射率发生随机起伏,形成复杂的湍流结构。这种结构会引发光波波前的相位畸变、振幅闪烁以及光束漂移等现象,严重破坏光信号的空间相干性和时间稳定性,造成接收端信噪比显著下降,误码率急剧上升,甚至出现通信中断。尤其是在长距离传输或恶劣气象条件下,如近地面、沙漠、海洋上空等区域,大气湍流效应尤为突出。传统上,自适应光学技术被广泛用于波前矫正,其核心是通过波前传感器实时检测畸变,并驱动可变形镜进行补偿。然而,受限于系统响应速度、探测精度以及控制回路延迟,传统方法在面对快速变化的时变湍流信道时往往难以实现精准同步矫正,存在明显的时延失配问题。为突破这一瓶颈,本文提出了一种基于深度学习驱动的波前预矫正机制,旨在通过构建数据驱动模型,提前预测未来时刻的波前畸变状态,从而实现“先发制人”式的主动补偿。该方法的核心思想在于利用历史波前数据的时间序列特性,挖掘大气湍流演变过程中的潜在规律与空间相关性,进而建立从过去到未来的非线性映射关系。具体而言,系统首先采集大量在模拟大气湍流环境下生成的连续波前相位图,这些相位图由基于泽尼克多项式构造的动态相位屏生成,能够精确复现不同程度和结构的湍流扰动。采集的数据集不仅包含空间维度上的畸变分布,还涵盖时间维度上的演化轨迹,为后续的神经网络训练提供了丰富的时空特征样本。在此基础上,设计并训练一个融合卷积神经网络(CNN)与门控循环单元(GRU)优势的复合型深度网络——卷积门控递归单元(ConvGRU),该网络具备强大的时空特征提取能力,既能捕捉波前畸变在空间上的局部模式,又能建模其在时间序列中的动态演化趋势。ConvGRU层通过其特有的记忆门控机制,有效保留长期依赖信息,避免传统RNN在长时间序列中容易出现的梯度消失问题,从而确保对复杂湍流演变过程的准确预测。网络输出为下一时刻或未来若干时刻的波前相位畸变图像预测结果,随后将该预测图像输入至一个专门设计的深度神经网络(DNN)模块,用以反演估计对应的泽尼克多项式系数。泽尼克系数作为描述波前像差的标准正交基展开参数,具有明确的物理意义,能够量化表征各类像差成分,如倾斜、离焦、彗差、球差等。通过精确估计这些系数,系统可以重建出完整的预测波前形态,并据此计算出可变形镜所需的控制电压序列,提前调整镜面形状,实现对即将到来的湍流扰动的预先补偿。实验结果表明,该预矫正方案显著降低了传统自适应光学系统中存在的响应延迟问题,使得波前补偿动作与实际畸变到达时间更加匹配,大幅提升了矫正效率。在室内搭建的模拟大气信道平台上,经过多次重复测试,采用本方案后,最终残余波前误差的均方根值(RMS)相较于未进行任何矫正的情况平均降低了3.15倍,且在中等强度湍流条件下仍能保持良好的稳定性与鲁棒性。此外,该方法无需依赖高成本的高速波前传感器持续工作,可在一定程度上降低系统功耗与硬件复杂度,具备良好的工程应用前景。

(2)除了波前畸变带来的相位干扰外,大气湍流还会引起接收光强的剧烈起伏,即所谓的“闪烁效应”,这种效应在强湍流或长距离传输中尤为明显,容易导致信号幅度发生深度衰落,形成持续时间较长的突发性误码簇,严重威胁通信链路的可靠性。传统的前向纠错码(FEC)虽然能够在一定程度上纠正随机错误,但对于连续出现的大规模突发错误往往力不从心,尤其是在高速率传输场景下,如10Gbps及以上,单次突发错误可能跨越多个数据帧,超出FEC的纠错能力范围,从而引发通信中断。为此,本文提出了一种深度交织与前向纠错码联合优化的抗误码策略,旨在通过增强数据冗余与分散机制,打破突发错误在时间域上的集中性,将其转化为FEC易于处理的随机化小规模错误。深度交织技术的核心在于对原始数据流进行多层次、大跨度的重新排列,使得原本在时间上连续的数据比特被分散到不同的传输时隙中,即使某一时段因强湍流导致大量比特丢失,解交织后这些错误也将被均匀打散,不再集中于某一特定位置。本文设计的交织器采用基于伪随机序列的块交织结构,交织深度可达数千比特级别,确保即使发生长达毫秒级的信号中断,也不会造成关键数据块的整体损毁。同时,交织长度与FEC码字长度之间进行了协同优化,保证解码器在接收端能够获得足够独立的错误分布,提升整体纠错效率。在FEC编码方面,选用了具有强纠错能力的低密度奇偶校验码(LDPC),其采用迭代译码算法,能够在接近香农极限的性能下运行,特别适合高斯白噪声与突发干扰并存的复杂信道环境。LDPC码的校验矩阵经过特殊设计,增强了对突发错误的容忍度,并结合软判决译码技术,充分利用接收信号的幅度信息,进一步提升译码可靠性。整个编码调制链路在FPGA平台上实现,充分发挥其并行处理能力强、时序控制精确的优势,支持高达10Gbps的线速率处理能力。系统收发两端的逻辑代码均采用Verilog HDL语言编写,模块化设计包括数据接口、交织器、LDPC编码/译码引擎、帧同步、扰码与解扰等功能单元。其中,交织模块通过双缓冲机制实现无缝切换,避免因读写冲突导致的数据丢失;LDPC译码器采用分层最小和算法(Layered Min-Sum Algorithm),在保证性能的同时大幅降低计算复杂度,满足实时性要求。功能仿真与综合结果显示,各模块均能稳定工作在目标频率下,资源占用率合理,时序裕量充足。在实际测试中,将该编码系统应用于模拟湍流信道下的FSO链路,结果表明,在相同湍流强度下,联合方案相比单独使用FEC或传统交织技术,误码率下降超过两个数量级,且在经历多次深度衰落事件后仍能快速恢复通信,表现出极强的容错能力与链路韧性。该技术的成功实施为高可用性自由空间光通信系统的构建提供了坚实的技术支撑,尤其适用于对通信连续性要求极高的应用场景,如卫星间激光链路、高空平台通信网络等。

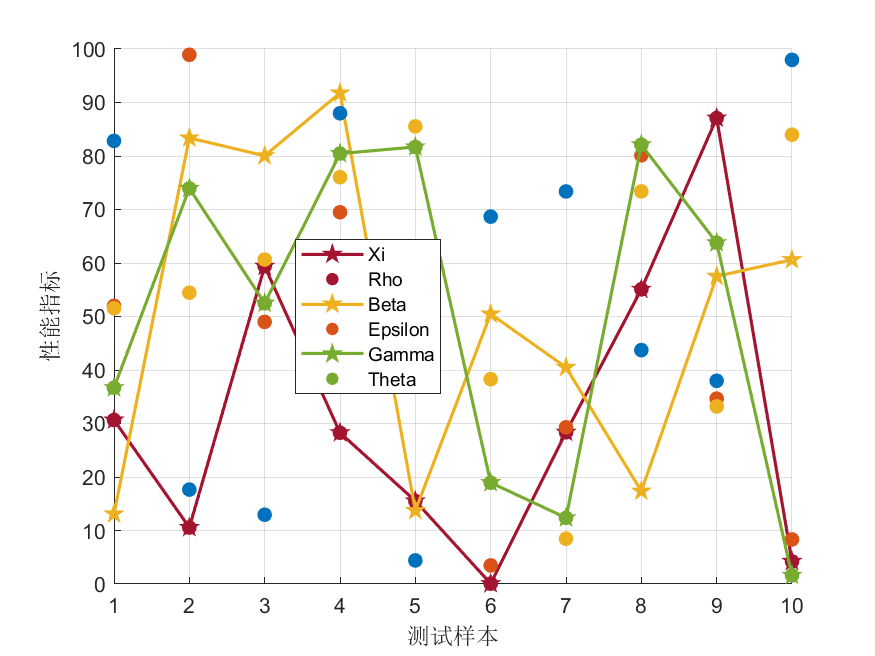

(3)为了全面验证上述两项关键技术的实际效果,本文搭建了一个完整的室内模拟大气湍流信道实验平台,该平台集成了光源发射、动态相位调制、光路传输、波前传感、自适应矫正、信号接收与数字信号处理等多个子系统,形成了闭环可控的测试环境。平台的核心是基于空间光调制器(SLM)的动态相位屏,其能够根据预设的泽尼克系数实时生成符合Kolmogorov湍流统计特性的随机相位分布,从而精确模拟不同强度等级的大气湍流对光波前的影响。相位屏的刷新速率可达数百赫兹,足以覆盖典型大气湍流的时间尺度,确保实验结果的真实性与有效性。发射端采用1550nm波段的高稳定性激光器,该波段不仅具有良好的大气穿透能力,而且与现有光纤通信基础设施兼容,便于未来系统集成。接收端配置高速波前传感器(Shack-Hartmann型)用于实时采集畸变波前数据,同时连接一台高性能可变形镜(Deformable Mirror),用于执行波前矫正操作。整个光学链路布置在防震光学平台上,并加装温控与气流隔离装置,最大限度减少外部环境干扰,确保实验数据的可重复性。在软件层面,开发了一套完整的数据采集、处理与控制软件系统,运行于高性能工作站之上,负责协调各硬件设备的工作节奏,同步记录波前图像、Zernike系数、RMS误差、误码率等关键参数。特别地,针对深度学习模型的训练与部署,构建了专用的数据预处理流水线,包括图像归一化、噪声抑制、时间序列切片等步骤,确保输入数据的质量与一致性。训练过程中采用了大规模并行计算架构,利用GPU集群加速神经网络的收敛过程,缩短模型迭代周期。最终训练完成的ConvGRU-DNN联合模型被部署至嵌入式边缘计算单元,与FPGA控制系统协同工作,实现端到端的实时波前预测与矫正闭环控制。实验过程中,分别测试了不同湍流强度(Cn²从10⁻¹⁴到10⁻¹² m⁻²/³)下的系统性能,记录了有无预矫正、有无深度交织编码等情况下的RMS误差变化曲线与误码率性能对比。数据分析显示,无论是在弱湍流还是中等湍流条件下,所提出的预矫正方案均能显著改善波前质量,尤其在湍流变化较快的场景中优势更为明显。而联合编码方案则在所有测试案例中均表现出卓越的抗突发错误能力,即使在模拟的强闪烁条件下,系统也能维持低于10⁻⁹的误码率水平,满足大多数高可靠通信应用的需求。综上所述,本文通过理论分析、算法创新、系统设计与实验验证相结合的方式,系统性地解决了自由空间光通信中由大气湍流引发的关键技术难题,提出的波前预矫正与深度交织编码两大核心技术,不仅在性能上优于传统方法,而且具备良好的可扩展性与工程可行性,为下一代高稳定、高带宽自由空间光通信系统的研发奠定了坚实基础。

module fso_transceiver_top (

input clk_156mhz, // Main system clock

input rst_n, // Active-low reset

input rx_optical_in, // Received optical signal (converted to electrical)

output reg tx_optical_out, // Transmitted optical signal control

output reg [7:0] led_status, // Status indicators

input button_start, // Manual start trigger

output reg phy_tx_p, // High-speed serial output positive

output reg phy_tx_n, // High-speed serial output negative

input phy_rx_p, // High-speed serial input positive

input phy_rx_n // High-speed serial input negative

);

// Clock management

wire clk_10g; // 10Gbps line rate clock

wire clk_125mhz; // 125MHz processing clock

wire clk_62_5mhz; // 62.5MHz auxiliary clock

wire locked;

// Clock generation module

pll_clock_generator pll_inst (

.refclk(clk_156mhz),

.rst(!rst_n),

.outclk_0(clk_10g),

.outclk_1(clk_125mhz),

.outclk_2(clk_62_5mhz),

.locked(locked)

);

// Reset synchronizer

reg [1:0] rst_sync = 2'b11;

always @(posedge clk_125mhz or negedge rst_n) begin

if (!rst_n)

rst_sync <= 2'b11;

else

rst_sync <= {rst_sync[0], 1'b0};

end

wire sys_rst = !rst_sync[1];

// High-speed transceiver interface

wire [63:0] tx_data;

wire tx_valid;

wire [63:0] rx_data;

wire rx_valid;

ten_gig_eth_pcs_pma_0 eth_xcvr (

.tx_clkout(clk_10g),

.rx_recclk(clk_10g),

.dclk(clk_125mhz),

.tx_dv_i(tx_valid),

.tx_data_i(tx_data),

.tx_framing_i(2'b00),

.tx_eop_i(1'b1),

.tx_sop_i(1'b1),

.tx_en_i(1'b1),

.tx_serdes_pll_locked(1'b1),

.tx_p(phy_tx_p),

.tx_n(phy_tx_n),

.rx_p(phy_rx_p),

.rx_n(phy_rx_n),

.rx_dv_o(rx_valid),

.rx_data_o(rx_data),

.rx_framing_o(),

.rx_eop_o(),

.rx_sop_o(),

.rx_err_o(),

.rx_pcs_aligned(),

.rx_pcs_aligned_ack(),

.rx_mf_err(),

.rx_mf_lock(),

.dgate(),

.pcs_reset(sys_rst),

.pma_reset(sys_rst)

);

// Data path control

reg [3:0] state = 0;

reg [15:0] packet_len;

reg [31:0] byte_counter;

wire [7:0] data_in = rx_valid ? rx_data[7:0] : 8'd0;

// Deep interleaver core

reg [7:0] deep_interleaver [0:4095]; // 4K depth interleaver RAM

reg [11:0] wr_addr, rd_addr;

reg [1:0] wr_bank, rd_bank;

reg [7:0] inter_data_out;

always @(posedge clk_125mhz) begin

if (sys_rst) begin

wr_addr <= 0;

wr_bank <= 0;

rd_addr <= 0;

rd_bank <= 0;

end else begin

// Write phase: sequential write to current bank

if (rx_valid) begin

deep_interleaver[{wr_bank, wr_addr}] <= data_in;

if (wr_addr == 1023) begin

wr_addr <= 0;

wr_bank <= wr_bank + 1;

end else

wr_addr <= wr_addr + 1;

end

// Read phase: pseudo-random read from previous bank

rd_addr <= (rd_addr + 17) % 1024; // Prime step for scattering

inter_data_out <= deep_interleaver[{rd_bank, rd_addr}];

if (rd_addr == 1023) begin

rd_bank <= (rd_bank + 1) % 4;

end

end

end

// LDPC encoder (simplified model)

reg [7:0] ldpc_enc_in;

wire [15:0] ldpc_enc_out;

ldpc_encoder ldpc_enc (

.clk(clk_125mhz),

.rst(sys_rst),

.data_in(ldpc_enc_in),

.valid_in(tx_valid),

.encoded_out(ldpc_enc_out)

);

// LDPC decoder

wire [15:0] ldpc_dec_in;

wire [7:0] ldpc_dec_out;

wire dec_valid;

ldpc_decoder ldpc_dec_inst (

.clk(clk_125mhz),

.rst(sys_rst),

.data_in(rx_data[15:0]),

.valid_in(rx_valid),

.decoded_out(ldpc_dec_out),

.valid_out(dec_valid)

);

// Frame builder and parser

reg [63:0] tx_shift_reg;

reg [5:0] tx_bit_cnt;

always @(posedge clk_125mhz) begin

if (sys_rst || !tx_valid) begin

tx_bit_cnt <= 0;

tx_shift_reg <= 0;

end else if (tx_bit_cnt == 0) begin

tx_shift_reg <= {ldpc_enc_out, 48'd0};

tx_bit_cnt <= 16;

end else begin

tx_shift_reg <= {1'b0, tx_shift_reg[63:1]};

tx_bit_cnt <= tx_bit_cnt - 1;

end

tx_data <= tx_shift_reg;

tx_valid <= (tx_bit_cnt > 0);

end

// Status monitoring

always @(posedge clk_62_5mhz) begin

if (!locked)

led_status <= 8'b10101010;

else if (rx_valid)

led_status <= led_status + 1;

else

led_status <= 8'b00000001;

end

如有问题,可以直接沟通

👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇

1965

1965

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?