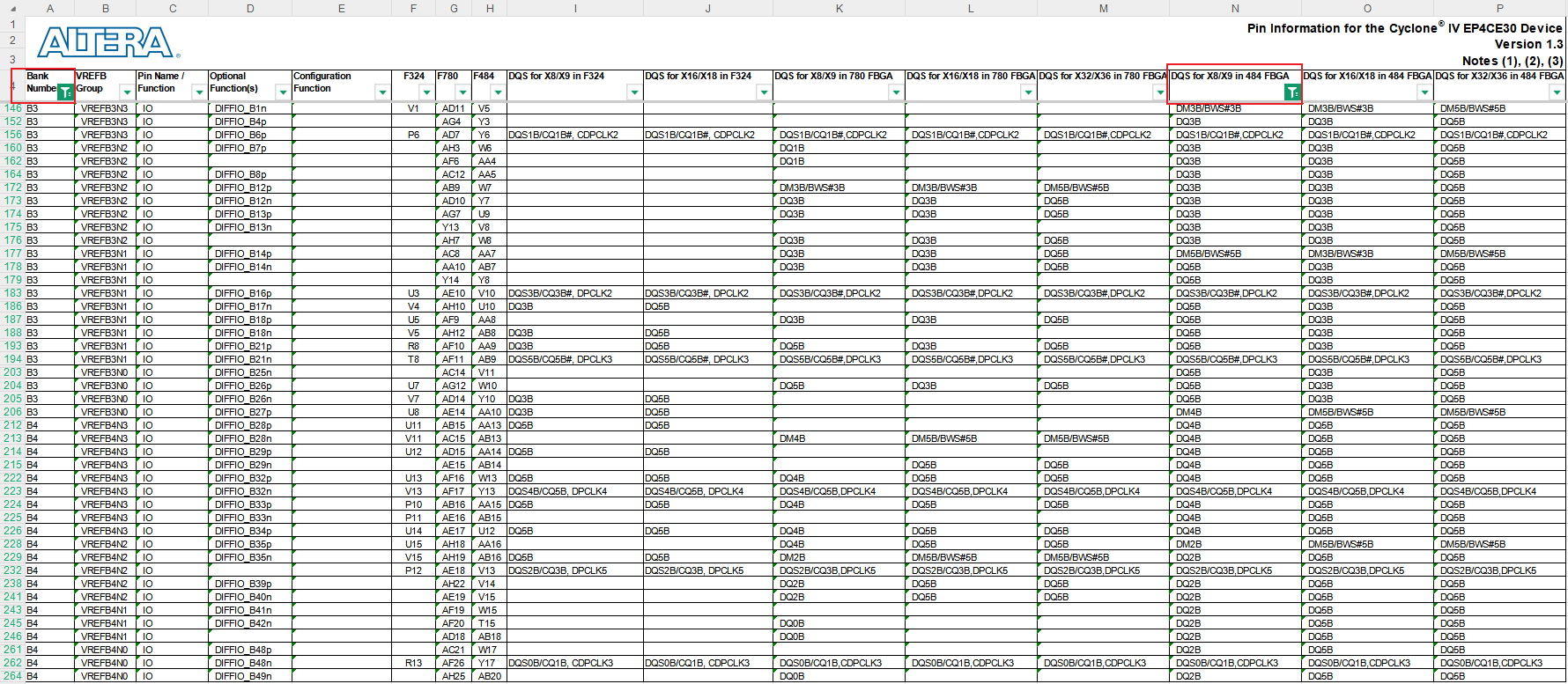

1. 前往官方下载引脚功能表(ep4ce30)

Cyclone® IV EP4CE30 设备的引脚信息 - XLS 格式

2. DDR2 FPGA Bank分配

EP4CE30F23I7N有4块Group,Group1、2、3、4分别位于芯片的左侧、下方、右侧、上方,对应的Bank分别是Bank1、2,Bank3、4,Bank5、6,Bank7、8。

下方、上方Bank(Bank3、4、7、8)为专用高速接口,最高支持200 MHz。

左侧、右侧Bank(Bank1、2、5、6)支持真差分(PPDS, LVDS, mini-LVDS, and RSDS I/O standards)。

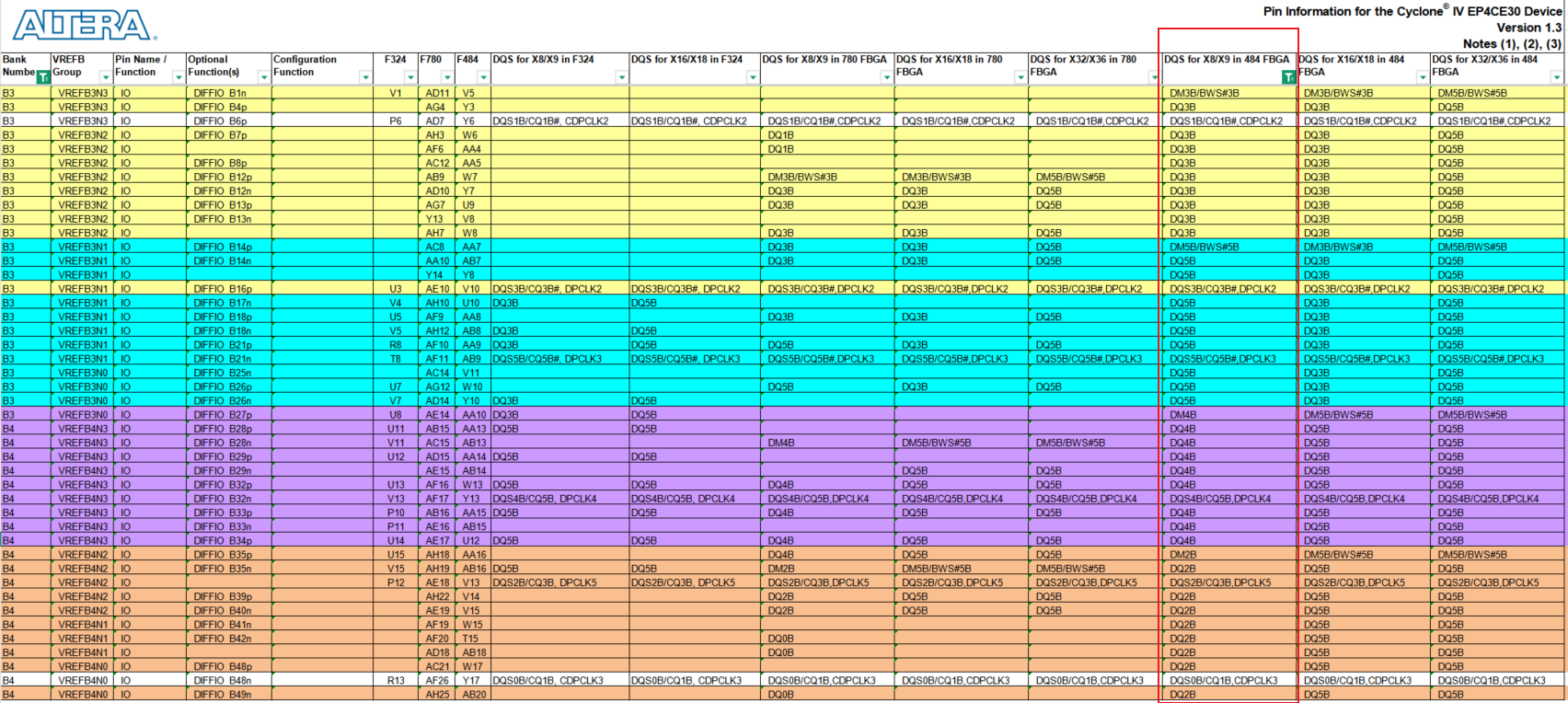

以DDR2分布在Bank3、4为例,Bank Number选择BANK3、4,‘DQS for X8/X9 in 484 FBGA’取消空白项显示

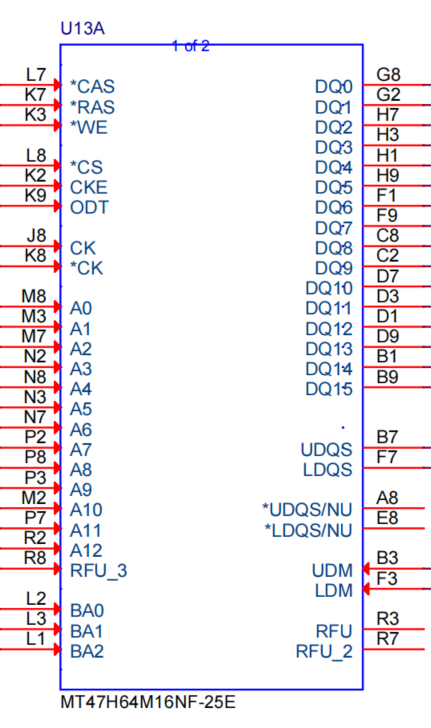

3. 数据组FPGA信号分配

DDR2: DQ[0..7]、LDQS、LDQM为一组,DQ[8..15]、UDQS、UDQM为另一组。

FPGA: DQ、DQS、DM序号相同的既是同组(底纹填充相同的为同一数据组)

DDR2每一组的DQS、QDM、QD必须和FPGA组绑定。QDS、DQM必须分配在FPGA标有DQS、DM的引脚上,DQ必须分配在FPGA标有DQ的引脚上,序号可自由分配。

4. 地址/命令/控制 FPGA信号分配

位于Bank3、4的IO即可。

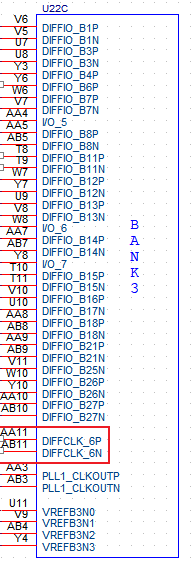

5. 时钟引脚分配

DDR差分时钟建议分配在FPGA专用时钟引脚

也可分配在同Bank中的差分对上(Bank3、4)。

专用时钟引脚对比普通差分对,抖动更低(专用时钟< 50 ps,普通差分对>100 ps),分配在专用时钟引脚可靠性更高,若分配在普通差分对,FPGA需额外占用缓冲/调整逻辑资源。

6. FPGA其他配置

6.1 Bank、VREFB电源配置

FPGA DDR2 SDRAM IO电平SSTL_18,Bank3、4电源配置为1.8V,VREFB配置为0.9V - Bank电源的一半。

6.2 RUP、RUN设置

RUP/RDN 引脚用于配置 片内终端电阻 (OCT) 的校准。

DDR2 接口和其对应的 RUP/RDN 引脚 必须位于同一 I/O Bank 或共享校准模块的 Bank 组,且 VCCIO 电压一致。DDR应用Quartus II不能将RUP/RDN 作用普通 I/O。

RUP2接50Ω到DDR2的VDDQ电压,RUN2接50Ω到GND。

7. 完整的设计参考

下载资源: Intel/Altera FPGA基于Cyclone IV DDR2设计参考

设计参考包含FPGA端、DDR端的电路设计。

8. 官方资料参考

Cyclone® IV 设备手册,第 1 卷,第 6 章:I/O 功能

Cyclone® IV Device Family Pin Connection Guidelines

如果我在 Cyclone 中使用电压参考 I/O 标准...

Cyclone IV FPGA的DDR2硬件设计指南

Cyclone IV FPGA的DDR2硬件设计指南

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?