低级别 SVF JTAG 命令

注释:在 Versal™ 器件上不支持 SVF。

低级别 JTAG 命令允许您扫描多个 FPGA JTAG 链。针对链操作所生成的 SVF 命令使用这些低级别命令来访问链中的

FPGA。

报头数据寄存器 (HDR) 和报头指令寄存器 (HIR)

语法

HDR length [TDI (tdi)] [TDO (tdo)] [MASK (mask)] [SMASK (smask)];

HIR length [TDI (tdi)] [TDO (tdo)] [MASK (mask)] [SMASK (smask)];

目的

指定每次扫描操作前移入的默认报头模式。报头模式用于指定如何使用一组前导位来填充扫描语句,以供容纳位于扫描

路径上超出感兴趣组件范围的器件。

常规信息

报头数据寄存器 (HDR) 用于指定追加到所有后续 SDR 命令开始位置之前的默认报头模式。报头指令寄存器 (HIR) 用于

指定追加到所有后续 SIR 命令开始位置之前的默认报头模式。报头命令具有一组与之相对的报尾命令(TIR 和 TDR),

下一章节中描述了这些报尾命令。可通过将报头长度设置为 0 来移除报头。

报尾数据寄存器 (TDR) 和报尾指令寄存器 (TIR)

语法

TDR length [TDI (tdi)] [TDO (tdo)][MASK (mask)] [SMASK (smask)];

TIR length [TDI (tdi)] [TDO (tdo)][MASK (mask)] [SMASK (smask)];

目的

指定所有后续扫描操作完成后移入的默认报尾模式。报尾模式用于指定如何使用一组尾位元来填充扫描语句,以供容纳

位于扫描路径上的感兴趣组件之后的器件。

常规信息

报尾数据寄存器 (TDR) 用于指定将追加到所有后续 SDR 命令末尾的报尾模式。报尾指令寄存器 (TIR) 用于指定将追加

到所有后续 SIR 命令末尾的默认报尾模式。可通过将报尾长度设置为 0 来移除报尾。

示例

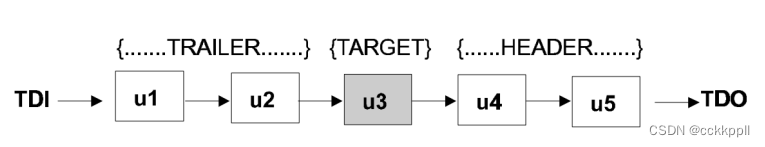

在此示例中,专为 ASIC 开发了 1 个 SVF 文件。随后,将此 ASIC 布局在开发板上作为 u3,如下所示:

如果相应的头尾语句定义为适用于 u3 前后的器件,那么只需对原先为 ASIC 开发的一组 SVF 语句进行少量修改即可复

用。在此示例中,将为器件 u4 和 u5 定义报头模式,并为 u2 和 u1 定义报尾模式。可选参数可按任意顺序指定。每个

可选参数都仅限指定一次。针对 TDI、TDO、MASK 或 SMASK 指定的十六进制字符串值不得大于长度参数所暗示的最

大值。如果未明确指定,那么假定十六进制字符串包含前导零位。

scan_ir_hw

在 hw_jtag 上执行移位 IR。

语法

scan_ir_hw_jtag [-tdi <arg>] [-tdo <arg>] [-mask <arg>] [-smask <arg>] [-

quiet]

[-verbose] <length>

常规信息

scan_ir_hw_jtag 命令用于指定将扫描到 JTG 接口目标指令寄存器中的扫描模式。此命令以 hw_jtag 对象为目

标,该对象是在 JTAG 模式下使用 open_hw_target -jtag_mode 命令打开 hw_target 时创建的。切换至

scan_ir_hw_jtag 命令中指定的扫描模式之前,以 hw_jtag 对象为目标时,最后定义的报头属性 (HIR) 将追加到指定的

数据模式开头位置之前。最后定义的报尾属性 (TIR) 则追加到数据模式的末尾之后。

针对 -tdi、-tdo、-mask 或 -smask 指定的十六进制字符串所表示的位数不能大于 <length> 所指定的最大值。

scan_ir_hw_jtag 命令用于返回十六进制数组,其中包含从 hw_jtag 采集的 TDO 数据,或者如果采集失败,则

返回错误。

示例

以下示例扫描 JTAG 指令寄存器中的 24 位值:

scan_ir_hw_jtag 24

以下示例先向 TDI 发送 24 位值 0x00_0010(LSB 优先),然后采集 TDO 输出、以 0xF3_FFFF 应用掩码,并将返回

的 TDO 值与指定值 tdo 0x81_8181 进行比较。

scan_ir_hw_jtag 24 -tdi 000010 -tdo 818181 -mask F3FFFF -smask 0

scan_dr_hw

在 hw_jtag 上执行移位 DR。

语法

scan_dr_hw_jtag [-tdi <arg>] [-tdo <arg>] [-mask <arg>] [-smask <arg>] [-

quiet]

[-verbose] <length>

常规信息

scan_dr_hw_jtag 命令用于指定将扫描到 JTG 接口目标数据寄存器中的扫描模式。此命令以 hw_jtag 对象为目

标,该对象是在 JTAG 模式下使用 open_hw_target -jtag_mode 命令打开 hw_target 时创建的。切换

scan_dr_hw_jtag 命令中指定的扫描模式之前,以 hw_jtag 对象为目标时,最后定义的报头属性 (HDR) 将追加到

指定的数据模式开头位置之前。最后定义的报尾属性 (TDR) 则追加到数据模式的末尾之后。

scan_dr_hw_jtag 命令用于返回十六进制数组,其中包含从 hw_jtag 采集的 TDO 数据,或者如果采集失败,则返

回错误。

示例

以下示例扫描 JTAG 数据寄存器中的 24 位值:

scan_dr_hw_jtag 24

以下示例先向 TDI 发送 24 位值 0x00_0010(LSB 优先),然后采集数据输出 TDO、以 0xF3_FFFF 应用掩码,并将

TDO 值与指定值 -tdo 0x81_8181 进行比较。

scan_dr_hw_jtag 24 -tdi 000010 -tdo 818181 -mask F3FFFF -smask 0

1120

1120