输出延迟

set_output_delay命令指定输出端口相对于设计接口处的时钟边缘。

当考虑应用板时,此延迟表示以下各项之间的相位差:

1.数据从FPGA的输出封装引脚通过板传播到另一个设备,以及

2.相对基准板时钟。

输出延迟值可以是正的,也可以是负的,这取决于相对的时钟和数据相位在FPGA之外。

使用输出延迟选项

尽管-clock选项在SDC标准中是可选的,但Vivado Design需要它套件工具。

相对时钟可以是设计时钟,也可以是虚拟时钟。

输出延迟命令选项包括:

•最小和最大输出延迟命令选项

•时钟下降输出延迟命令选项

•添加延迟输出延迟命令选项

最小和最大输出延迟命令选项

-min和-max选项为最小延迟分析(保持/删除)和最大延迟分析(设置/恢复)。如果两者都不使用,则输出延迟值适用于两个最小值和最大。

时钟下降输出延迟命令选项

-clock_fall选项指定输出延迟约束应用于定时路径由相对时钟的下降时钟沿捕获。如果没有此选项,Vivado IDE默认情况下仅假设相对时钟的上升沿(在设备外部)。不要将-clock_fall选项与-rise和-fall选项混淆。这些选项指的是数据边缘而不是时钟边缘。

添加延迟输出延迟命令选项

在以下情况下,必须使用-add_delay选项:

•最大输出延迟约束已经存在,并且

•您希望在同一端口上指定第二个最大输出延迟约束。

对于最小输出延迟约束也是如此。此选项通常用于约束相对于一个以上时钟边沿的输出端口,例如DDR中的上升沿和下降沿接口,或者当输出端口连接到使用不同时钟的几个设备时。

set_output_delay命令选项的使用

以下示例介绍了set_output_delay命令选项的典型用法。对于有关输出延迟约束方法的其他信息,请参阅中的此链接《FPGA和SoC的超快设计方法指南》(UG949)。

输出延迟示例一

此示例定义了相对于先前定义的sysClk的min和的输出延迟最大分析。

输出延迟示例二

此示例定义了相对于先前定义的虚拟时钟的输出延迟。

输出延迟示例三

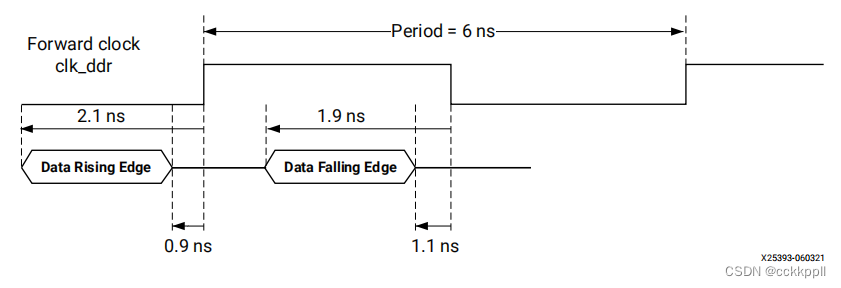

此示例指定相对于DDR时钟的输出延迟值,该值为min的不同值(保持)和最大(设置)分析。

此示例根据的上升沿和下降沿启动的数据创建约束设备外部的clk_ddr时钟,到对两者都敏感的内部触发器的数据输出上升和下降时钟边沿。

输出延迟示例四

此示例指定STARTUPE3内部引脚(UltraScale+设备)对从结构到STARTUPE3的路径进行计时。

本文详细解释了如何在FPGA设计中使用VivadoDesignSuite的`set_output_delay`命令来设定输出延迟,包括最小/最大延迟分析、时钟下降沿约束,以及针对不同时钟边缘和接口的应用实例。

本文详细解释了如何在FPGA设计中使用VivadoDesignSuite的`set_output_delay`命令来设定输出延迟,包括最小/最大延迟分析、时钟下降沿约束,以及针对不同时钟边缘和接口的应用实例。

773

773

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?