参考:

https://www.ti.com.cn/cn/lit/an/zhcaa89d/zhcaa89d.pdf?ts=1755140419109

https://www.analog.com/cn/resources/app-notes/an-960.html

RS485

RS485、TTL与串口协议的关系

许多初学者容易混淆这几者,实际上它们分属通信协议栈的不同层级:

TTL: 是一种电平标准,通常指 0V 和 5V(或 3.3V)的单端信号,这是许多MCU内部UART模块直接输出的电平

RS485: 这是一种物理层标准,定义了差分信号的电气特性。它与TTL最大的区别在于,RS485采用差分信号,而TTL是单端信号

串口协议:是一种数据链路层协议,它定义了数据帧的格式,包括起始位、数据位、校验位和停止位。

简单来说,TTL/RS485 决定了“信号的形态”,而串口协议决定了“信号的内容”。通常,我们会使用 RS485收发器(常见如MAX485等)作为电平转换芯片,将MCU的TTL电平信号转换为RS485的差分信号,以便在总线上进行数据传输

什么是总线?什么是差分?为什么要差分传输?

几个核心概念:

总线(Bus): 总线可以理解为一种公共的通信通道,在总线型网络中,所有设备都共享同一条物理线路。这种架构非常适合多点通信,即一个设备可以在一条线路上与多个设备进行通信

差分信号: 差分信号是一种通过两根线之间的电压差来传输信息的信号。这两根线通常被称为A和B(或H和L)

与此相对的是单端信号,它只使用一根信号线和地线间的电压差来传输信息

为什么要差分传输? 差分信号最大的优点在于其强大的抗干扰能力。在环境中,电磁噪声会同时叠加到A和B两根线上。由于噪声是共模的,接收器只关心A和B之间的电压差,因此这些共模噪声会被有效抵消。这使得差分信号能够在长距离和高噪声环境下实现可靠通信。

RS485中的差分信号

485利用了差分信号的优势,将数据以差分电压的形式进行传输

发送端:RS485收发器根据MCU发出的TTL信号,产生相应的差分电压。例如,当TTL为高电平时,它会让A线的电压高于B线;当TTL为低电平时,它会让B线的电压高于A线

接收端:接收器持续监测A和B两线的电压差。只要电压差超过一个设定的阈值(例如±200mV),它就能判断出是逻辑“1”还是“0”,并将其转换回MCU可以理解的TTL电平

由于差分信号能有效抵御干扰,485总线能够支持长达1200米的通信距离,并且允许多达32个(在某些新规范下更多)设备挂载到同一总线上

RS485、CAN与以太网:物理层与协议层的类比

为了更好地理解485这种分层思想,我们可以将它扩展到其他常见的通信协议中,如CAN和以太网

- RS485

- 物理层: 485差分信号

- 数据链路层: 未定义

- CAN

- 物理层: CAN_H和 CAN_L差分信号。与RS485 类似,它也是通过两根线之间的电压差来传递信号。

- 协议层: 已定义。CAN 不仅仅是一个物理标准,它是一个完整的协议,定义了独特的数据帧格式,包括仲裁段、数据段、CRC 校验等

- 以太网:

- 物理层: 这层定义了信号的电气或光学特性,例如 100Base-TX(双绞线,差分信号)和 100Base-FX(光纤,光信号)

- 数据链路层: 这层定义了MAC帧格式,包括源MAC地址和目的MAC地址。这层还负责访问控制,决定哪个设备可以在什么时候使用物理介质

收发器

485收发器是一种专用芯片,它的核心功能是作为MCU和RS485总线之间的电平转换器和驱动器

电平转换: MCU的UART接口输出的是TTL 电平(例如 0V 和 3.3V/5V),而 485总线需要的是差分信号。收发器就负责将单端TTL信号“翻译”成差分信号,反之亦然

总线驱动: 收发器内部包含强大的驱动器,能够输出足够的电流和电压来驱动总线,确保信号在传输过程中保持其完整性

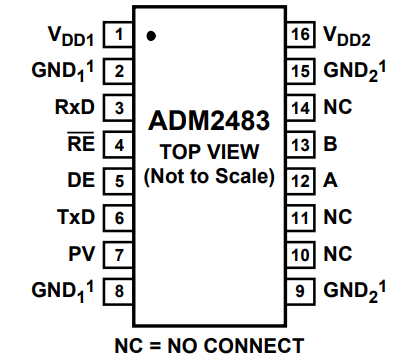

一个典型的485 收发器会有四对主要引脚,用于和单片机以及总线进行连接

-

与 MCU 连接:

- DI (Driver Input): 输入引脚,将单片机的TXD引脚连接到这里,当单片机要发送数据时,它会通过 TXD向DI输入TTL 电平信号

- RO (Receiver Output): 输出引脚,将单片机的RXD引脚连接到这里。收发器从总线上接收到差分信号后,会将其转换成TTL电平,并通过RO输出给单片机的RXD

-

与 RS485 总线连接:

- A/B: RS485 差分总线引脚,这两个引脚直接连接到RS485的通信总线上,收发器通过A和B之间的电压差进行数据的发送和接收

DIR控制引脚

DIR控制引脚是485收发器的核心,尤其是在半双工(Half-Duplex)模式下

半双工意味着总线在同一时间只能发送或接收数据,不能同时进行。为了避免多个设备同时向总线发送数据造成冲突,每个收发器都必须能够被使能(Enable)或禁用(Disable),这就是DIR引脚的作用

-

当DIR为高电平(逻辑1)时:

收发器的发送器被使能。它会根据DI引脚上的TTL信号,将数据发送到A/B总线上

同时,接收器通常会被禁用,或者在某些芯片中,其输出会处于高阻态,避免自己的发送信号“回环”到单片机的RXD引脚 -

当DIR为低电平(逻辑0)时:

收发器的发送器被禁用,进入高阻态,从而释放对总线的控制权

接收器被使能,开始监听A/B总线上的差分信号,并将接收到的数据通过RO引脚输出给单片机。 -

如何控制 DIR 引脚?

通常,DIR引脚由单片机的一个GPIO引脚控制。需要严格控制这个GPIO引脚的电平,以实现正确的收发时序:

发送前: 将DIR引脚拉高

发送数据: 单片机通过TXD发送数据

发送完成: 等待最后一个数据位发送完毕后,将 DIR 引脚拉低,禁用发送器,并使能接收器,从而可以开始接收其他设备发来的数据

以stm32 HAL库为例

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

293

293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?