1.下列陈述中正确的是 ( ) 。

A.在DMA周期内,CPU不能执行程序

B.中断发生时,CPU首先执行入栈指令将程序计数器内容保护起来

C.DMA传送方式中,DMA控制器每传送一个数据就窃取一个指令周期

D.输入输出操作的最终目的是要实现 CPU与外设之间的数据传输

result:

D

2.执行部件接受微命令后所进行的操作叫做 ( ) 。

A.微命令

B.微操作

C.微指令

D.微程序

result:

B

3.SRAM存储器的存储元是一个触发器,它具有 ( )个稳定的状态。

A.1

B.2

C.3

D.0

result:

B

4.主存储器和CPU之间增加Cache的目的是( )。

A.解决CPU和主存之间的速度不匹配问题

B.扩大存储器容量

C.扩大CPU中通用寄存器的数量

D.增加CPU速度

result:

A

5.( ) 是构成计算机系统的骨架,是多个系统部件之间进行数据传送的公共通路。

A.数据总线

B.计算总线

C.系统总线

D.存储总线

result:

C

6.把执行指令的一段时间叫做( ) 。

A.执行周期

B.取指周期

C.读周期

D.写周期

result:

A

7.中央处理器不包括( )。

A.主存

B.控制器

C.运算器

D.寄存器

result:

A

8.每一个基本操作对应一条( )。

A.命令

B.指令

C.口令

D.代码

result:

B

9.每个存储单元都有编号,称为( )。

A.存储单元

B.地址

C.数据

D.信号

result:

B

10.在计算机里,相当于算盘功能的部件,称为( )。

A.存储器

B.运算器

C.控制器

D.适配器

result:

B

11.系统总线中控制总线的功能是( )。

A.提供数据信号

B.提供主存、I/O接口设备的控制信号和响应信号

C.提供时序信号

D.提供主存、I/O接口设备的响应信号

result:

B

12.在此处输入题干部分的内容

A.选项一

B.选项二

C.选项三

D.选项四

result:

A

13.若存储器按机器字进行编制,则存储单元是指( )。

A.存放一个二进制信息位的存储元

B.存放一个机器字的所有存储元集合

C.存放一个字节的所有存储元集合

D.存放两个字节的所有存储元集合

result:

B

14.在CPU中保存当前正在执行的指令的寄存器是( )。

A.程序计数器(PC)

B.地址寄存器(AR)

C.指令寄存器(IR)

D.通用寄存器

result:

C

15.操作数放在主存储器中,而操作数的地址放在某一通用寄存器中,指令的地址码部分给出的是该通用寄存器的编号,此种是( )寻址。

A.直接

B.间接

C.寄存器

D.寄存器间接

result:

D

解析:地址码在存的是地址,地址指向数据(此为间址),地址是寄存器的地址,所以是寄存器间址

16.在定点运算器中,无论采用双符号位还是单符号位,必须有( ),它一般用( )来实现。

A.译码电路,与非门

B.编码电路,或非门

C.溢出判断电路,异或门

D.移位电路,与或非门

result:

C

17.运算器虽有很多部件组成,但核心部分是( )。

A 、数据总线 B、算术逻辑运算单元

C 、多路开关 D、通用寄存器

result:

B

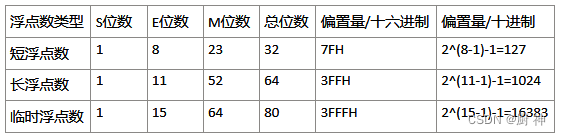

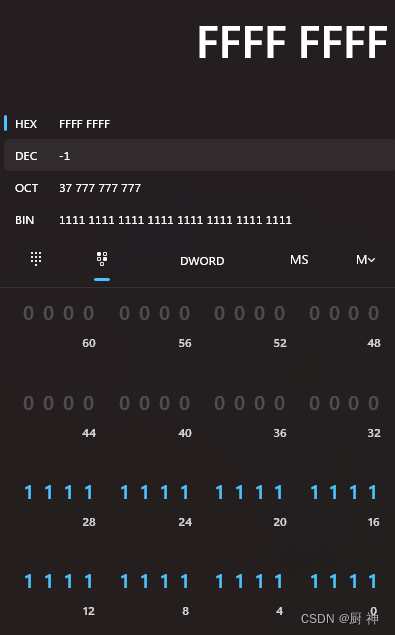

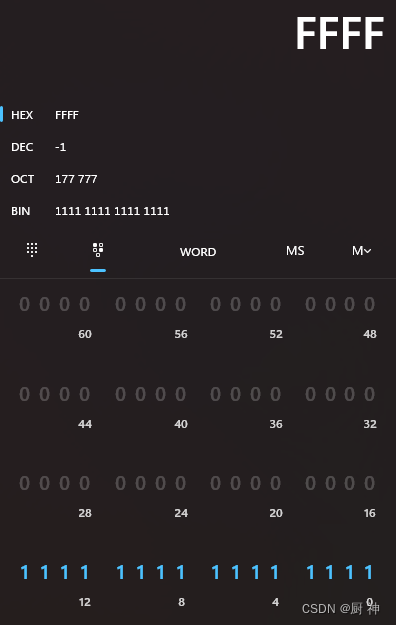

18.十进制数-35的32位浮点数IEEE754代码为( )

A.11000010000011000000000000000000

B.01000010000011000000000000000000

C.01100000101000000000000000000000

D.11000000101000000000000000000000

result:

A

解析:

系统学习来源:尚硅谷-计算机组成原理-IEEE754

IEEE754代码包括三部分:符号位S、阶码E、尾数M (符号+指数+小数)

- 快速方法:负数(第一位为1)+尾数的最后两位为11(35=32+2+1,所以100011)

- 详细方法:

步骤:

1. 确定符号位S:正数为0,负数为1

2. 数值部分转为二进制:35的二进制为0010 0011

3. 将0010 0011规格化为:1.000011 * 105

4. 得到指数为5,尾数为00011

5. 将指数部分5变成二进制补码:

方法一:5的二进制为101,8位阶码为:101+1000 0000-1=1000 0101

方法二:5+127=132=,132的二进制为1000 0100

6. 组合SEM :11000 010000011 ,凑够32位,尾数后面补0

7. 得到11000010000011000000000000000000

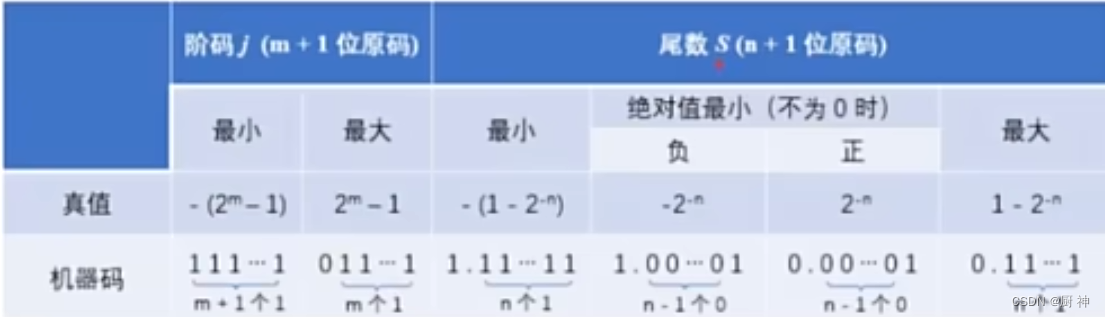

19.某机字长32位,其中1位符号位,31位表示尾数。若用定点小数表示,则最大正小数为( )。

A.+(1 – 2-32)

B.+(1 – 2-31)

C.2-32

D.2-31

result:

B

尚硅谷《计算机组成原理

+(1-2(-31))

0.11111… 31个1

20.计算机的发展大致经历了五代变化,其中第四代是( )年的( )计算机为代表。

A.1946-1957,电子管

B.1958-1964,晶体管

C.1965-1971,中小规模集成电路

D.1972-1990,大规模和超大规模集成电路

result:

D

21.PCI总线是当前实用的总线,是一个高带宽且与处理器无关的标准总线,又是重要的层次总线。

result:

true

22.总线仲裁使用串联的方式进行查询,称为链式查询方式。

result:

true

23.衡量总线性能的重要指标是总线带宽。

result:

true

24.偏移寻址是直接寻址和寄存器间接寻址方式结合。

result:

true

25.运算器、存储器、外围设备可以称为控制部件。

result:

false

26.中、低速I/O设备之间互相连接的总线,称为系统总线。

result:

false

27.计算机操作的最小时间单位是时钟周期。

result:

true

28.对各种操作实施时间上的定时,称为时间控制。

result:

true

29.指令系统的性能要求是完备性,有效性,规整性。

result:

true

30.cache不命中时,CPU从主存中读取数据。

result:

true

31.在此处输入题干部分的内容

result:

true

32.程序计数器PC属于CPU中的运算器部件。

result:

false

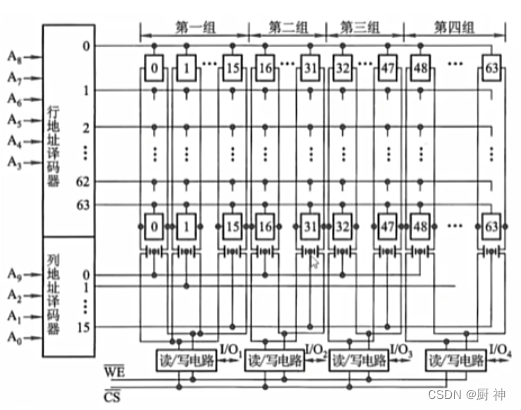

33.16Kx8bit的SRAM中,地址线有15条。

result:

false

解析:

完整学习:尚硅谷-计算机组成-SRAM

16KB=214B 8bit就是,分为8组,分8根给列地址译码器 一共14个地址线,8行列地址译码器 和 6根行地址译码器

所以地址线为14根

(其实地址线15根也可以,只能多不能少,题目应该加一个”最少地址线“)

34.E2PROM属于紫外光可擦除可编程只读存储器。

result:

false

解析: 电可擦可编程只读存储器。

EPROM才是紫外光可擦除可编程只读存储器

35.双端口存储器中,当两个端口同时存取存储器同一存储单元时,不会发生读写冲突。

result:

false

36.DRAM存储器的存储元是双稳态触发器。

result:

false

DRAM存储器的存储元是由一个MOS晶体管和电容组成的记忆电路

双稳态触发器所构成的存储元,属于SRAM类型的存储器存储元

37.计算机系统中,传输信息采用三种方式:串行传送、并行传送和分时传送。

result:

true

38.计算机操作的最小时间单位是时钟周期。

result:

true

39.周期挪用方式常用于DMA方式的输入/输出中。

result:

true

40.CPU内部连接各个寄存器及运算部件之间的总线,称为内部总线。

result:

true

41.分布式仲裁不需要集中的总线仲裁器。

result:

true

42.移码就是在真值X上加上一个常数,通常这个常数取2n,相当于X在数轴上向正方向偏移了若干单位,这就是“移码”一词的由来。移码常用来表示浮点数的 ( ) ,只用于定点整数。

result:

阶码

43.( ) 是计算机内部存储,加工处理、检索、传输汉字时所用的统一编码。

result:

汉字内码

44 ( ) 是指指令的地址码部分给出的是某一通用寄存器的编号,操作数存放在对应的寄存器中。

result:

寄存器寻址

- ( ) 是指指令中的地址字段,不是操作数地址,而是操作数本身。

result:

立即寻址

46.( ) 在具有层次结构存储器的计算机系统中,自动实现部分装入和部分替换功能,能从逻辑上为用户提供一个比物理贮存容量大得多,可寻址的“主存储器”。

result:

虚拟存储器

47.( ) 一种特殊功能的处理器,有自己的指令和程序专门负责数据输入输出控制,而CPU将“传输控制”的功能下放给通道后,只负责“数据处理”。

result:

通道

48.( ) 是一种完全由硬件执行I/O交接的工作方式。这种方式既能响应随机发生的服务请求,又可省去中断处理的开销。

result:

直接内存访问方式 (或DMA)

49.CPU的工作节拍受主时钟控制,主时钟不断产生固定频率的时钟,主时钟的频率(f)叫CPU的 ( ) 。度量单位是MHz(兆赫兹)、GHz(吉赫兹),主频的倒数称为CPU的 ( ) 。

result:

主频,时钟周期

50.( ) 指系统在单位时间内处理信息的数量,单位字节/秒(B/S)。

result:

吞吐量

51.奥运精神是 ( ) 、 ( ) 、 ( ) 。

result:

更快,更高,更强

52.在中断服务中,开中断的目的是允许 ( ) 。

result:

多级中断

53.集中式总线仲裁分为链式查询方式、计数器定时查询方式和 ( ) 方式。

result:

独立请求

54.就取得操作数的速度而言, ( ) 寻址方式的速度最快;MOV AX,BX指令为RR型指令,其指令周期包含 ( ) 个CPU周期。

result:

立即,2

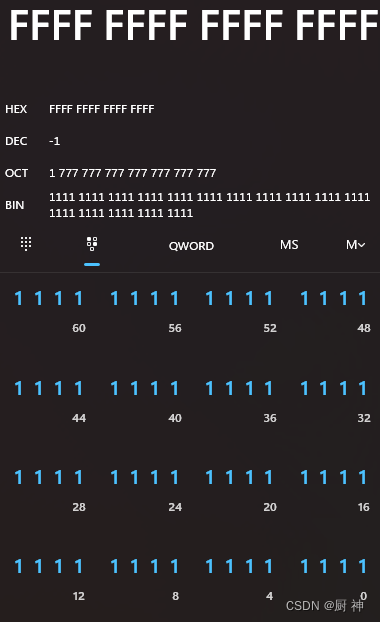

55.某机器字长32位,其存储容量为4GB,若按双字进行编址,它的寻址范围是 ( ) 。

result:

0.5G或512M

4GB=4 x 1024 x 1024 x 1024字节=232

机器字长为32位,字长32位表示每字有32位,有两个字,也就是64位

因为1b=8B,所以是一次64/8=8字节

4GB/8B=0.5G

byte字节,word字,dword双字

1dword=2word,1word=2byte=2B

四字qword:64位(1qword=64b=8B)

双字dword:32位(1dowd=32b=4B)

双字的大小通常是32位(4个字节)

字word:16位(1word=16b=2B)

早在十六位机时代,人们将字长定义为16位。后来出现32位机,有人便将32位称之为双字。等出现64位机之后,又将其称之为四字。这成为一种约定俗成的叫法,与早先对字长的定义无关了。

byte:8位(1B=8b)

56.一条指令是由 ( ) 和 ( ) 两部分构成的。

result:

操作码,地址码

57.一个组相联cache由64个行组成,每组4行。主存储器包含4K个块,每块128字。则表示的内存地址格式中标记= ( ) 位,组号= ( ) 位,字号= ( ) 位。

result:

8,4,7

组相联就是直接映射和全相联映射两种方式结合起来

组和组之间用直接映射,组内用全相联映射。

每组四行代表组内有4路,且一共64行,表示一共64/4=16组,24=16,一共4位

4K个块:4K=4*1024=212,主存块共有212个

每块128B:2^7^=128得到字号为7位

组号需要4位表示

因为有4位可以表示cache缓存内地址了(组间直接映射),不需要标记里面再记录了,所以标记只需要12-4=8

58.计算机除法运算中,常用不恢复余数法,又称 ( ) 。

result:

加减交替法

59.计算机中常用的数据表示格式有两种,一是 ( ) ,二是 ( ) 。

result:

定点格式,浮点格式

60.电子计算机从总体上可分为( ) 和 ( ) 两大类。

result:

模拟电子计算机,数字电子计算机

61.若用32K8位的E2PROM芯片,设计组成128K16位的只读存储器,问:

(1)数据寄存器多少位?

(2)地址寄存器多少位?

(3)共需多少个E2PROM芯片?

(4)为解决存储器速度和容量问题,主要都采取什么技术和方法?

result:

(1)数据寄存器16位。

(2)128K=217

所以地址寄存器有17位。

(3)128/32*16/8 =8

共需8个E2PROM芯片。

(4)芯片技术:提高单个芯片的访问速度。例:突发传输技术、同步DRAM技术、CDRAM技术等。

结构技术:改进存储器与CPU直接的连接方式。例:多端口技术、多体交叉技术。

系统结构技术:从整个存储系统的角度,采用分层存储结构解决访问速度问题。例:增加cache、采用虚拟存储器。

62.CPU执行一段程序时,cache完成存取的次数为1900次,主存完成存取的次数为100次,已知cache存取周期为50ns,主存存取周期为250ns。

(1)求cache的命中率。

(2)求系统的平均访问时间。

(3)求系统的访问效率。

result:

命中率:h=Nc/=1900/2000=0.95

平均访问时间:ta = 0.95×50+(100/2000)×250 = 0.95*50+(1-0.95)*250=60ns

效率:e=访问Cache的时间/平均访问时间=50/60=83.3%

63.x=-1100 、y=-1000 。

(1)求x的补码、y的补码。

(2)x+y的值。

(3)判断是否溢出。

result:

(1)[x]补=10100

[y]补=11000

(2) [x+y]补=[x]补+[y]补=10 1100=0 1100=[4]补

(3)

方法一: 两个负数相加为正数,溢出,负溢出

方法二:x=-12,y=-8,x+y=-20,超过n=4能表示的最小负数-16,负溢出

方法三:C1=最高数位相加的进位=0,Cs=符号位产生进位=1,0异或1=1,溢出,且两个负数相加为负溢出

方法四:使用双符号位 :11,0100+11,1000=10,1100=[x+y]补,两个符号位结果为10,负溢出

解析:

尚硅谷-溢出判断方法

无符号位判断溢出:将加法为0,减法为1的操作 和 计算结果的进位 异或即可

有符号位判断溢出:

- 双符号位方法:符号位表示为00为正数,11为负数,10为负溢出,01为正溢出

- 一位符号位方法:符号位产生的进位 异或 最高数位相加的进位

- 符号判断:正数相加为负数,正溢出,负数相加为正数,负溢出

- 用范围判断:两个数相加或相减,超过了数的表示范围

64.要求完成下面的数制专换。

(1)(10110)2求其对应的10进制。

(2)将二进制数1100111转化为16进制数。

(3)将十六进制数A6转化为二进制数。

result:

(1)22

(2)67

(3)1010 0110

65.根据操作数所在位置,指出其寻址方式:

(1)操作数在寄存器中;

(2)操作数地址在寄存器;

(3)操作数在指令中;

(4)操作数地址(主存)在指令中;

(5)操作数的地址为某一寄存器内容与位移量之和。

result:

寄存器寻址

寄存器间接寻址

立即寻址

直接寻址

相对寻址、基址寻址、变址寻址

解析:

寻址方式分为指令寻址和数据寻址两大类:

- 指令寻址:

- 顺序寻址:PC+1,程序计数器自动形成下一条指令的地址

- 跳跃寻址:转移类指令,下一条指令地址不是PC给出,而是本条指令给出的

- 数据寻址:

- 立即寻址:地址码==操作数本身

- 直接寻址:地址码==操作数在内存中的地址

- 间接寻址:地址码==操作数地址所在的存储单元的地址,(地址的地址)

- 隐含寻址:地址码==无,默认隐含在某个寄存器(ACC)中

- 寄存器寻址:地址码==寄存器编号,指令在执行时所需要的操作数在寄存器中

- 寄存器间接寻址:地址码==寄存器编号所在地址,指令在执行时所需要的操作数在寄存器指向的内存地址中

- 偏移寻址:

- 基址寻址:基址寻址器BR,BR内容(基地址)+指令的形式地址=操作数有效地址(程序或数据分配存储空间)

- 变址寻址:变址寄存器IX,IX内容(基地址)+指令中的形式地址=操作数有效地址(数组问题)

- 相对寻址:程序计数器PC,PC内容+指令中的形式地址=操作数的有效地址(用于转移指令)

- 堆栈寻址:只用堆栈指针SP(也可以CPU寄存器作为SP)指出栈顶地址,操作数只能在栈顶指针指向的存储单元存取(是隐含地址(操作数地址隐含在SP中),也是寄存器间接寻址(将SP看作存放有效地址的寄存器)),寄存器组实现堆栈为硬堆栈,主存中的一部分空间作为堆栈为软堆栈

注意:

基址寄存器面向操作系统,内容由操作系统或管理程序确定,程序执行过程中不可变,指令字中的A可变

变址寄存器面向用户设定,程序执行过程中其值可变,指令字中的A不可变(用于数组)

66.假设某机器有 80 条指令,平均每条指令由 4 条微指令组成,其中有一条取指微指令是所有指令公用的。 已知微指令长度为 32 位。

(1)请估算控制存储器容量。

(2)微程序控制器的基本思想是什么?

(3)画出微程序逻辑框图。

result:

80条指令,平均每条指令由4条微指令组成,其中有一条公用微指令,所以总微指令条数为80*(4-1)+1=241条微指令。

每条微指令32位,所以控存容量为:241*32/8=964 B

仿照解题程序的方法,把操作控制信号编制成微指令,存放到只读存储器里,运行时,一条一条地读出这些微指令,从而产生全机所需要的各种操作控制信号,使相应部件执行规定的操作。从上述可以看出,微程序设计技术是用软件方法来设计硬件的技术。

67.x=+10111,y=+11011,用变形补码计算x-y,并指出运算结果是否溢出。

[x]原=0010111,[y]原=0011011(2分)

result:

则[x]补=0010111、 [-y]补=1100101

变形补码加法结果为1111100,由于符号位为11,所以结果无溢出。

68.什么是机器字长、指令字长、存储字长?

result:

机器字长是指CPU一次能处理数据的位数。

指令字长是指计算机指令中二进制代码的位数。

存储字长是指存储单元中存放二进制代码的位数。

69.简述什么是间接寻址、直接寻址、寄存器寻址?

result:

间接寻址:指令的地址码部分给出的地址A不是操作数的地址,而是存放操作数地址的主存单元的地址,简称操作数地址的地址。

直接寻址:指令中地址码字段给出的地址就是操作数的有效地址。

寄存器寻址:指令的地址码部分给出的是某一通用寄存器的编号,操作数存放在对应的寄存器中。

70.接口也称适配器,是CPU、主存和外设之间通过总线进行连接的标准化逻辑部件,请简述其典型功能。

result:

控制:接口模块靠指令信息来控制外围设备的动作,如启动、关闭设备等。

缓冲:作为外围设备与计算机系统的缓冲器,以补尝速度差。

状态:监视外围设备的工作状态并保存。如“忙”、“错误”等 ,供CPU询问外围设备时分析使用。

转换:完成数据转换。如并-串或串-并,以保证数据在CPU和外设之间正确传送。

整理:完成一些特别功能。如:修改字记数器或当前内存地址寄存器。

程序中断:当外设向CPU请求某种动作时,接口模块即向CPU发送一个中断请求信号。

71.简述DMA方式的特点。

result:

DMA方式以随机请求的方式实现主存与 I/O设备的快速数据传送。

若不存在访存冲突,DMA和CPU互不影响。

DMA只能实现简单数据传送,难以识别和处理复杂事态。

能够进行连续批量的数据交换,适合连接高速I/O设备。

72.简述总线的基本概念。

result:

总线是构成计算机系统的互联机构,是多个系统功能部件之间进行数据传送的公共通路。

73.简述什么是机器语言、汇编语言、高级语言?

result:

机器语言是一种用二进制表示的计算机语言,机器可以直接执行用机器语言编写的程序。

汇编语言是一种用助记符表示的与机器语言一一对应的语言,用汇编语言编写的程序需要经过汇编后才能执行。

高级语言是一种接近人类自然语言的与计算机结构无关的语言,用高级语言编写的程序要经过解释和编译才能执行。

74.简述I/O接口与外设之间数传送的三种方式。

result:

与速度极慢或简单的外设之间采用无条件传送方式。

与慢速或中速外设之间采用应答方式。

与高速外设之间采用同步传送方式。

75.中央处理器有哪些基本功能?

result:

指令控制:即对程序运行的控制,保证指令序列执行结果的正确性。

操作控制:即指令内操作步骤的控制,控制操作步骤的实施。

数据运算:即对数据进行算术运算和逻辑运算。

异常处理和中断处理:如处理运算中的溢出等错误情况以及处理外部设备的服务请求等。

import requests

url="https://homeworkapi.ulearning.cn/quiz/homework/stu/record/10521625/answer/record"

response=requests.get(url,headers={"Authorization":"FAB3EE44BFDACBB4D22D9F54E059BAF0"})

with open("answer.txt",'w') as f:

f.write(response.text)

result=response.json()

print(result["result"])

for i in result["result"]:

if isinstance(i,dict):

print(i)

all=[]

index=1

choice_index=["A.","B.","C.","D."]

for i in result["result"]["answerRecordDTOList"]:

print(i)

if isinstance(i,dict):

title=i.get("title","")

correctAnswer=",".join(i.get("correctAnswer",""))

choiceIItemLists=i.get("choiceItemList",[])

choices=[]

if(choiceIItemLists is not None):

choice_i=0

for choice in choiceIItemLists:

choices.append(choice_index[choice_i]+choice.get("title","").replace("<br/>","")+"\n")

choice_i=choice_i+1

print(title)

all.append(f"""{index}.{title}\n{"".join(choices)}\n result:\n{correctAnswer} """)

index=index+1

with open("answer_all.txt","w") as f:

f.write("\n".join(all))

5257

5257

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?