1.如果在vivado里面的一个工程,调用了两个不同的 自定义IP(举例模块A和B) ,但这两个IP分别调用了 同一个 子代码(举例 test.v),则需要注意如下问题:如果在 A 和 B 里面, 这两个test.v 完全一致的话,那编译的时候不存在问题,也不会报 critical waring ;如果不巧,A B 模块都没想到对方模块会和自己有一个同样名字的子代码,两个模块下这个子代码的功能还不一样,那在编译时,后面编译的模块的 test.v会将前面编译完成的模块的test.v文件覆盖掉,并报critical waring 。

2.关于位宽的定义问题。之前在一个ram管理模块的代码中,将位宽(通过上层paramater参数传递)定义的都刚刚好不多不少,使用Modelsim 和 Vivado2018.2的自带仿真时,结果都正确。但是上板测试时,发现工具将cnt综合成有符号数,相当于致使位宽少了一个bit,后面解决的方法是,将通过参数传递的位宽加多一个bit。暂未弄清楚出现这个问题的原因是什么(可能是编译策略的问题???目前不清楚)。

3.在进行逻辑设计时,不是在top层的 IO port ,尽量不要使用 inout定义。原因是,如果定义普通的内部使用的输入输出信号,使用了inout定义的话,那工具在布局布线的时候,会将这个信号布局到芯片边缘的 IO port 上 ,因为只有在 IO Bank 哪里才有 inout 的资源。

4.当serdes不稳定(例如jesd204b偶尔desync),考虑:电源、时钟、serdes周边bank IO是否有电平切换频繁导致影响。

5.在使用ADI脚本封装IP的时候,如果改动IP的非接口代码,可以直接在vivado里面updata IP, 如果改动了IP的接口代码(例如位宽,接口协议等,),需要将IP清空(make clean),重新创建(make)

6.vivado可以将block_design的设计导出成tcl;一般情况下,导出来的tcl可以直接来用,sourc design.tcl 还原block_desgin的设计。但是有时候有些情况要特别注意,当block_desgin里面调用了xilinx的reset IP时,这颗IP的有些自动适配的只读设置,导出时有可能无法在tcl中体现(例如接口ext_reset_in的属性设置),最终导致source design.tcl 时,没办法1:1的还原设计。当发现还原后的工程无法启动,或者无法工作,要多检查时钟复位这些模块;

7.在vivado中定义parameter时,不可使用逻辑赋值,只能直接赋值。例如定义parameter A=1; parameter B=2;不能定义parameter C=A+B;这样编译出来的C并不是3,而是1;但是使用modelsim仿真,得出的是3;这个可能是编译器的差异导致;

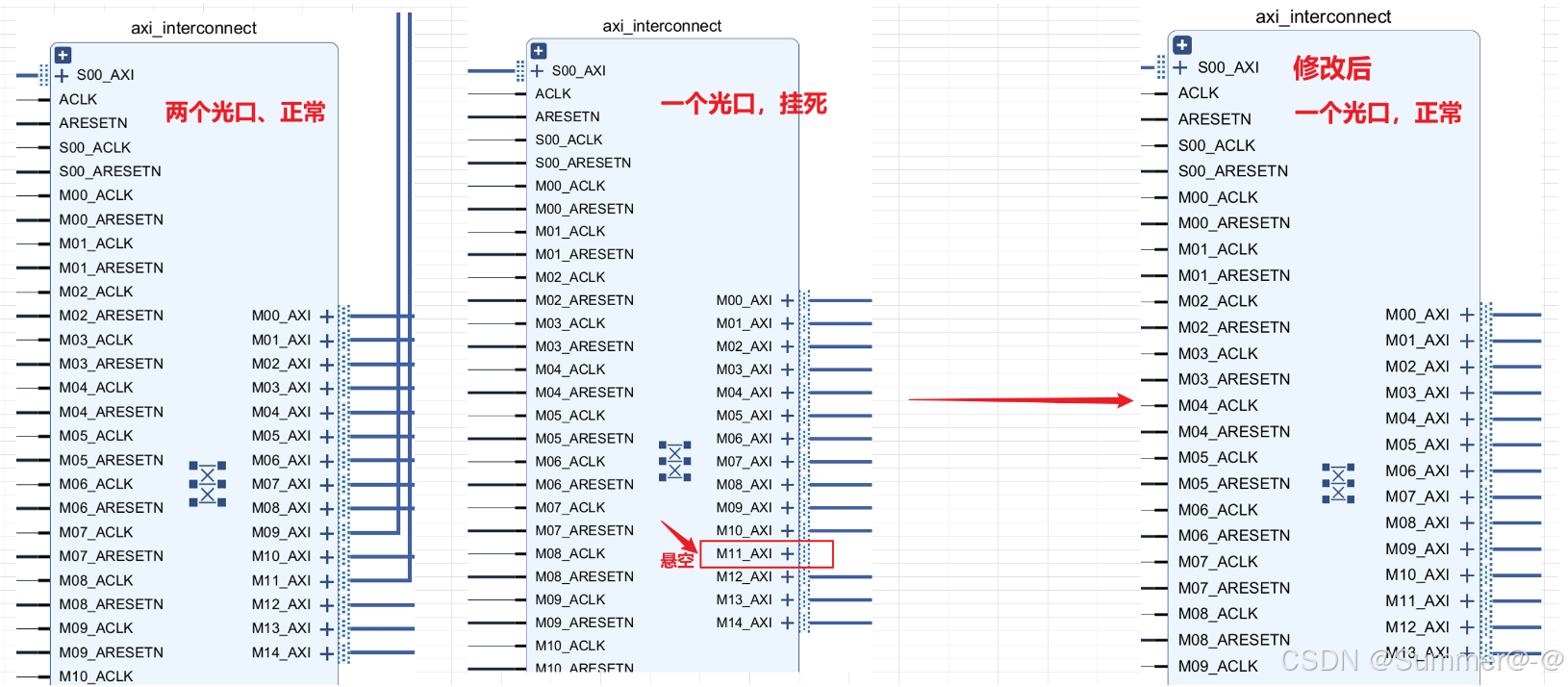

8.在调用axi_interconnect IP(vivado 2022.2)时,如果有接口悬空,那可能会出现系统挂死的现象,不过是可能会出现,不是一定;但是如果总线上有很复杂繁多的总线通信,例如DMA ,DPD等,则挂死的概率很大;

6014

6014

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?