8.3.2 8B/10B PCS

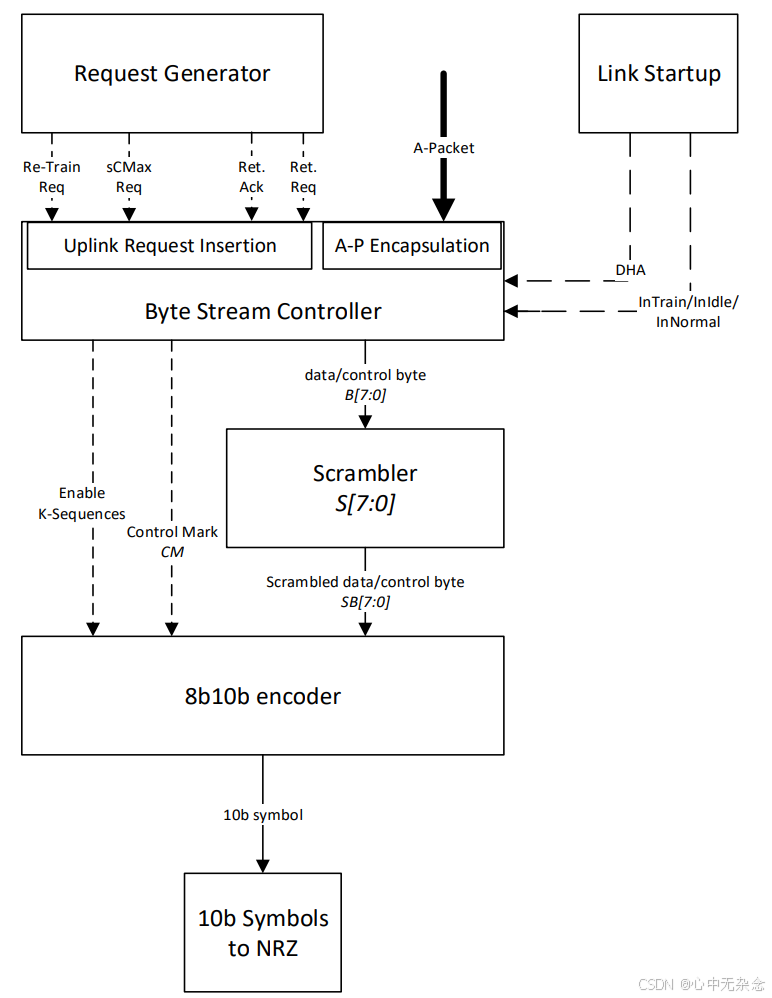

8B/10B PCS(图59)在上行链路上使用,用于所有档位,用于两个配置。它用于下行链路/反向下行链路的档位#1和#2。对于配置1,档位#3的下行链路也使用8B/10B PCS。

8B/10B TX PCS封装A包,使用‘ A-P封装’模块(参见章节8.3.2.8.6),将A包逐字节转换为10B Symbool(8B/10B编码),然后通过链路逐bit发送(LSB到MSB)。

当在上行链路上操作时,8B/10B TX PCS还使用“上行请求插入”模块将几个Requests/ Ack-Indications插入字节流中。当在反向下行链路上发送Requests/ Ack-Indications时,它们应使用具有类似的格式和A包包头的A包封装,详见章节8.2.3.3。

8B/10B TX PCS有三种工作模式:

1. Training Mode

在链路启动时,Training模式用于使接收端同步到10b word边界并锁定其解码器。

2.Idle Mode

在链路启动期间,从Training模式移出的中间模式只传输加扰器内容(数据为零)。

3.Normal Mode

正常运行数据包传输。

图59 PCS框图

8.3.2.1 10b Symbol到NRZ映射

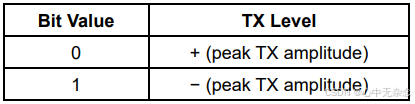

8B/10B Symbol的表示法是“abcdeifghj”,其中“a”位首先传输。每个比特按表45传输。

表45 NRZ电平映射

8.3.2.2 8B/10B 编码

所有传输的信息均应根据附件B中指定的数据和控制符号分配进行8B/10B编码。

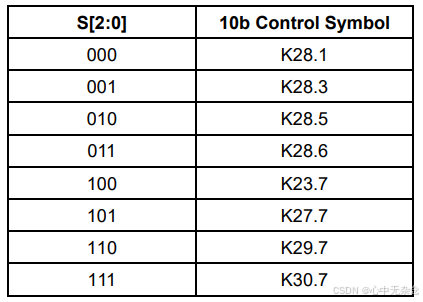

在对一个数据/控制字节(CM=0)进行编码时,需要传输10b数据Symbol。

在编码控制标志(control mark)(CM=1)时,将B[7:0]置零,以保证SB[7:0]反映扰码器内容,并根据当前扰码器输出的3个LSB SB[2:0]发送10b控制符号,如表46所示。

表46 8B/10B 编码

8.3.2.3 上行/反向下行加扰器

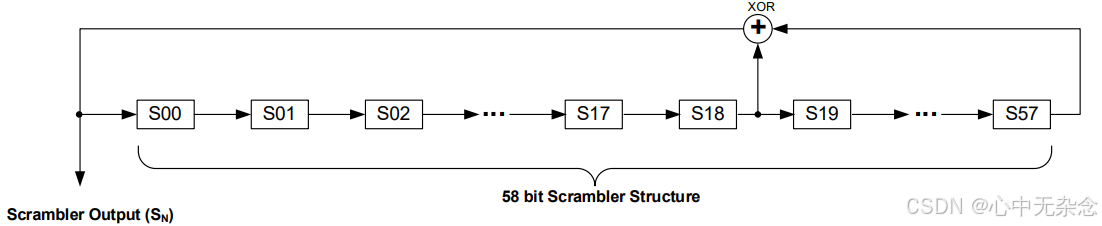

当使用8B/10B PCS实现上行/反向下行链路时,加扰器应使用图60所示的LFSR 实现。

图60 上行/反向下行TX加扰器LFSR

图60的LFSR也可以表示为多项式:

![]()

Note:

如果多项式和图之间的解释有任何差异,则将图视为正确的。

加扰器的58位种子应由TX PCS初始化为具有至少一bit1的任意值。对于每个10b symbol周期,加扰器产生8位,即S[7:0],其中S[0]表示在该周期内产生的第一个比特。

上行/反向下行链路TX应使用该加扰器产生一个加扰的数据/控制字节SB[7:0],该字节等于B[7:0] XOR S[7:0]。

8.3.2.4

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1297

1297

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?