文章目录

一、学习任务

1、从"实验3-基于Verilog HDL的数字秒表、波形发生器等设计" 任选一个完成;

2、练习基于VGA的图像显示,了解VGA协议,通过Verilog编程实现VGA端口生成彩条图案或者自定义的汉字图案;或者完成一个简单的类似贪吃蛇的VGA小游戏 (实际效果验证可在下次实验课检查)。

二、学习内容

1.基于Verilog HDL的数字秒表

1.1.仿真波形

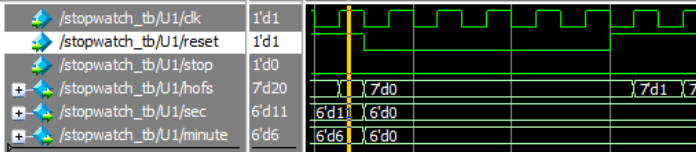

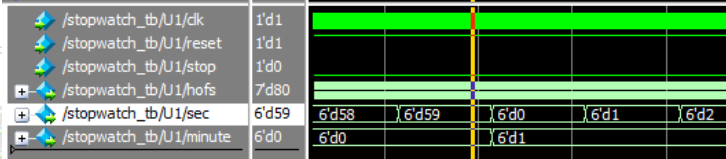

1.1.1.异步复位功能

1.reset从1变为0时,hofs,sec,minute全被复位变成0.

2.reset从0变为1后,hofs重新计数

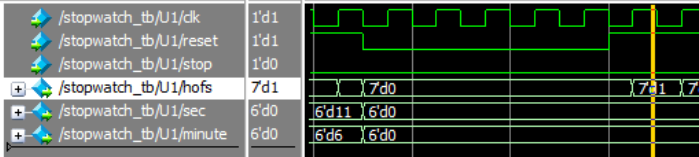

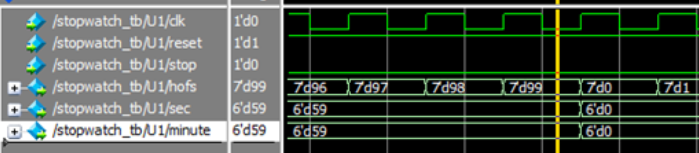

1.1.2.暂停功能

1.stop从0变为1时,hofs,sec,minute保持不变。

2.stop从1变成0,hofs,sec,minute继续计数。

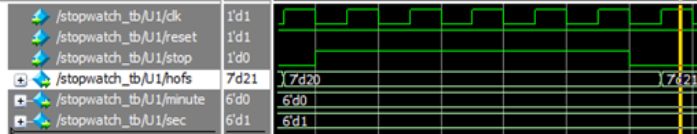

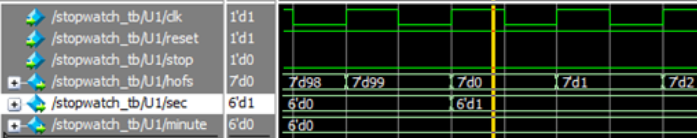

1.1.3.计数功能

1.hofs从0计数到99,sec加一次。

2.sec从0计数到59,minute加一次。

3.minute从0计数到59,hofs,sec,minute全部清0,重新下一次的计数

1.2.相关代码

module stopwatch(

input clk,

input rst_n,

input stop,

output [5:0] minute,

output [5:0] sec,

output [6:0] hofs

);

reg [6:0] counter100;//模100的计数器,用于百分秒计数和进位

reg [5:0] counter60_s; //模60的计数器,用于秒计数和进位

reg [5:0] counter60_m;//模60的计数器,用于分计数和清零

//异步复位和暂停

// counter100

always@(posedge clk or negedge rst_n or posedge stop) begin

if(!rst_n) //复位功能,低电平有效

counter100 <= 7'b0000000;

else if(stop) //暂停功能,高电平有效,保持原值不变

counter100 <= counter100;

else if(counter100 < 7'b1100011)//实现模100的计数器,小于99,累加1

counter100 <= counter100 + 1'b1;

else

counter100 <= 7'b0000000;

end

// counter60_s

always@(posedge clk or negedge rst_n or posedge stop) begin

if(!rst_n) //复位功能,低电平有效

counter60_s <= 6'b000000;

else if(stop) //暂停功能,高电平有效,保持原值不变

counter60_s <= counter60_s;

else

if(counter60_s < 6'b111100)

if(counter100 == 7'b1100011)

counter60_s <= counter60_s + 1'b1;

else

counter60_s <= counter60_s;

else

counter60_s <=

博客介绍学习任务,包括从基于Verilog HDL的数字秒表等设计中任选一个完成,练习基于VGA的图像显示。学习内容涵盖基于Verilog HDL的数字秒表的仿真波形(异步复位、暂停、计数功能)及相关代码,还有基于VGA的图像显示中FPGA驱动VGA显示文字的字库生成、代码与时序及结果显示。

博客介绍学习任务,包括从基于Verilog HDL的数字秒表等设计中任选一个完成,练习基于VGA的图像显示。学习内容涵盖基于Verilog HDL的数字秒表的仿真波形(异步复位、暂停、计数功能)及相关代码,还有基于VGA的图像显示中FPGA驱动VGA显示文字的字库生成、代码与时序及结果显示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?