Verilog HDL 学习笔记三

基于状态机的序列检测器

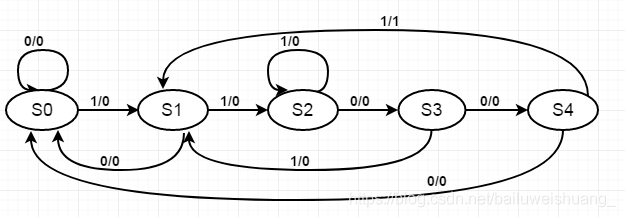

检测序列11001,其状态转移图如下所示:

三段式:在两个always模块描述方法基础上,使用三个always模块,一个always模块采用同步时序描述状态转移,一个always采用组合逻辑判断状态转移条件,描述状态转移规律,另一个always模块描述状态输出(可以用组合电路输出,也可以时序电路输出)。

设计代码:

module seqdet_11001(dout,din,clk,rst_n);

input clk,rst_n;

input din;

output reg dout;

reg [2:0] cst,nst;

localparam [2:0] s0=3'b000,

s1=3'b001,

s2=3'b010,

s3=3'b011,

s4=3'b100;

always @(posedge clk or negedge rst_n )

begin

if(!rst_n)

cst <= 0;

else

cst <= nst;

end

always @(din or cst)

begin

case(cst)

s0:if(din==1)

nst <= s1;

else

nst <= s0;

s1:if(din==1)

nst <= s2;

else

nst <= s0;

s2:if(din==0)

nst <= s3;

else

nst <= s2;

s3:if(din==0)

nst <= s4;

else

nst <= s1;

s4:if(din==1)

nst <= s1

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

936

936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?