1.冯诺伊曼计算机在结构上以 运算器 为中心,发展到现在,已转向以 存储器 为 中心。

2.计算机硬件结构:控制器、运算器、主存储器、辅助存储器、输入设备、输出设备

3.计算机发展经历了 电子管时代、晶体管时代、集成电路时代。

4.指令系统的优化设计向着两个方向发展:复杂指令系统计算机(CISC)和精简指令系统计算机(RISC)

5.总线是一组能够为多个部件分时共享的公共信息传送线路。分时是指同一时间只能允许一个部件向总线发送信息。然而,同一时间,允许多个部件接收相同的信息。包括地址总线、数据总线、控制总线。

6.多级存储体系:Cache、主存、辅助存储三级。

7.局部性原理——

时间局部性:一条指令执行后,不久可能再次被执行,因为程序中存在大量的循环执行;

空间局部性:程序访问了某一个存储单元后,它附近的存储单元可能也被执行,因为程序一般都是顺序执行。

8.存储器的存储方式:顺序存取、直接存取、随机存取和相联存取四种。

顺序存取:对数据的访问必须按照特定的线性顺序。磁带就是顺序存取方式。

直接存储:使用一个共享的读写装置对所有的数据进行访问,每一个数据块都有唯一的地址标识,读写装置可以直接移动到目的数据块所在位置进行访问。磁盘就是直接存储方式。

随机存取:存储器的每一个可寻址单元都有自己的唯一的地址和读写装置,系统可以在相同的时间内对任意的存储单元的数据进行访问,而已先前的访问序列无关。主存储器采用随机存取方式。

相联存取:相联存取也是一种随机存取的形式,但是选择某一单元进行读写是取决于其内容而不是地址。Cache采用相联存取方式。

9.主存分为:随机存取存储器(RAM)和只读存储器(ROM)

RAM可读可写,断电后信息无法保存。

RAM分为:DRAM(动态RAM)和SRAM(静态RAM)

DRAM:信息会随着时间而逐渐消失,必须定时刷新才能维持信息,密度大,便宜;

SRAM:只要不断电,信息不会丢失,速度快,电路简单(不需要刷新),容量小,价格高。

ROM只读不可写,即使断电,信息不会丢失。一般用于存放系统程序BIOS(Basic Input Output System,基本输入输出系统)

10.存储器中每一个单元的位数是相同且固定的,称为存储器编址单位。一般有字编址和字节编址。

主存一般以字节编址(8位),或者以字为单位(16位,或者32位等)

例如:主存地址从AC000H到C7FFFH,则共有C7FFFH-AC000H+1=1C000H个地址单元,转换为十进制:1*16^4+12*16^3=114688个地址单元,114688/1024=112KB个地址单元——这里可以把一个地址理解为一位Bit,那么它的地址大小112KB。——一般说的内存的大小(容量)指的就是它的地址空间。

如果该主存地址按字(16bit)编址,一个地址指向一个16位的单元(1个内存地址代表一个16bit的存储空间),则该主存一共有112KB *16 位。

假设该主存由28片存储器芯片构成,已知构成此主存的芯片每片有16KB个存储单元,

那么该芯片每个存储单元存储(112KB*16)/(28*16KB)=4位。

上面的理解思路是:地址空间是逻辑的(操作系统设定),编址也是逻辑(操作系统设定);存储单元的位数是物理固定的(存储芯片的位数和存储芯片的数量)。

深入理解:内存地址和内存空间——

例如经常说32位的操作系统最多支持4GB的内存空间,也就是说CPU只能寻址2的32次方(4GB),这里的4GB是以Byte为单位的,不是bit。即内存有4GB个地址单元。另外,32位的操作系统的CPU只能寻址32位(32根地址线),所以用8位十六进制(2^32)。

无论何种存储器,软盘、硬盘、光盘或者内存,都有地址。因为它们要存储数据,所以就必须按一定的单位的数据分配一个地址。有了地址,程序才能找到这些数据。如下图,第一行是数据,第二行是数据对应的内存的地址。

11.“冯诺伊曼瓶颈”:CPU与存储系统间数据传送带宽限制。

12.Cache通常使用相联存储器(CAM),CAM是一种基于数据内容进行访问的存储设备。

Cache改善系统性能的依据是程序的局部性原理。

CPU发出访存请求,存储器地址先被发送到Cache控制器以确定所需数据是否已在Cache中,命中或者不命中。这个过程称作Cache的地址映射,主存和Cache均被分成容量相同的块(页),操作系统需要高效率地完成主存和Cache之间的交换。常见的映射方法有直接映射、全相联映射和组相联映射。

下面假设内存容量是1GB(内存地址容量),Cache容量为8MB,页面的大小为512KB。

12.1 直接映射

直接映射方式以随机存取存储器作为Cache存储器,硬件电路比较简单。

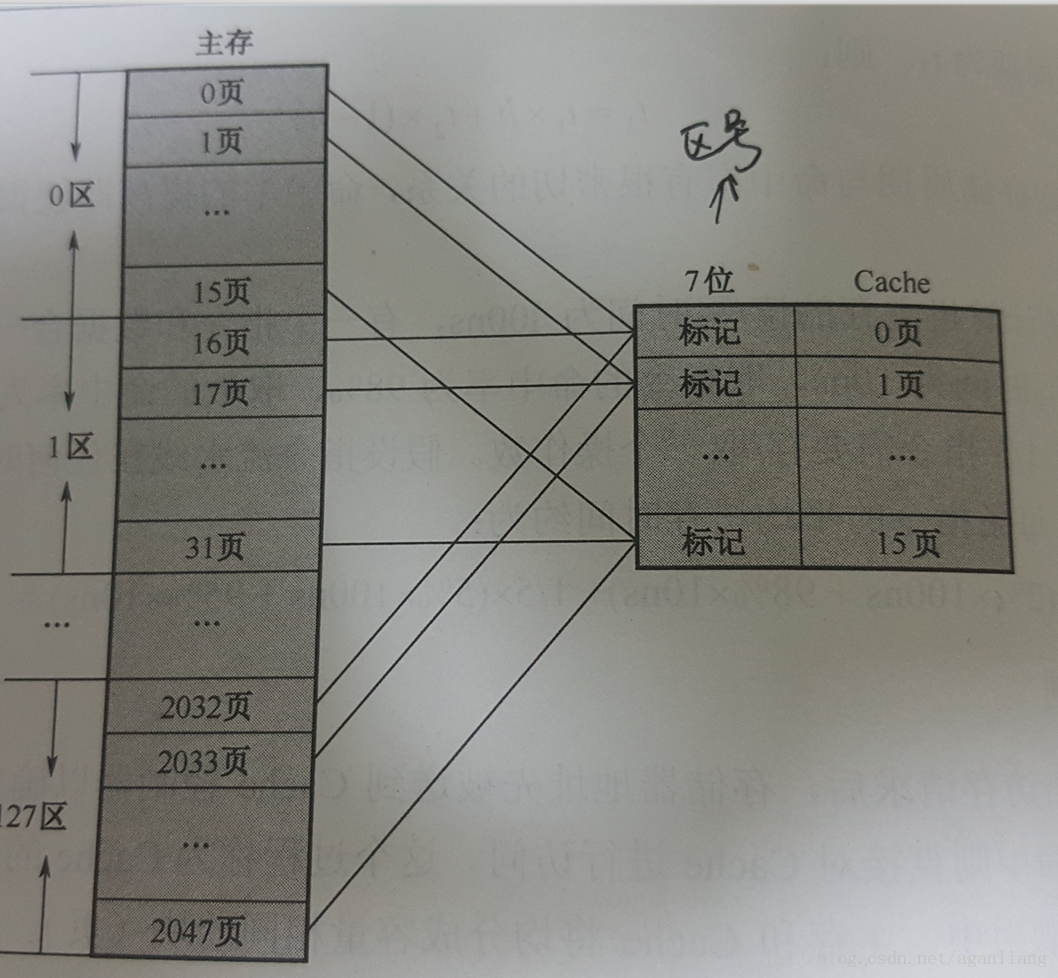

主存先分区,再分页。主存一个区的大小就是Cache的容量大小,所以,1GB/8MB=128个区,区号用7位即可。

每一个区分为:8MB/512KB=16个页,页号用4位即可。

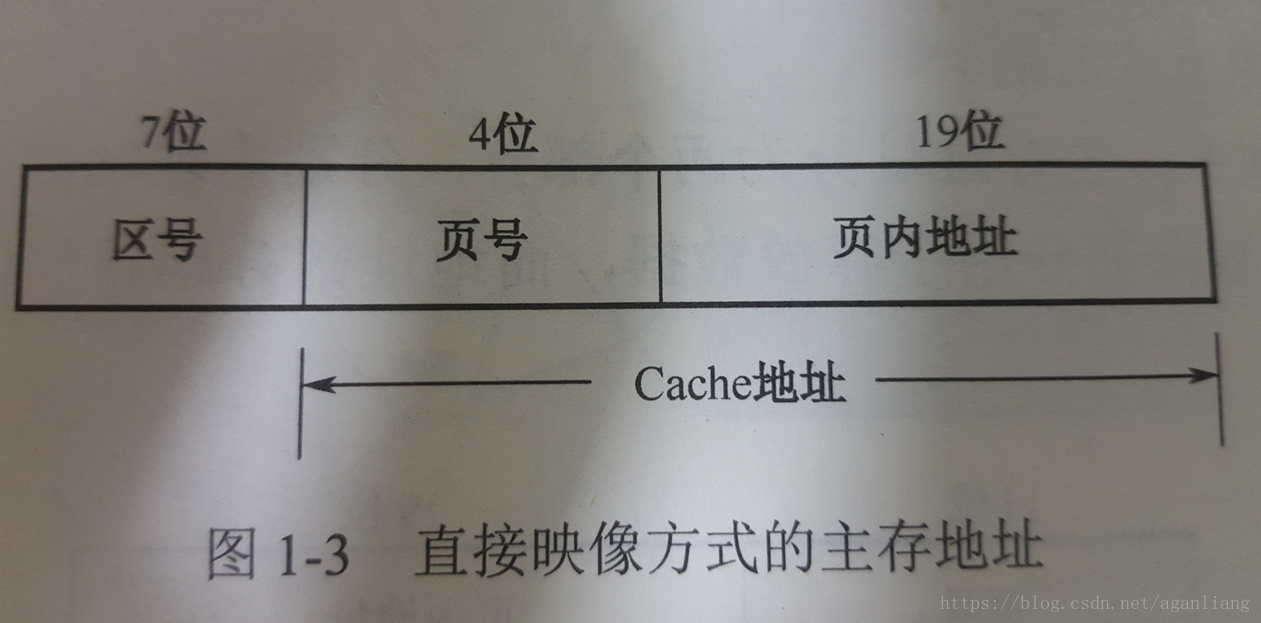

主存地址一共30位(1GB=2^30),那么页内地址剩下:30-7-4=19。

Cache地址一共23位(8MB=2^23),另外:23=4+19。

如下图所示:

直接映射方式:每一个主存页只能复制到某一个固定的Cache页中。即主存中每一个区的第N页,只能进入到Cache的第N页。这种方式导致直接映射的页冲突率非常高。

Cache为每一页设立一个Cache标记,用于识别当前的Cache页来自于哪个内存页,由于上面的规则,这个标记只需要记录区号即可,所以,标记为 7 位即可。如图所示:

12.2 全相联映射

全相联映射使用相联存储器组成Cache存储器。

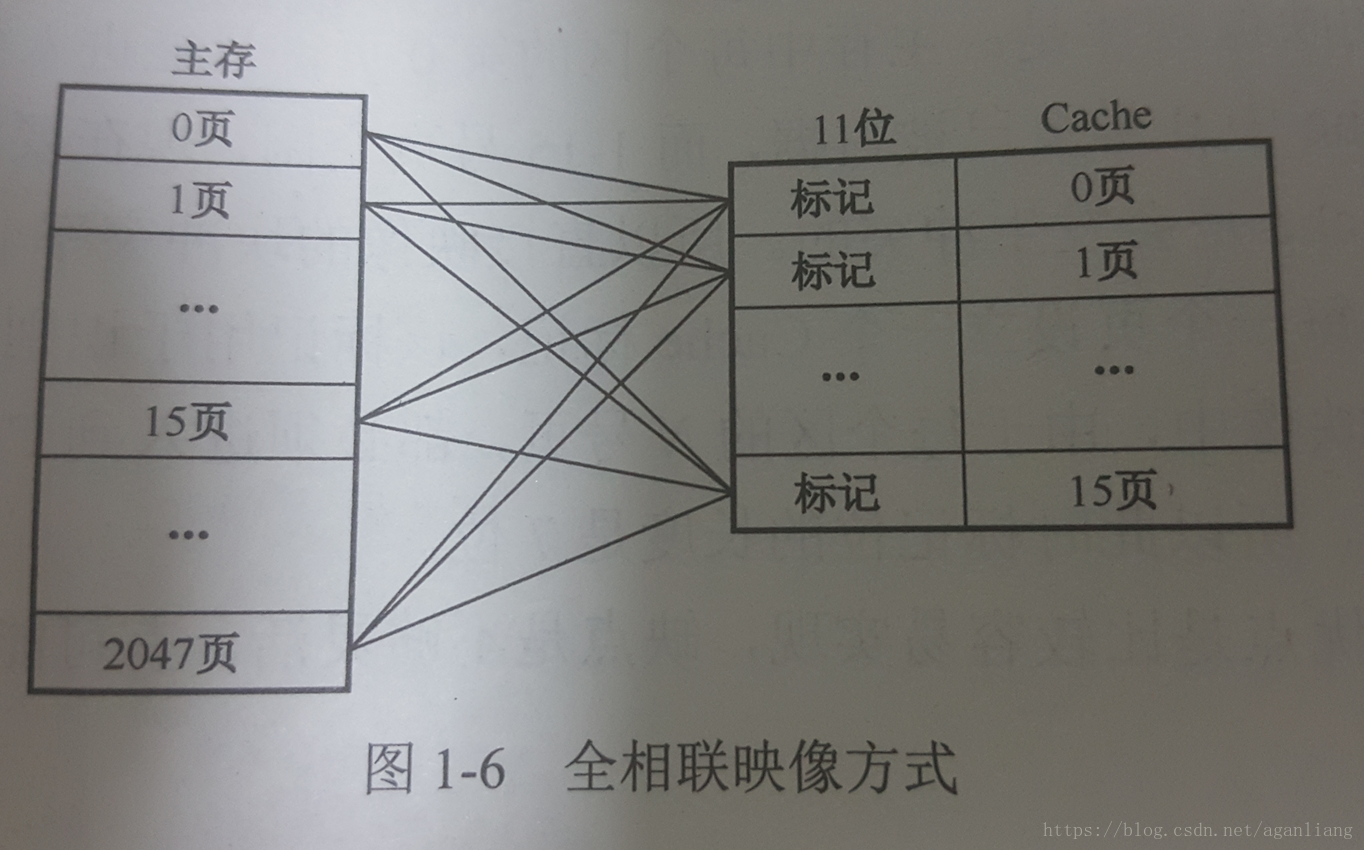

全相联映射中,主存的每一页可以映射到Cache的任一页。

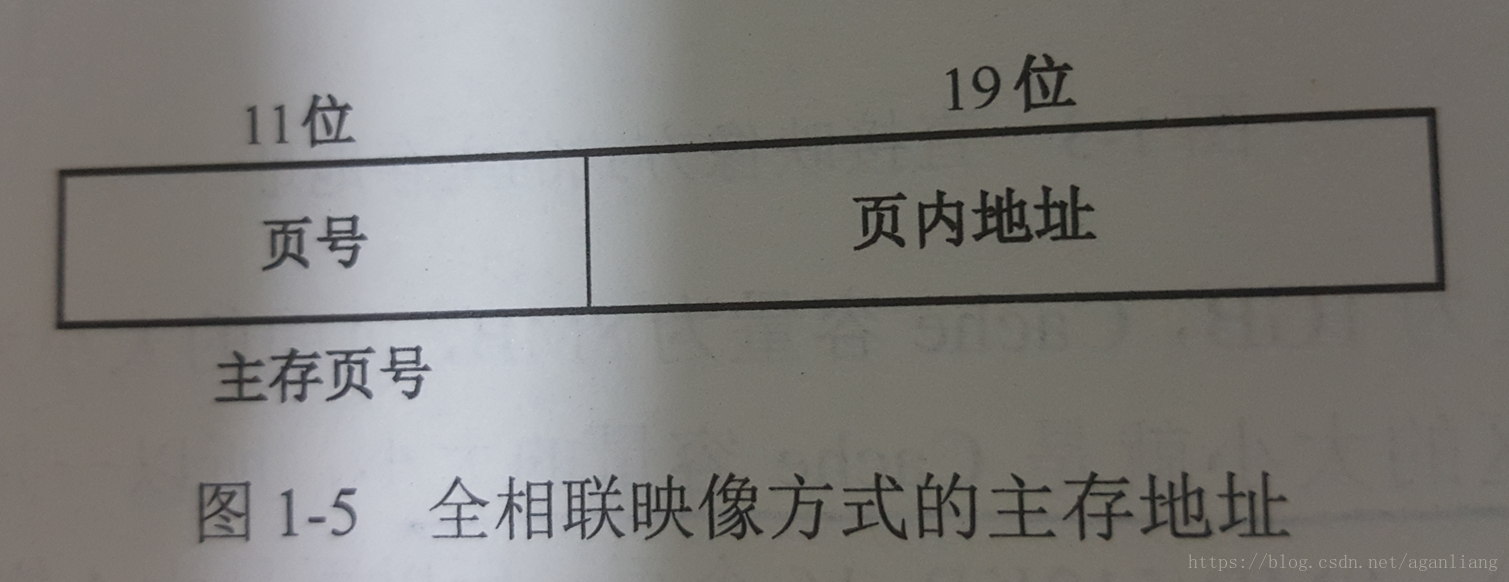

总共有1GB/512KB=2048个页,所以,页号需要11位(2^11);主存地址分为地址部分(主存页标记)和数据部分(页内地址)。

如图所示:

由于每个Cache页可以映射到2048个主存页中的任一页,所以,每页的Cache标记需要11位(2^11),以表明它现在所映射的主存页号。因此,Cache标记信息位数增加,比较逻辑成本随之增加。

全相联映射方式因为 比较器电路难以设计和实现,只适用于小容量Cache。

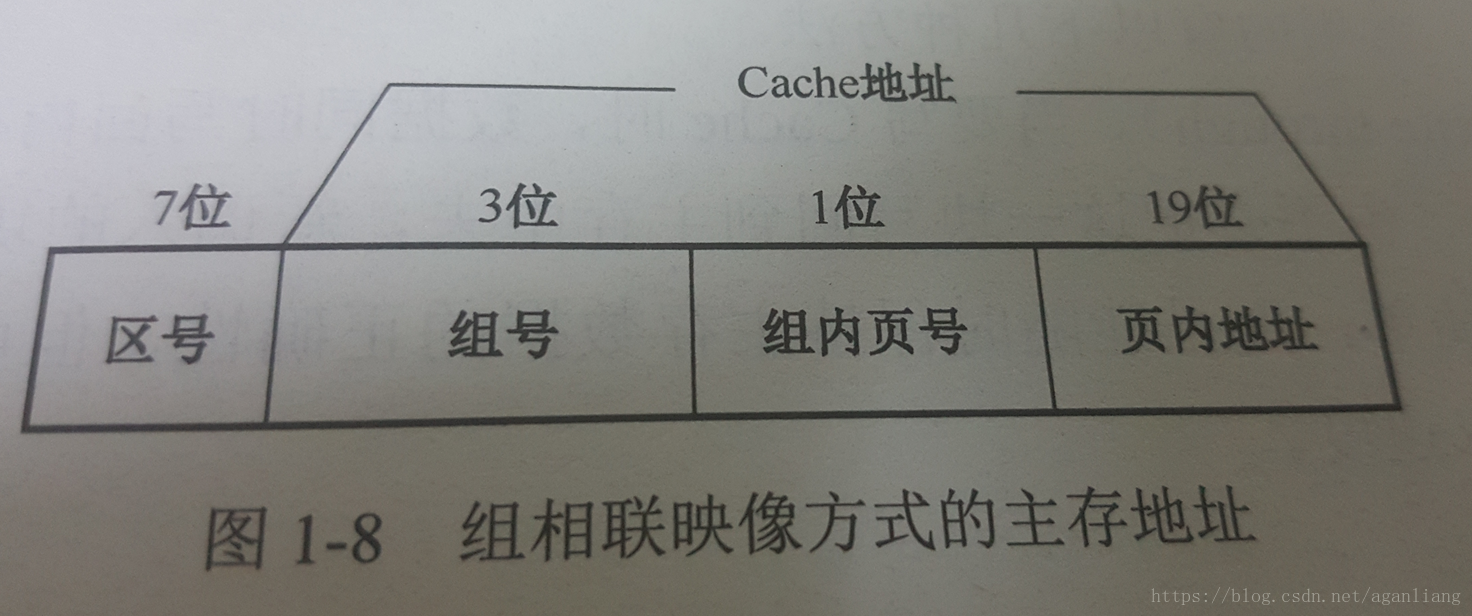

12.3 组相联映射

组相联映射(页组映射)介于直接映射和全相联映射之间,是这两者的一种折中方案。

全相映射:以页为单位,可以自由映射,没有固定关系。

直接映射:主存分组,主存组内的各页与Cache的页之间采取固定的映射关系,但是各组可以自由映射到Cache中。

组相联映射:主存与Cache都分组,主存中的一个组内的页数与Cache的分组数相同。

如图所示:

它的规则是:主存中的组与Cache的组形成直接映射关系,而组内的每一页是全相联映射关系。如主存1区0组,只能进入Cache的0组,但是,可以自由进入0组的0页或者1页。

可以看出,如果Cache的每一组只有1页,那么它实际就是直接映射;如果Cache的每一组有16页(即只有1组),那么它实际就是全相联映射。

由于需要记录区号,还需要记录组号,所以,Cache标记位数是7+1=8。

如图所示:

PS:为了保证性能,主存与Cache之间的映射一般采用硬件完成,对于程序员来说,是透明的。

13.流水线

流水线周期:将需要处理的工作分为N个阶段,最耗时的那一段所消耗的时间。如,使用流水线技术执行100条指令,每条指令取指2ms,分析4ms,执行1ms,那么,流水线周期是4ms。

流水线执行时间T = 第一条指令的执行时间 + (N-1)*流水线周期t

14.进程状态模型

传统进程的三态模型中,总是假设所有进程都在内存中,事实上,由于进程的不断创建,系统的资源已经不能满足进程运行的要求,这个时候必须把某些进程挂起,所谓挂起就是把进程从内存对换到磁盘镜像区中,暂时不参与进程调度。

所以,三态模型:运行——活跃阻塞——活跃就绪,活跃是指在内存中。

变成五太模型:运行——活跃阻塞——活跃就绪——静止就绪——静止阻塞,静止是指在磁盘镜像区中。

15.虚拟内存管理

假如内存地址由 页目录号、页号、页内偏移三部分组成,其中,页目录号占10位,页号占10位,页内偏移占12位

那么,页目录号占10位,即一个页目录最多2^10=1K页;页内偏移12位,即页的大小是2^12=4K。

16.I/O系统

处理器完成I/O指令有两种方式:查询方式和中断方式。

查询方式:处理器直接利用I/O指令编程,实现数据的输入输出。处理器发出I/O指令,命令中包含了外设的地址信息和所要执行的操作,相应的I/O系统执行该命令并设置状态寄存器;处理器不停地查询I/O系统以确定该操作是否完成。该方式简单,硬件开销小。

中断方式:处理器利用中断方式完成数据的输入和输出,当I/O系统与外设交换数据时,处理器无须等待,也不必去查询I/O的状态;当I/O系统完成输入后,则以中断信号同志处理器。处理器保存正在执行程序的现场,转入I/O中断服务程序完成与I/O系统的数据交换,然后返回原主程序继续执行。该方式无须等待,实时性好。

本文介绍了计算机体系结构的基础知识,涵盖了冯诺伊曼计算机的发展、硬件结构、指令系统、存储体系等内容,并详细解释了Cache的不同映射方式及其对系统性能的影响。

本文介绍了计算机体系结构的基础知识,涵盖了冯诺伊曼计算机的发展、硬件结构、指令系统、存储体系等内容,并详细解释了Cache的不同映射方式及其对系统性能的影响。

344

344

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?