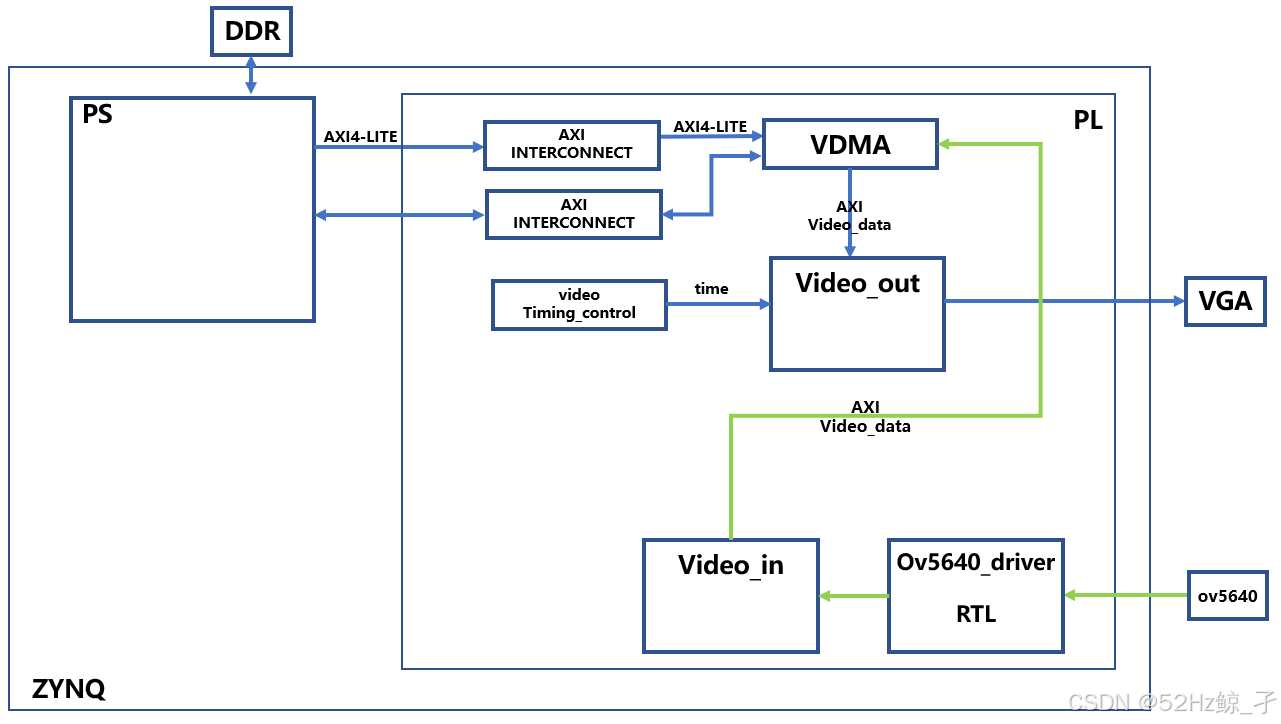

方案

开发板:ebaz4205

摄像头:ov5640

显示器:vga接口,1080p

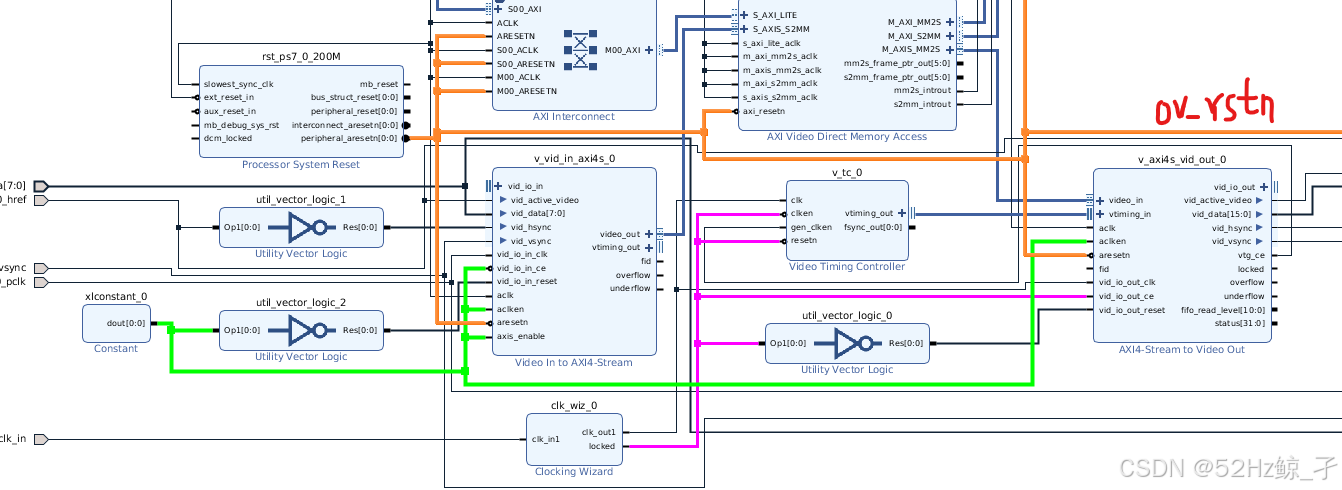

vivado设计

时钟需求:74.25Mhz(PL晶振分频)、50Mhz和200Mhz(PS引出)

高速总线需求:AXI-HP

VTC

输出:根据分辨率 输出视频显示同步信号

clk:74.25Mhz(1024*720 60hz) (用一个clock wizard生成)

如果是1080p下图要配置1080p,且要改VTC的输入时钟,1080p 60hz 时钟为148.5Mhz

vga接口

输入:使能信号、视频数据

输出:vga数据

根据有效信号使能,向vga输出16位显示数据。

`timescale 1ns / 1ps

module video_active(

input active_video,

input [15:0] rgb_data_i,

output wire [15:0] rgb_data_out

);

assign rgb_data_out = (active_video == 1'b1) ? {rgb_data_i[7:0], rgb_data_i[15:8]}: 16'h0;

endmoduleAXI4-Stream to Video Out

输入:video_data 、 VTC输出的视频同步信号

输出:vga同步信号、视频数据

作用:将DDR取出的视频数据进行同步

输入输出位宽都为16bit

in_clk:200M out_clk:74.25Mhz(1024*720 60hz)

VDMA

通过高速接口连接至zynq,通过zynq读写内存中的视频数据,输出至stream to video_out

clk:200M

OV5640模块

verilog驱动(配置)ov5640摄像头(摄像头自带驱动晶振)

摄像头输入:视频数据1024*720(可配置)、同步信号、像素时钟

RTL输出:iic配置信号、复位、上电

50Mhz时钟用于输出配置信息

三个模块:iic通信模块、ov5640寄存器配置模块、sccb通信启动模块

代码托管:wrjxx/ov5640-驱动程序-verilog- (github.com)

1080p输出要改ov5640驱动中的寄存器配置,配置输出1080p的参数。(可参考github 1080p_cfg)

modelsim仿真(debug)

寄存器配置到100被复位,检测发现计数溢出导致。修改为时序逻辑后解决,成功输出304个寄存器配置。

![]()

![]()

AXI4-Stream to Video In

接收摄像头采集的数据,传到VDMA

输入:同步信号、像素时钟(pclk)、视频数据

输出:视频数据 (clk=200M)

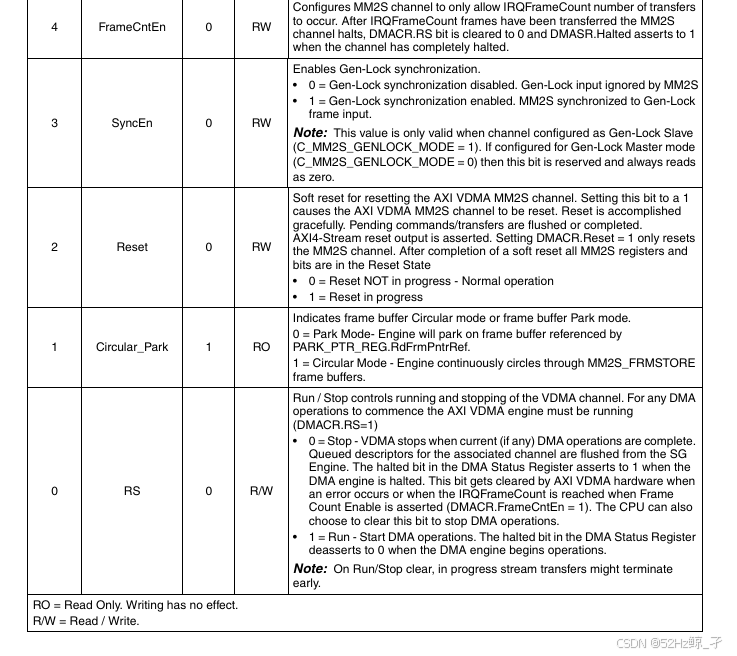

裸机测试(乒乓操作)

内存作为帧缓存(显存),进行乒乓操作来避免视频割裂。

VDMA的frame buffer设置 3帧缓存。

#include "xil_io.h"

#include "xil_types.h"

#include <stdio.h>

#include <sleep.h>

int main(){

// read

Xil_Out32(0x43000000,0x8B); // 对0x8b的解释:10001011 见下图

Xil_Out32(0x43000000+0x5C,0x01000000); //指定三帧在ddr中的起始地址

Xil_Out32(0x43000000+0x60,0x02000000);

Xil_Out32(0x43000000+0x64,0x03000000);

Xil_Out32(0x43000000+0x58,1920*2);

Xil_Out32(0x43000000+0x54,1920*2); // 一个像素占两个字节(所以要x2)

Xil_Out32(0x43000000+0x50,1080);

//write

Xil_Out32(0x43000000+0x30,0x8B);

Xil_Out32(0x43000000+0xAC,0x01000000);

Xil_Out32(0x43000000+0xB0,0x02000000);

Xil_Out32(0x43000000+0xB4,0x03000000);

Xil_Out32(0x43000000+0xA8,1920*2);

Xil_Out32(0x43000000+0xA4,1920*2);

Xil_Out32(0x43000000+0xA0,1080);

return 0;

}

VDMA提供四种模式的 Genlock 同步。其中GenLock 同步锁相机制(保证读写同一块帧缓冲的顺序)。

问题记录

vivado报错

外部输入时钟

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets ov5640_pclk_IBUF]

xdc文件添加,降级该错误裸机测试推流失败

① vga无法驱动。 因为直接给vtc的clken接了constant 1。应该接PLL的locked,需要等PLL稳定后再对逻辑进行复位和使能。

② 摄像头无法驱动。跨时钟域处理问题导致亚稳态。。。。

ov5640接了全局复位,ps时钟,复位应该不会产生亚稳态。

要根据时钟源确定使能和复位信号的连接。注意时序。

显示问题

视频显示偏蓝绿色,寄存器错误配置为了YUV。修改后解决。

![]()

1826

1826

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?