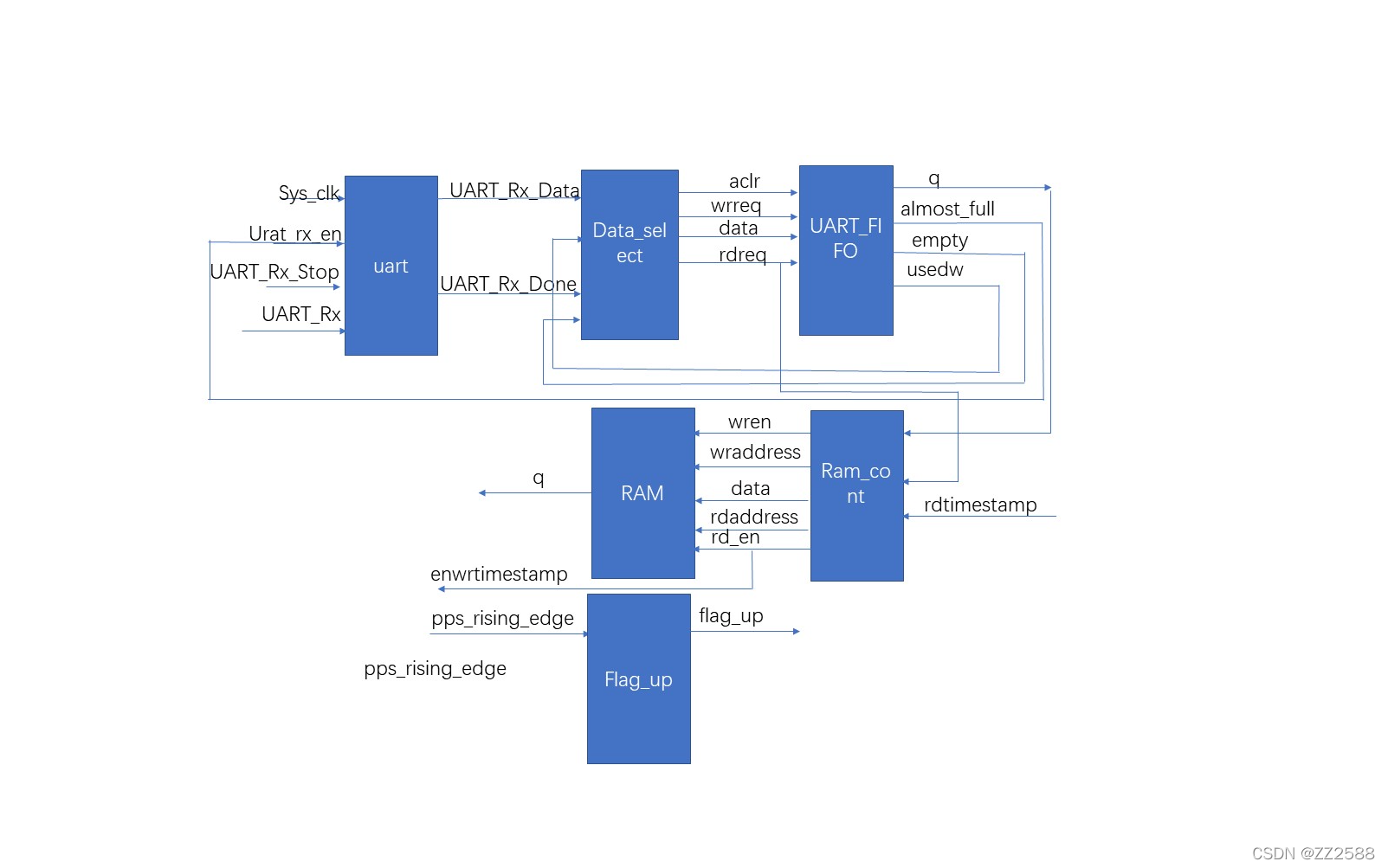

串口接受时间戳模块图:

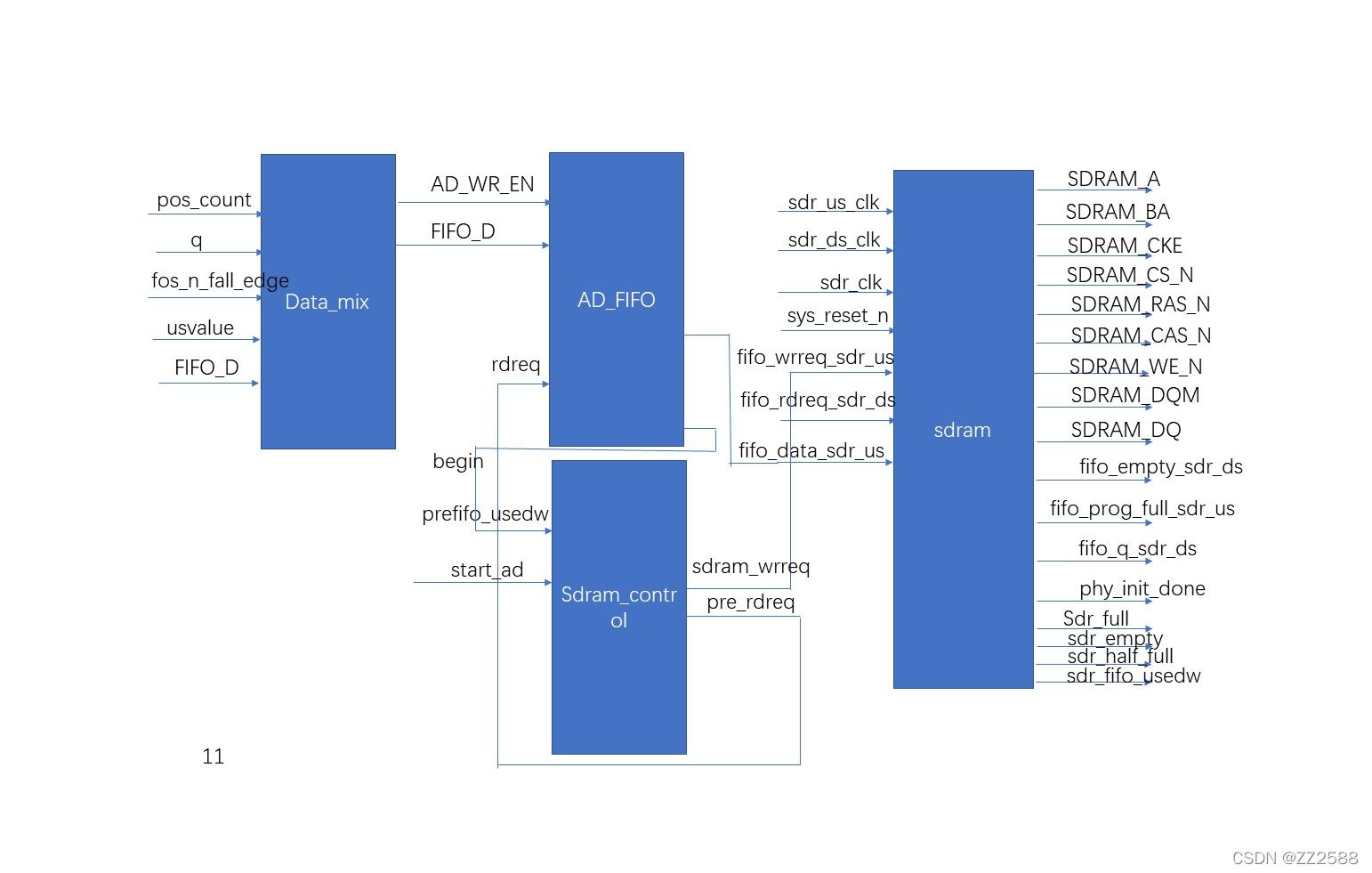

将时间戳与AD数据存入sdram模块图:

本项目是基于在原有的16路AD采集卡的系统之上,加入GPS实时的授时系统。将FPGA接收卫星信号的时间戳,插入到AD数据中,从而产生带有实时时间戳的ad数据。

基本原理是FPGA模块通过uart串口模块,接收来自卫星发送的tod信号,提取tod信号的有效字节作为大秒(既时分秒、日月年),通过10Mclk时钟计数来产生小秒,理论上最小精度可达100ns具体看来自卫星的时钟。

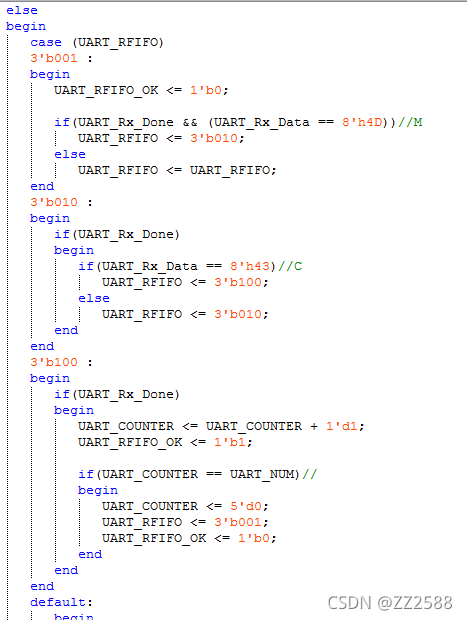

具体实现过程,通过调用uart串口,接收卫星信号发送的格林威治时间,通过计数器筛选有用信号(一共35B,有效数据只有12B)

UART_Rx_Done uart串口数据接收完成信号,M、C信号之后就是时间戳的有效数据,因此可以将此作为接收时间戳信号的标志位,

该项目将GPS实时授时系统与16路AD采集卡结合,通过FPGA接收卫星时间戳并插入AD数据中,实现带有时间戳的高精度AD测量。FPGA利用UART接收卫星的格林威治时间,筛选有效数据,存储于寄存器,然后与AD数据一同写入DRAM,上位机软件可显示并记录时间戳数值。

该项目将GPS实时授时系统与16路AD采集卡结合,通过FPGA接收卫星时间戳并插入AD数据中,实现带有时间戳的高精度AD测量。FPGA利用UART接收卫星的格林威治时间,筛选有效数据,存储于寄存器,然后与AD数据一同写入DRAM,上位机软件可显示并记录时间戳数值。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

784

784

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?