一、实验目的

1.进一步熟悉 ALTERA 公司 EDA 设计工具软件 Quartus II。

2.进一步熟悉 Quartus II 设计的原理图输入方法及设计流程。

二、实验原理

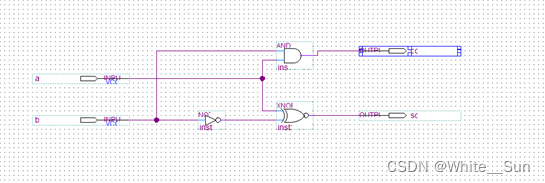

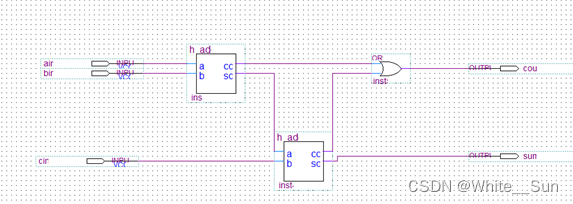

1 位全加器可以用两个半加器及一个或门连接而成,半加器原理图的设计方法很多,我

们用一个与门、一个非门和同或门(xnor 为同或符合,相同为 1,不同为 0)来实现。先设计

底层文件:半加器,再设计顶层文件全加器。

三、实验内容

在Quartus II软件中使用原理图输入法设计并实现一个1位全加器。在实验板上拨码开关作为输入设置,组成一个全加器,用实验板上的发光二极管作为输出,观察全加器输出随拨码开关置值的改变而引起的相应变化。

1.半加器原理图

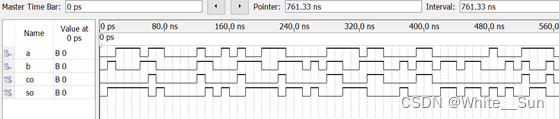

2.半加器仿真波形

3.一位全加器原理图

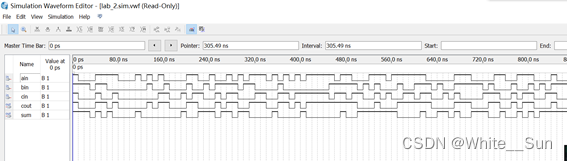

4.一位全加器仿真波形

波形分析:sum的结果为ain、bin全加的结果,cin为进位标志,从仿真波形可以看出,sum满足两个二进制数ain、bin相加,并且输出cout加法进位。

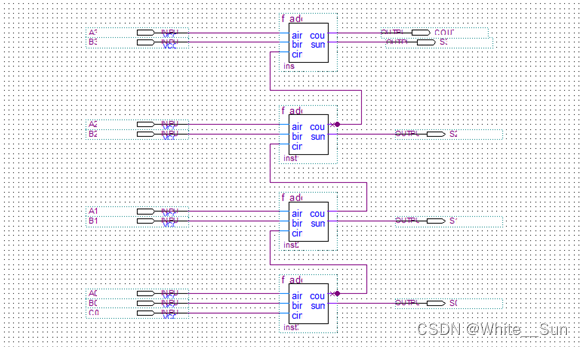

5.四位全加器原理图:

6.四位全加器波形仿真:

四、实验总结:

通过本次实验学习,完成了半加器和全加器电路设计和波形仿真,熟悉半加器和全加器功能,回顾了数电的基础知识,加深了对EDA软件仿真功能的了解,进一步熟悉并能掌握电路图设计和仿真波形等关键功能的初步实现。

错误整理(Quartus9.0版本):①创建好半加器的原理图后,忘记点击“Creat Symbol Files for Current File”以生成模块。②未经过编译就试图在vwf文件中导入端口。

本实验旨在通过Quartus II软件设计和实现1位及4位全加器。首先,介绍了半加器的原理,采用与门、非门和同或门实现。接着,设计了1位全加器,然后扩展到4位全加器。通过实验板验证,观察输入变化对输出的影响。实验中还指出了常见错误,如未生成模块符号文件和未经编译导入端口。

本实验旨在通过Quartus II软件设计和实现1位及4位全加器。首先,介绍了半加器的原理,采用与门、非门和同或门实现。接着,设计了1位全加器,然后扩展到4位全加器。通过实验板验证,观察输入变化对输出的影响。实验中还指出了常见错误,如未生成模块符号文件和未经编译导入端口。

1231

1231

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?