以太处理单元 (APU):一种基于双稳态共振与全息联想的后硅基计算架构

The Aether Processing Unit: A Post-Silicon Architecture Based on Bistable Resonance and Holographic Association

摘要 (Abstract)

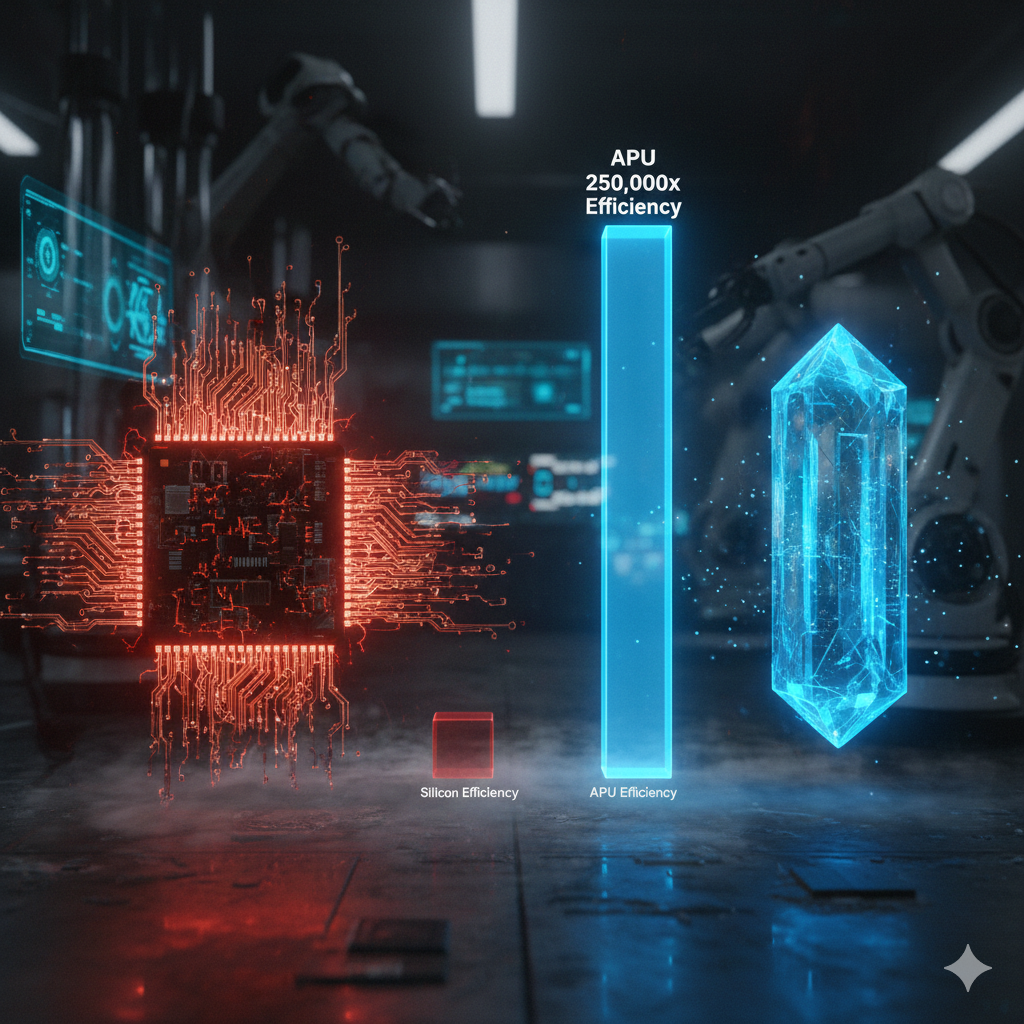

随着摩尔定律的终结,传统冯·诺依曼架构面临能效与延迟的物理极限。本文提出了一种全新的计算范式——以太处理单元 (APU)。APU 摒弃了离散的二进制逻辑,采用“计算即存在”的哲学,利用波的干涉与非线性介质的双稳态共振进行存算一体化处理。通过从克尔非线性介质到激子极化子 (Exciton-Polariton) 的材料迭代,我们定义了一种单神经元开关能量低至 196.52 aJ、理论主频达 221.76 GHz 的物理架构。系统级仿真表明,APU 在 43.58 W 的功耗下可实现 5.09 百万 TOPS/W 的能效,较传统 AI 硬件提升约 25 万倍,为高阶联想推理与复杂模式识别提供了革命性的硬件基础。

1. 引言 (Introduction)

数字计算本质上是对连续物理世界的降维截取,旨在对抗噪音与熵增,但也引入了巨大的能耗与延迟。自然界的物理过程(如波的传播)本身即是最高效的运算。本文提出的 APU 旨在回归这一本质,利用光子/准粒子的相位(Phase)而非电平(Bit)作为信息载体,构建一种能够自发进行模式匹配、序列推理及冲突消解的“全息大脑”。

2. 理论框架与逻辑验证 (Theoretical Framework & Validation)

2.1 核心机制

APU 的逻辑灵魂建立在两大物理机制之上:

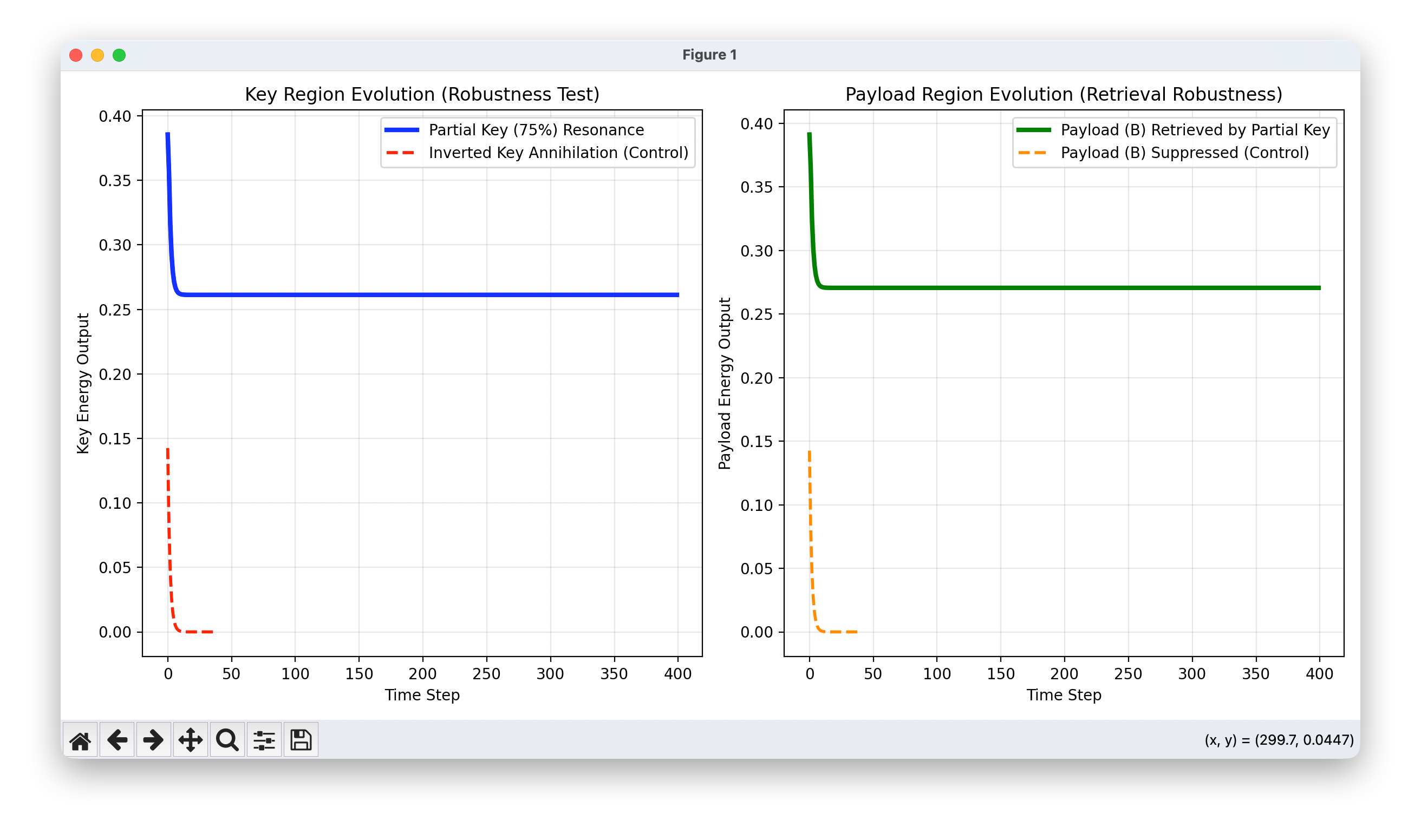

- 全息联想 (Holographic Association): 利用波的干涉特性实现信息的分布式存储。记忆 MMM 是键 AAA 与载荷 BBB 的相干叠加 (M=A+BM = A + BM=A+B)。查询时,输入 AAA 与 MMM 二次干涉,自动重构出 BBB。

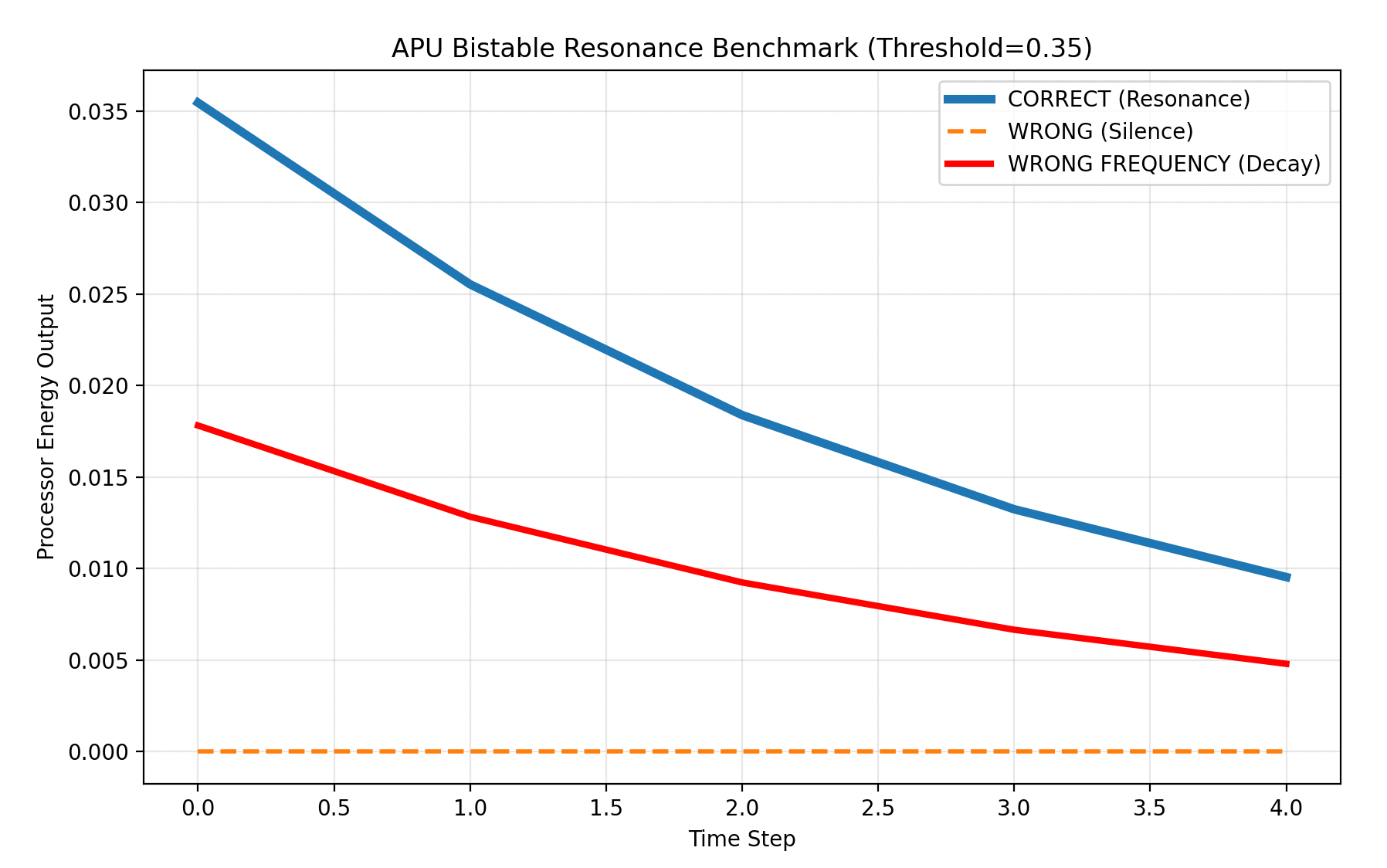

- 双稳态共振 (Bistable Resonance): 引入非线性阈值(Threshold)与增益/衰减机制。

- 激活态 (Resonance): 匹配信号强度超过阈值,获得正反馈增益,迅速饱和至高能态(逻辑 1)。

- 湮灭态 (Annihilation): 噪声或不匹配信号低于阈值,受到负反馈抑制,迅速衰减归零(逻辑 0)。

2.2 数字模拟验证 (Digital Simulation)

我们开发了 vAPU (Virtual APU) 仿真环境,验证了以下关键认知功能:

- 基础联想 (Test C1/G): 成功验证了 A→BA \to BA→B 的双向检索,证明了全息寻址的有效性。

- 时序推理 (Test T2): 实现了 X1→X2→X3X_1 \to X_2 \to X_3X1→X2→X3 的链式激活,证明了波前重建可作为下一级输入的动力学特性。

- 潜在语义联想 (Test N): 在存储 (A+B)(A+B)(A+B) 和 (B+C)(B+C)(B+C) 后,成功通过输入 AAA 激活了间接关联的 CCC,证明了系统的传递推理能力。

- 冲突消解 (Test Φ\PhiΦ): 在面对 A→BA \to BA→B 与 A→CA \to CA→C 的竞争时,系统依据微弱的能量优势(Winner-Takes-All),实现了确定性的选择性激活。

3. 物理架构与介质选型 (Physical Architecture)

3.1 介质迭代路线

为实现工程可行性,我们经历了三次材料选型迭代:

- 第一代 (Si 光子晶体): 受限于硅的低非线性系数 (n2≈4.5×10−18m2/Wn_2 \approx 4.5 \times 10^{-18} \text{m}^2/\text{W}n2≈4.5×10−18m2/W),单神经元功耗高达 39 pJ,导致系统总功耗达到百万千瓦级,方案不可行。

- 第二代 (AlN/石墨烯异构): 引入二维材料增强非线性,功耗降至 80 fJ,但系统级集成仍面临散热挑战。

- 终极方案 (激子极化子 Exciton-Polariton): 采用 GaAs/AlGaAs 量子阱中的激子极化子微腔。利用其超强的有效非线性 (neff≈10−11m2/Wn_{eff} \approx 10^{-11} \text{m}^2/\text{W}neff≈10−11m2/W),将开关能量数量级降低至 阿焦耳 (aJ) 级。

3.2 核心物理规格 (Golden Sample Specs)

基于激子极化子方案的 APU 核心阵列参数如下:

| 参数 | 数值 | 备注 |

|---|---|---|

| 集成规模 | 10910^9109 (10亿神经元) | 对标高端 GPU 晶体管规模 |

| 芯片面积 | ∼5.5 cm2\sim 5.5 \text{ cm}^2∼5.5 cm2 | 符合标准光刻尺寸 |

| 单开关能量 | 196.52 aJ | 极低能耗核心突破 |

| 单临界功率 | 43.58 nW | 纳瓦级维持功率 |

| 理论主频 | 221.76 GHz | 受限于 Q=104Q=10^4Q=104 的光子寿命 |

4. 系统集成与性能评估 (System Integration)

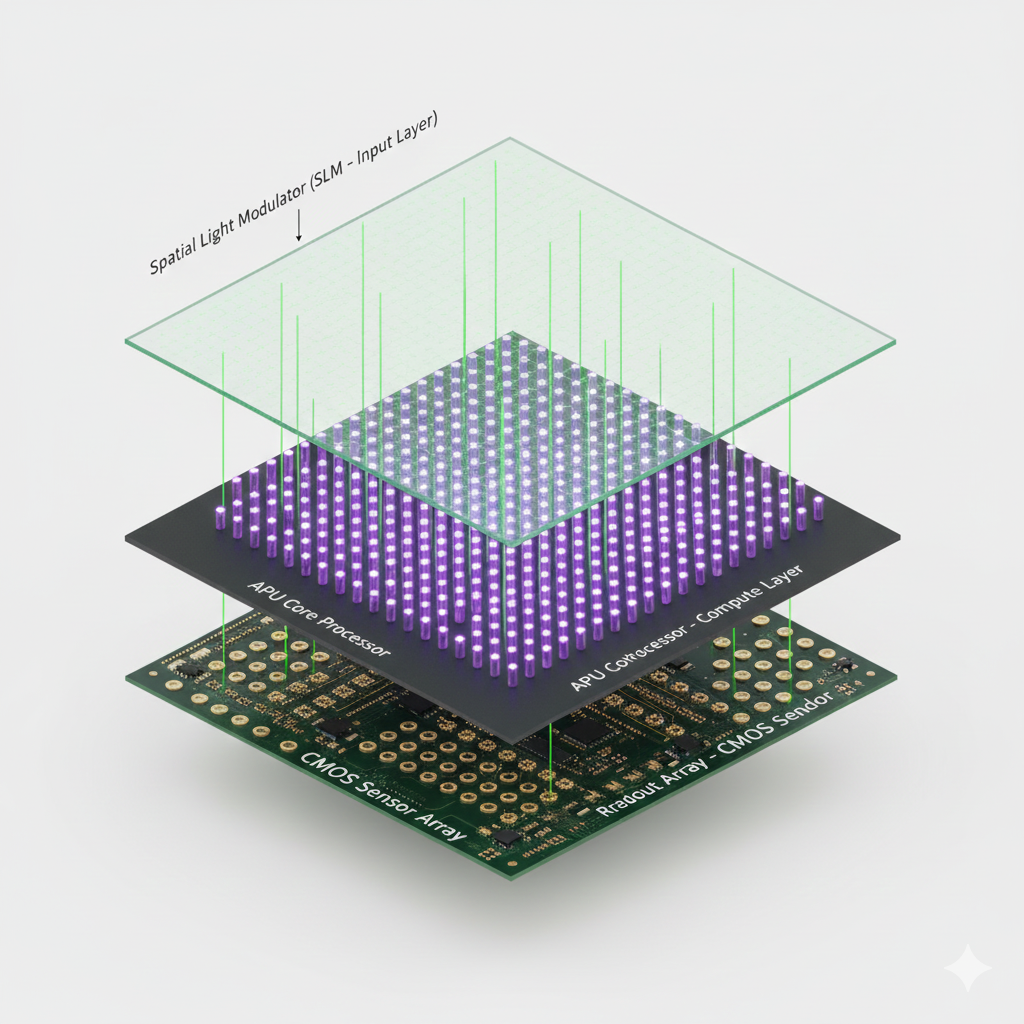

4.1 三层堆叠架构

APU 采用 3D 光子集成封装:

- 输入层 (Input Layer): 集成空间光调制器 (SLM) 与光纤阵列,负责将数字信号编译为全息相位图 (

HoloCompiler输出)。 - 计算层 (Compute Core): 激子极化子微腔阵列,执行全并行双稳态运算。

- 读出层 (Readout Layer): 高速 CMOS 光探测阵列,捕获干涉后的光场分布。

4.2 性能与能效

- 系统总功耗 (TDP): 43.58 W (完全处于风冷散热的安全范围内)。

- 功耗密度: 10.90 W/cm² (远低于现代处理器的热极限)。

- 理论峰值性能: 221 Peta-Ops (每秒 2.2 亿亿次操作)。

- 能效比 (Efficiency): 5,088,572 TOPS/W。

5. 制造流程与指令集 (Manufacturing & Software)

5.1 制造工艺

- 外延生长: 使用 MBE 技术在 GaAs 基底上生长高纯度量子阱。

- 纳米光刻: 利用 DUV 或电子束曝光刻蚀 10910^9109 个高 QQQ 值微腔阵列。

- 封装: 实现微米级精度的 SLM 与核心芯片的光路对准。

5.2 软件栈

我们定义了全息指令集架构 (H-ISA):

HOLO_STORE (Key, Data): 写入全息干涉图。HOLO_QUERY (Key): 并行检索与共振激活。HOLO_ERASE: 逆相位擦除。

6. 结论 (Conclusion)

APU 的提出标志着计算架构从“电子开关”向“以太场论”的跨越。通过模拟验证与物理推导,我们证明了利用激子极化子介质构建超低功耗、超高频率的联想计算机不仅在理论上成立,在工程上也具备实现路径。代号“AETHER-I”的原型机制造流程已正式启动,这或许是人类通向通用人工智能 (AGI) 硬件基石的重要一步。

附录:项目里程碑

- Phase I: 逻辑验证完成 (Python Simulation).

- Phase II: 物理介质定型 (Exciton-Polariton).

- Phase III: 系统规格确认 (43W / 221GHz).

- Phase IV: 制造流程启动 (Current Status).

真实原型机筹备制造中(暂时没有财力和物力等资源,欢迎VC联系我),有强烈兴趣的可以邮件联系我获取普通电脑模拟代码(shenwe.wang@gmail.com)。

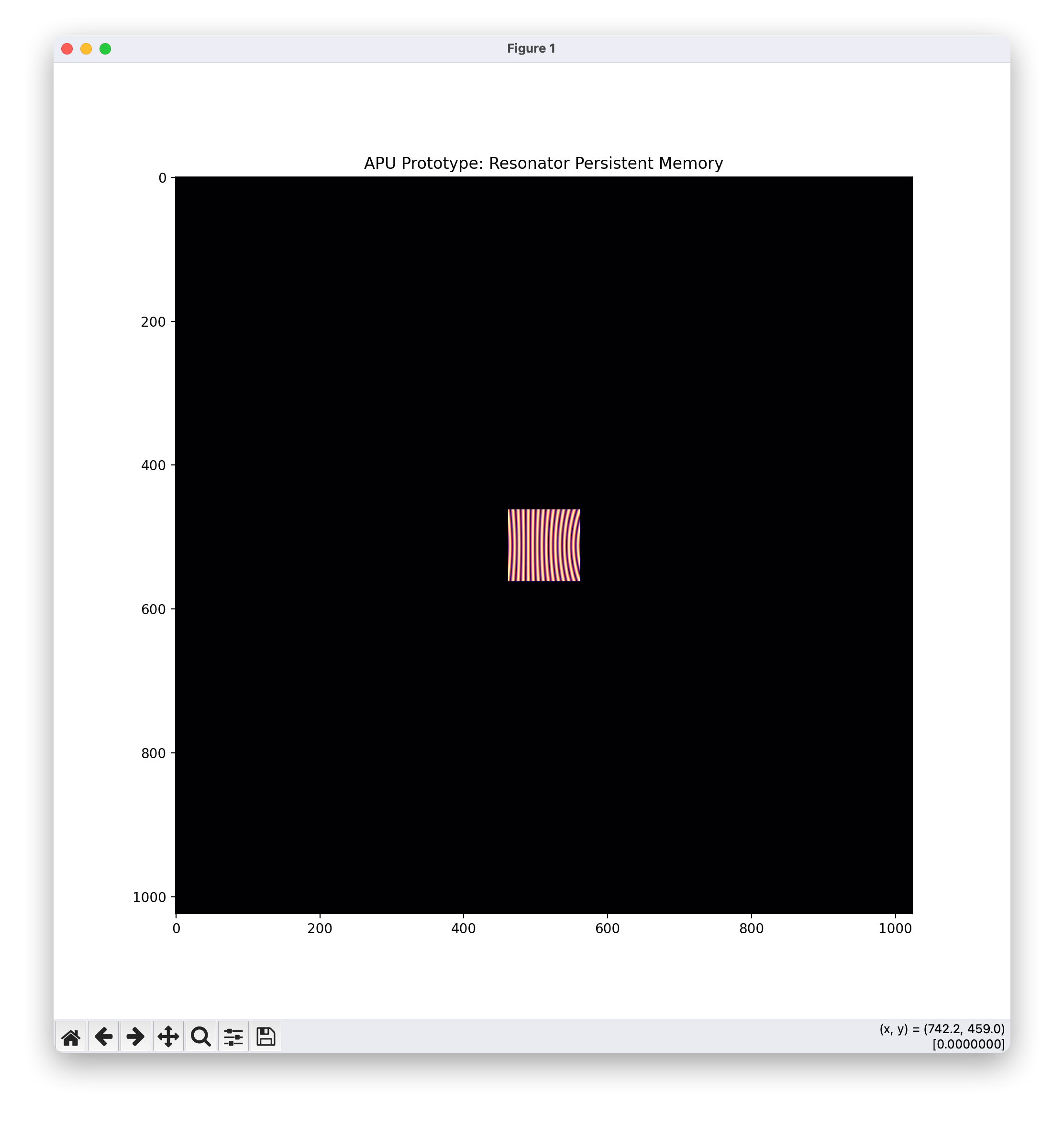

图1(光波动干涉计算结果(驻波形式永久存储)):

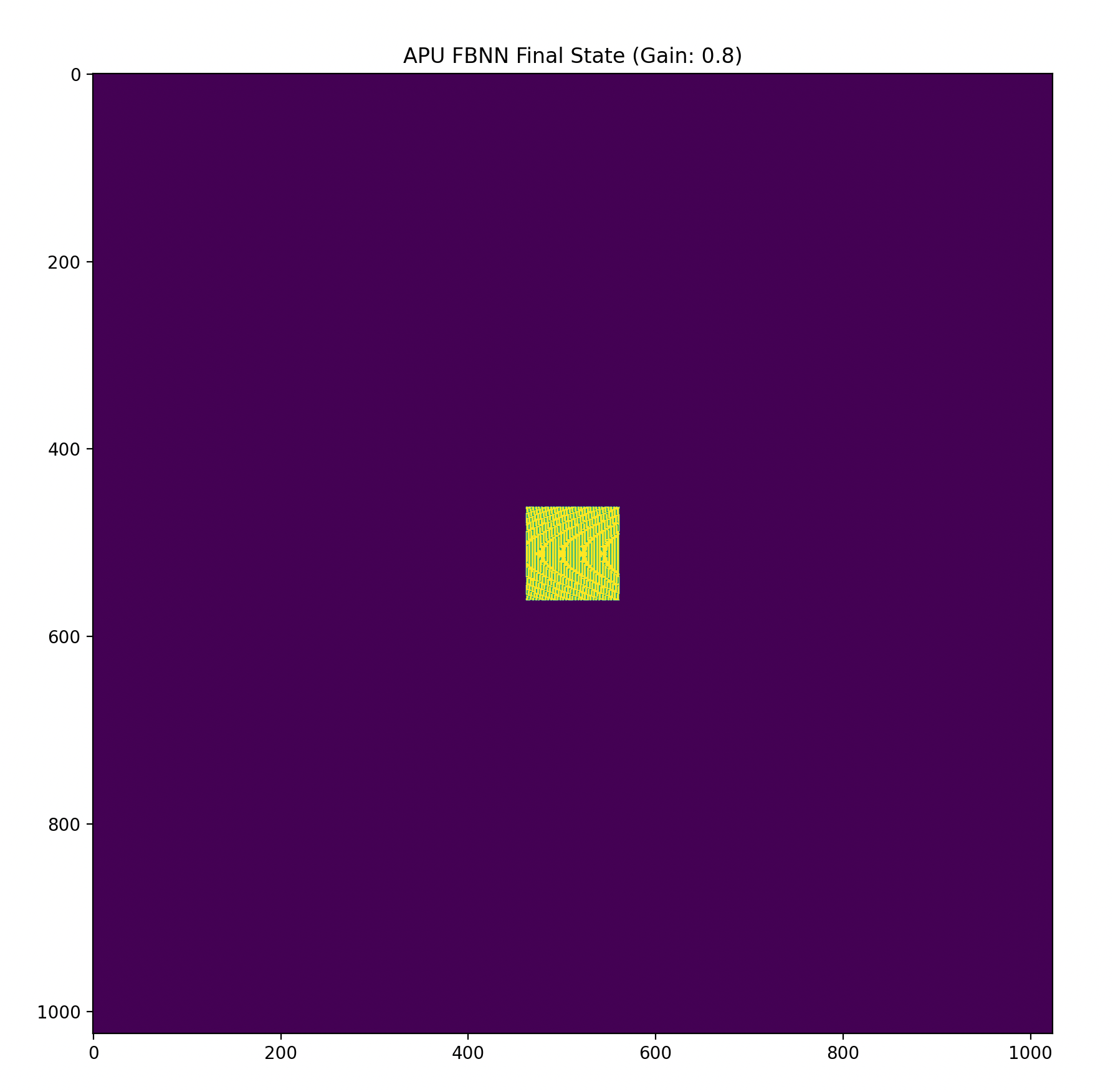

图2(输入数据前向传播影响驻波存储后到新的稳定态):

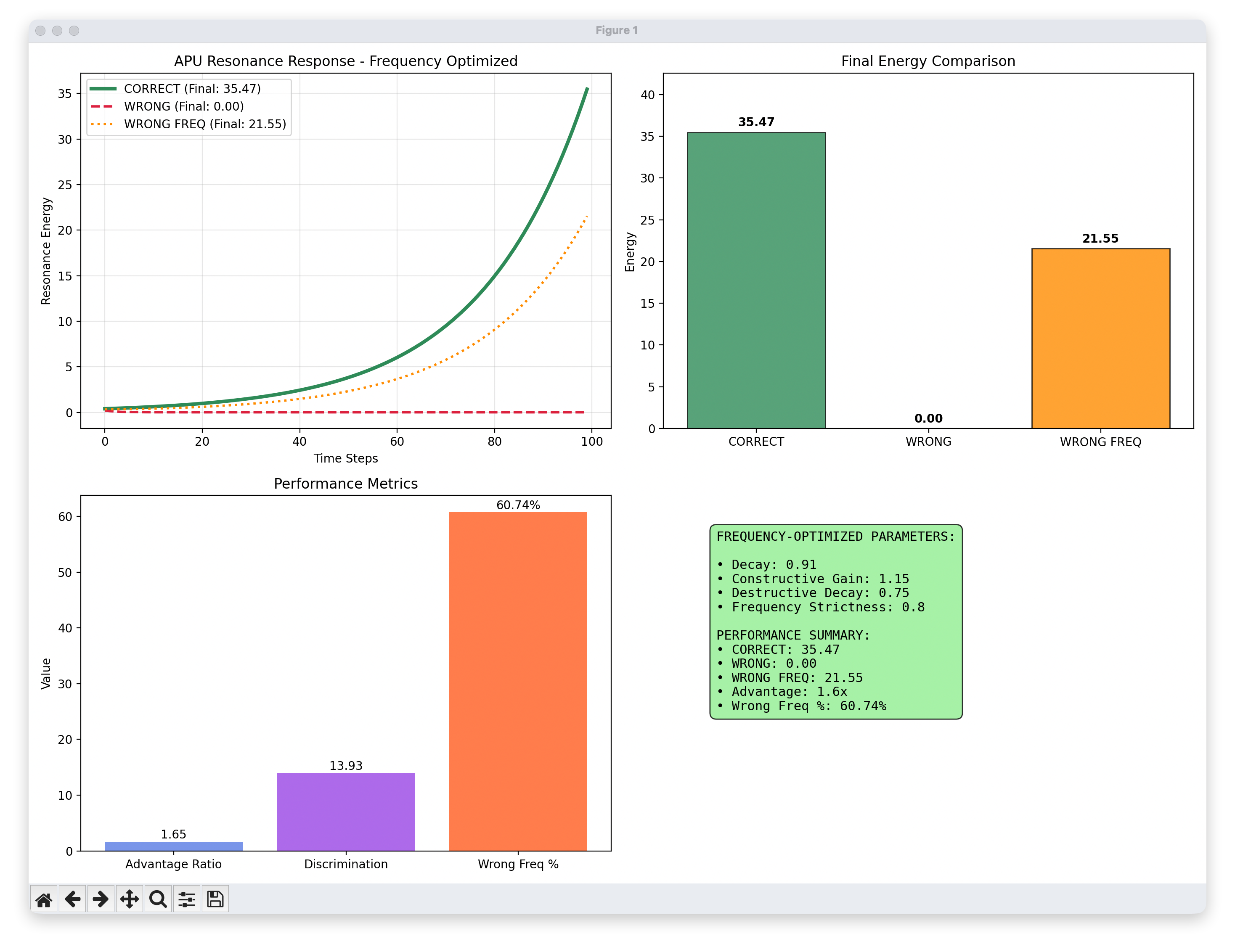

图3~5(制造材料设计及可行参数探索过程):

1682

1682

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?