1.为DUT选择合适的探测工具(如果是成熟的产品PCB板,探测点为PIN或者过孔时,此时需要选择对应的Prober,下图是测量差分信号的Prober)

单端Trace的或者过孔时Prober如下

2.连接DUT

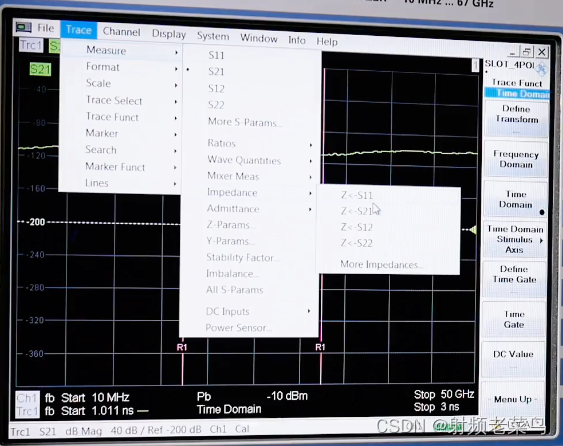

3.切换频域到时域

4.如何确定时域中实际待测物的阻抗起始时间

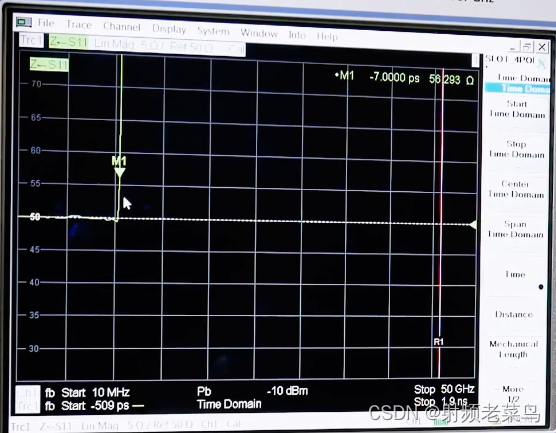

Cable不接任何东西,待时域阻抗稳定后,打上参考时间marker。

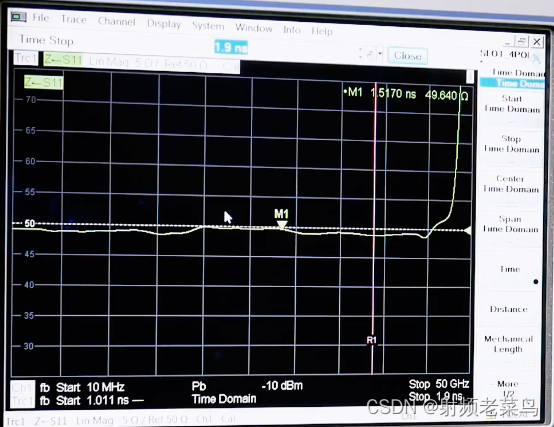

移动截止时间如下显示

那么如何区别待测物的起始时间呢?

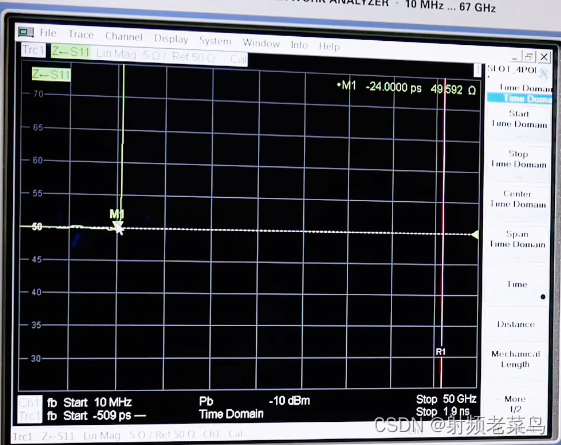

移除测试电缆,调整起始时间,等待阻抗稳定后,如下图marker点才是正确的起始时间

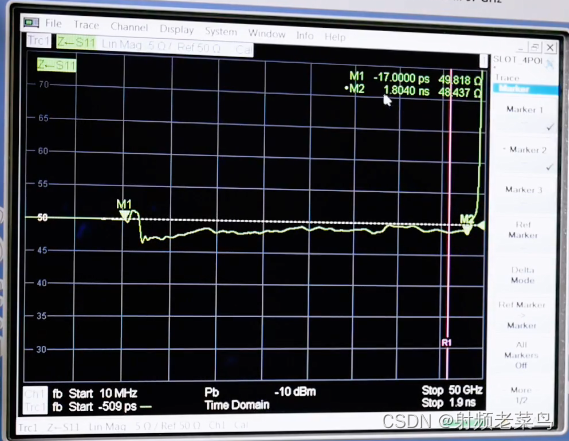

然后接上DUT,观看完整的阻抗时间

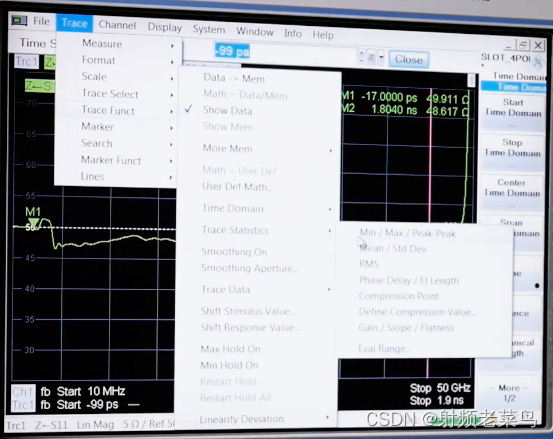

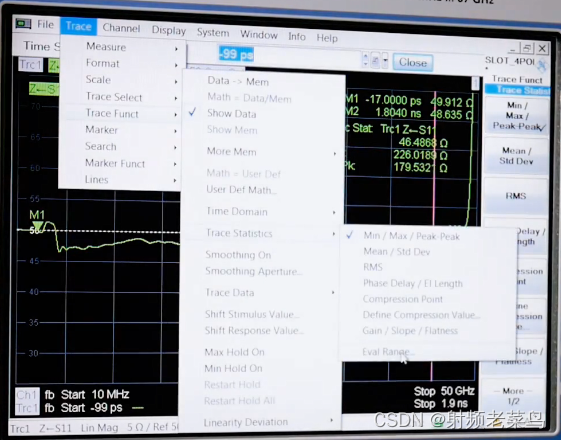

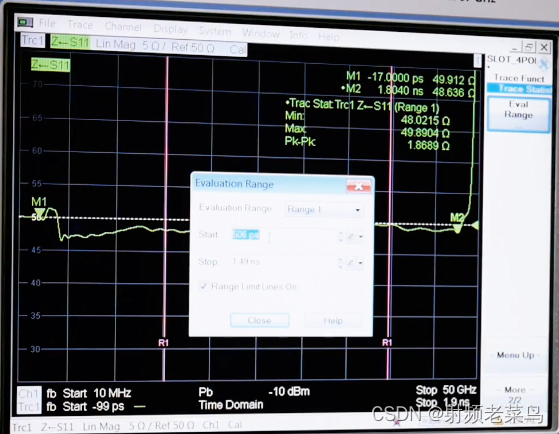

以下演示区间阻抗显示的功能(类似TDR)

1751

1751

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?