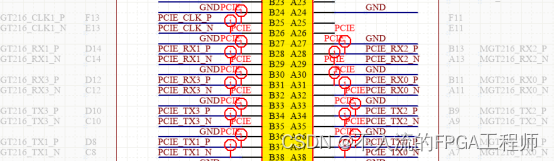

先上图,图1为自制底板的原理图,图2为官方底板的原理图,可以看出自制底板的rx和tx管脚和官方是相反的,这就导致了主机的设备管理不能识别到xdma设备(复位信号也可能导致不识别,故先确认复位信号),这是物理层的接线原因导致的,解决只有两种方案:重新画板和FPGA修改xdc约束,下面详细介绍xdc约束文件修改。

图1 自制底板原理图

图2 官方底板原理图

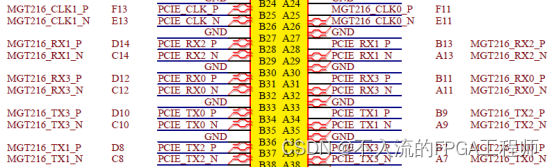

在bd文件中生成xdmaIP核后,找到底层的xdc约束文件,路径如下:

工程文件 \工程名.srcs\sources_1\bd\system\ip\system_xdma_0_0\ip_0\source。

该路径下拉到最后,可以看到一个xdc约束文件,如图3所示:

图3 xdc文件

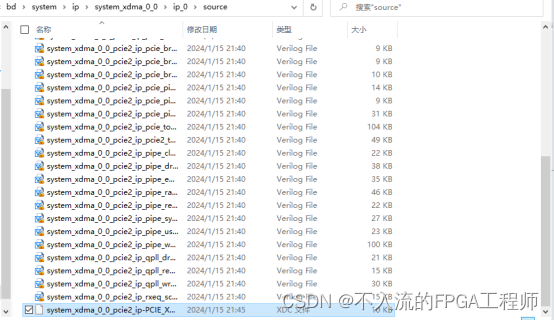

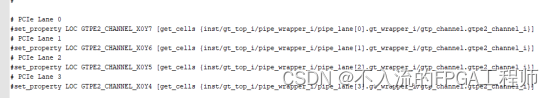

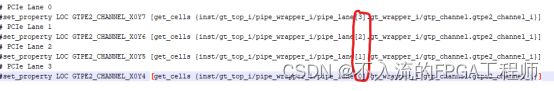

打开后可以看到所有的通道约束,由于此版本使用pciex4接口,故只有4路通道,如图4所示:

图4 原版底层xdc文件

此时绑定管脚是按照官方的顺序,我们要修改成自定义的顺序,修改后为下图所示:

图5 修改后xdc文件

修改后vivado中的bd文件就不要动了,如果重新generate后,该约束文件会恢复,需要重新修改。

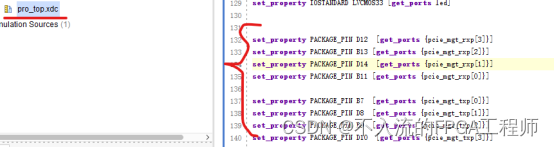

修改完底层后,在vivado中的顶层约束文件中按照自制板卡的引脚顺序去约束,如下图所示:

图6 vivado顶层自定义xdc文件

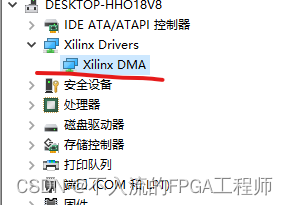

保存后就可以直接生成bit文件了,上板测试就可以看到设备可以识别。

图7 设备识别

当然这是rx和tx一起逆序了,也就是说rx0_p、rx0_n、tx0_p、tx0_n这四组仍然绑定在同一个区块中,从原来的x0y7变成了后来的x0y4,所以可以直接修改通道顺序,但是如果同一个通道中的rx和tx并非绑定在同一区块的高速引脚上时,就需要注意,可以先在底层同样位置的xdc文件中用户位置约束之前用{}设置空引脚:

set_property PACKAGE_PIN {} [get_ports RX0_P]

set_property PACKAGE_PIN {} [get_ports RX1_P]

set_property PACKAGE_PIN {} [get_ports RX2_P]

set_property PACKAGE_PIN {} [get_ports RX3_P]

然后把引脚约束成自定义引脚:

set_property PACKAGE_PIN B11 [get_ports RX0_P]

set_property PACKAGE_PIN D14 [get_ports RX1_P]

set_property PACKAGE_PIN B13 [get_ports RX2_P]

set_property PACKAGE_PIN D12 [get_ports RX3_P]

然后打开工程,在顶层的xdc中加入约束,注意极性:

set_property PACKAGE_PIN {} [get_ports {pcie_mgt_rxn[0]}]

set_property PACKAGE_PIN {} [get_ports {pcie_mgt_rxn[1]}]

set_property PACKAGE_PIN {} [get_ports {pcie_mgt_rxn[2]}]

set_property PACKAGE_PIN {} [get_ports {pcie_mgt_rxn[3]}]

set_property PACKAGE_PIN A11 [get_ports {pcie_mgt_rxn[0]}]

set_property PACKAGE_PIN C14 [get_ports {pcie_mgt_rxn[1]}]

set_property PACKAGE_PIN A13 [get_ports {pcie_mgt_rxn[2]}]

set_property PACKAGE_PIN C12 [get_ports {pcie_mgt_rxn[3]}]

然后烧录板卡,重启电脑。

第二种方案我没试过,但是大致的操作流程是这样的,有需要可以自己尝试一下。

7551

7551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?