factory机制

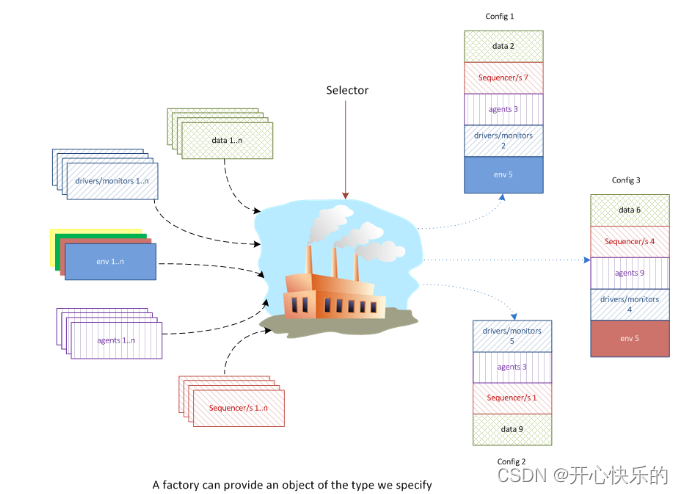

UVM factory is a mechanism to improve flexibility and scalability of the testbench by allowing the user to substitute anexisting class object by any of its inherited child class objects.

For this purpose, the factory needs to know all the types of classes created within the testbench by a process called asregistration.There are UVM macros that allow classes to be registered with the factory, and methods that allow certain typesand instances of class objects to be overridden by its derived types.

本文介绍了System Verilog和UVM中的factory机制,它通过允许用户用继承的子类对象替换现有类对象来提高测试平台的灵活性和可扩展性。重点讲解了Factory Override Methods中的set_type_override_by_type方法,该方法用于配置类型覆盖,将base_agent替换为child_agent,并通过示例展示了其效果。欢迎交流学习,相关文档可邮件索取。

本文介绍了System Verilog和UVM中的factory机制,它通过允许用户用继承的子类对象替换现有类对象来提高测试平台的灵活性和可扩展性。重点讲解了Factory Override Methods中的set_type_override_by_type方法,该方法用于配置类型覆盖,将base_agent替换为child_agent,并通过示例展示了其效果。欢迎交流学习,相关文档可邮件索取。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?