一、TS4RPSA2-3-3导电硅胶特性

SMT(Surface Mount Technology,表面贴装技术)导电硅胶作为一种创新型的电子元器件,是专为现代电子设备中线路与接地端子的连接需求而设计的。该产品凭借其独特的材料特性与结构设计,能够精准且稳固地通过表面贴装工艺焊接固定于印刷电路板(PCB)的指定位置,同时承担起高效接地的关键功能,成为了一种高度可靠的可用接地端子解决方案。

从材料科学的角度来看,SMT导电硅胶融合了硅胶材料的柔韧性与导电填料的优良导电性,展现出卓越的弹性恢复能力和稳定的导电性能。这种复合材料不仅确保了弹片在受到外力作用后能够迅速恢复原状,维持良好的接触压力,还保证了在复杂电磁环境下信号传输的稳定性和低阻抗特性。

此外,SMT导电硅胶在耐热性和耐久性方面表现尤为突出。相较于传统的金属弹片,它能够在更宽的温度范围内(-40°C至+150°C或更高,具体取决于材料配方)保持其物理和化学性质的稳定,不易因热应力导致断裂或变形,从而显著延长了产品的使用寿命。这种特性使得SMT导电硅胶特别适用于对环境适应性要求较高的应用场景,如汽车电子、工业控制等领域。

在印刷电路板的设计与应用中,SMT导电硅胶凭借其小巧的体积、灵活的安装方式以及优异的电气性能,能够轻松适应各种复杂的布局需求,被广泛应用于电路板上的任何需要接地的位置,为电子设备的稳定运行提供了坚实的保障。

二、TS4RPSA2-3-3导电硅胶电路防护

在电子设备复杂的内部构造中,导电硅胶扮演着极为关键的角色。它的主要作用在于,能够在不同的电路板之间搭建起稳固且可靠的连接桥梁。通过这样的连接,电流得以顺畅地传输,信号也能精准无误地传递,确保电子设备各个部件之间能够协同高效地工作。

导电硅胶之所以能够实现导电功能,其原理在于巧妙地利用了内部所含的金属颗粒或者碳颗粒所具备的导电特性。这些微小的导电颗粒均匀地散布在硅胶之中,使得硅胶整体拥有了良好的导电性能。当电流通过时,这些颗粒就像一条条畅通的道路,引导着电流顺利前行。

不仅如此,导电硅胶还具备出色的密封性能。能够有效地隔绝外界环境中的灰尘、湿气、化学物质等不利因素,为电子设备提供可靠的保护,延长其使用寿命。

三、产品特点

- 低阻抗,高回流焊强度

- 耐高温,阻燃

- 优异的弹性和回弹性

- 卓越的缓冲保护性能,耐化学腐蚀特性

- 合RoHS标准,无卤素认证

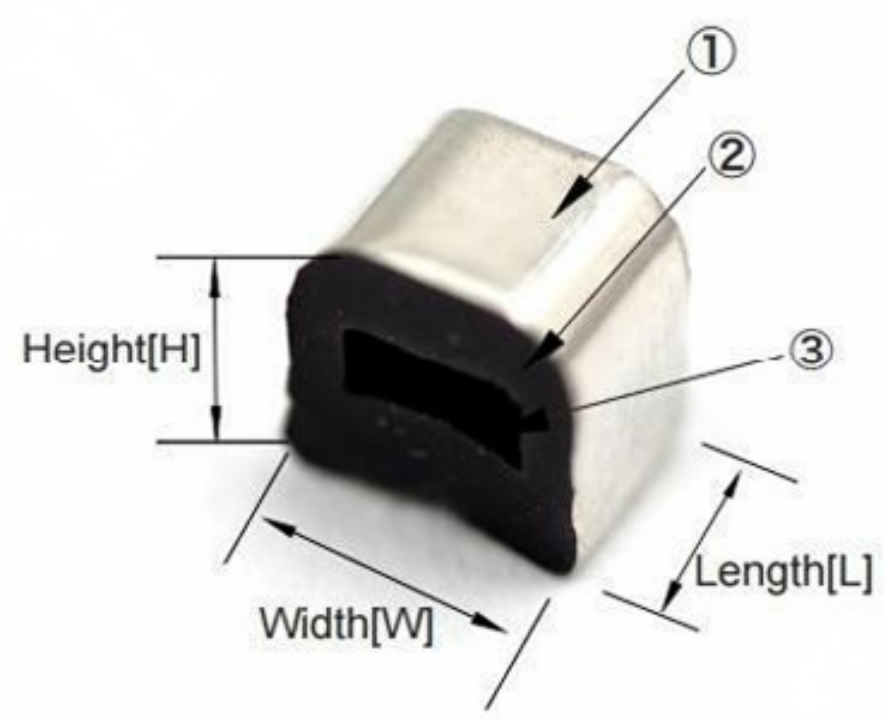

四、产品结构

|

① 聚酰亚胺薄膜+镀锡或镀金/镍的铜层 |

|

② 粘合剂 |

|

③ 硅橡胶管 |

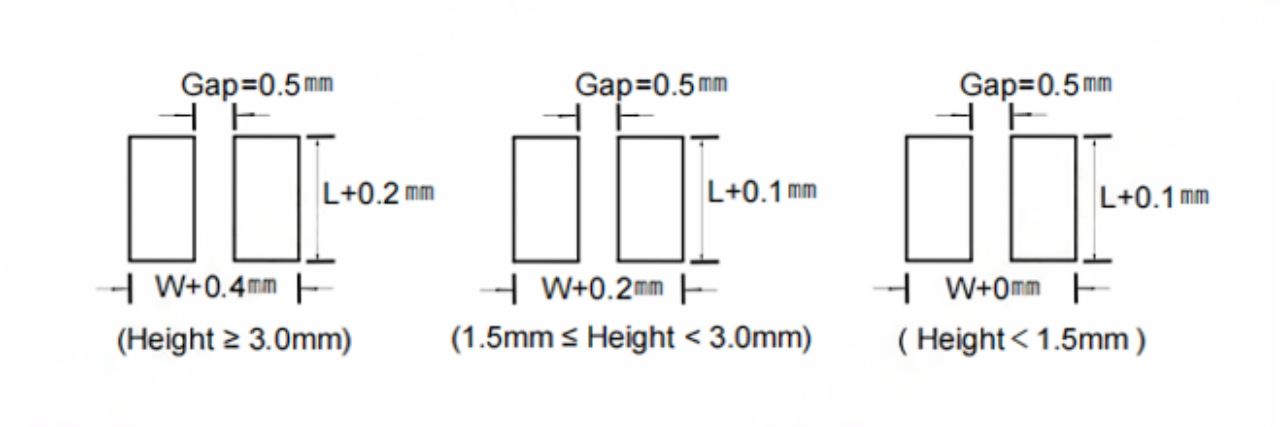

五、建议焊盘

六、产品应用

电气接地、电接触、电磁干扰/静电放电解决方案,以及液晶显示器、等离子显示屏、手机、导航仪、显示屏、柔性印刷电路板、天线、触摸屏等电子消费领域的产品抗冲击与振动解决方案。

七、产品规格和电气特征

|

Test item |

Test standar |

Test results |

Unit |

|

Color |

/ |

silver/Gold |

/ |

|

Hardness |

GB/T 531.2200 |

50±5 |

Shore C |

|

Instant temperature |

GB/T 2423.2 |

400 |

℃ |

|

Long-term temperature |

GB/T 2423.2 |

-40~+150 |

℃ |

|

Surface resistance |

ASTM F390 |

≤0.05 |

Ω/inch2 |

|

Vertical resistance |

ASTM F390 |

≤0.05 |

Ω |

|

Rebound rate |

ASTM D3574 |

>90 |

% |

|

Weld strength |

/ |

≥900 |

gf/cm |

|

Compression Range |

15%~30%、40%Max compression of original height | ||

753

753

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?