时源芯微 每天分享一个EMC相关内容,都是经验提炼,需要EMC整改,欢迎咨询

在排线设计中采用 π型RC滤波电路(由两个电容和一个电阻组成,结构形似希腊字母“π”)主要针对高频噪声抑制和多频段滤波需求,其优势及设计逻辑如下:

一、π型RC滤波的核心优势

1. 更强的噪声衰减能力

-

双电容结构:

输入和输出端各有一个电容(C1 和 C2),形成两级滤波:-

第一级滤波(C1+RC1+R):滤除高频噪声。

-

第二级滤波(R+C2R+C2):进一步抑制残留噪声,尤其是低频段的纹波。

总衰减率可达 -40dB/十倍频(单级RC为-20dB/十倍频),显著提升高频噪声抑制效果。

-

-

宽频段覆盖:

若采用不同容值的电容(如 C1=1nF 高频滤波,C2=10μF 低频滤波),可覆盖更宽噪声频谱。

2. 阻抗匹配与信号完整性

-

输入/输出阻抗优化:

π型结构通过电阻 RR 隔离前后级电路,减少信号源与负载间的相互影响,适合驱动低阻抗负载。

示例:若后级电路输入阻抗低(如功率放大器),单级RC可能导致信号衰减过大,而π型通过两级电容缓冲可改善此问题。 -

抑制反射噪声:

排线作为传输线易受反射干扰,π型滤波的电阻 R可吸收部分反射能量,减少信号振铃(Ringing)。

3. 电源与信号线的综合滤波

-

电源排线应用:

π型滤波常用于电源线(如DC-DC输出),同时滤除高频开关噪声(由C1抑制)和低频纹波(由C2平滑)。

示例:-

C1=100nF(陶瓷电容)滤除MHz级开关噪声。

-

C2=10μF电解电容)平滑100Hz~10kHz低频波动。

-

二、π型RC滤波的设计要点

1. 参数选择

-

截止频率:

以主噪声频段为目标,两级电容协同设计。

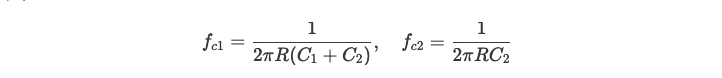

公式:

示例:

若需抑制1MHz以上噪声,选 R=50Ω,C1=1nF,C2=10nF,则 fc1≈265kHz,fc2≈318kHz。 -

电容选型:

-

高频电容(C1C1):低ESR陶瓷电容(如X7R/NPO),用于滤除开关噪声。

-

低频电容(C2C2):电解电容或钽电容,用于储能和抑制低频纹波。

-

-

电阻功耗:

电阻值需平衡滤波效果与功耗,避免过热。

公式:P=Irms2⋅RP=Irms2⋅R,电流较大时需选功率电阻(如1206封装)。

2. 布局与接地

-

短路径原则:

C1C1 和 C2C2 应尽量靠近噪声源和负载端,减少走线电感影响。

错误示例:长走线引入寄生电感(LparasiticLparasitic),可能在高频段形成LC谐振,反而放大噪声。 -

接地设计:

-

所有电容接地端需连接到同一低阻抗地平面。

-

避免共享敏感模拟地路径,防止地弹噪声耦合。

-

3. 与单级RC及LC滤波的对比

| 方案 | 优点 | 缺点 | 适用场景 |

|---|---|---|---|

| 单级RC | 简单、低成本 | 衰减率低(-20dB/十倍频) | 低频信号、小电流场景 |

| π型RC | 高频抑制强、阻抗匹配好 | 占用面积稍大、设计复杂 | 电源排线、高速数字信号 |

| LC滤波 | 低功耗、高频性能优 | 成本高、需防电感饱和 | 大电流电源、射频干扰抑制 |

三、典型应用场景

1. 高速数字排线(如HDMI、USB)

-

问题:信号边沿陡峭(高频谐波丰富),易辐射EMI。

-

方案:

-

在差分线对上加π型滤波(R=22Ω,C1=C2=100pF)。

-

抑制GHz级噪声,同时保持信号完整性。

-

2. 电源分配网络(PDN)

-

问题:DC-DC转换器的开关噪声通过排线耦合至敏感电路。

-

方案:

-

电源入口处使用π型滤波(C1=100nF,R=1Ω,C2=10μF)。

-

实测可将开关噪声(~1MHz)衰减30dB以上。

-

3. 传感器模拟信号排线

-

问题:长排线引入的50Hz工频干扰与射频干扰叠加。

-

方案:

-

π型滤波(C1=1nF 抑制射频,C2=1μF 滤除工频)。

-

配合屏蔽排线,信噪比提升20dB。

-

四、常见设计误区

-

盲目增大电容值:

过大的C2可能导致启动瞬间浪涌电流损坏电阻,需添加缓启动电路。 -

忽略电容谐振频率:

陶瓷电容在自谐振频率(SRF)后呈感性,高频段滤波效果下降,需并联多个容值不同的电容。 -

电阻值选择不当:

过大的RR会导致信号压降(如5V电源中R=100Ω,100mA电流时压降达10V),需根据负载电流调整。

五、总结

π型RC滤波通过两级电容+电阻的结构,显著提升对宽频噪声的抑制能力,尤其适合排线场景中的电源去耦、高速信号EMI抑制及长线传输抗干扰。设计时需注意电容频响特性、电阻功耗及布局优化,必要时结合频谱分析实测调整。对于极端高频或大电流场景,可升级为π型LC滤波或磁珠组合方案。

排线用π型RC滤波电路的优势与设计

排线用π型RC滤波电路的优势与设计

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?