DP1.4协议简介

HDMI(High-Definition Multimedia Interface,高清多媒体接口)和DisplayPort(DP)是目前最常见的两种视频传输接口。关于这两者的异同,参考该链接

https://baijiahao.baidu.com/s?id=1801245442762695709

最直接的区别就是外观

在上图左边是HDMI,右边是DP。

进入正题——DP1.4协议

DP接口信号:

1.HDP(热插拔)

2.AUX(辅助信息通道)

3.LANE0~3(数据传输通道)

DP上电工作流程:

主机检测到HPD

主机发送AUX指令读取EDID,获取显示器支持的分辨率,推荐时序等参数

主机发送AUX指令配置DPCD,设置带宽,LANE数目等

主机发送AUX指令配置DPCD,设置为时钟训练模式

主机LANE发送时钟训练信号(101010…)

主机发送AUX指令读取DPCD,确定时钟训练成功

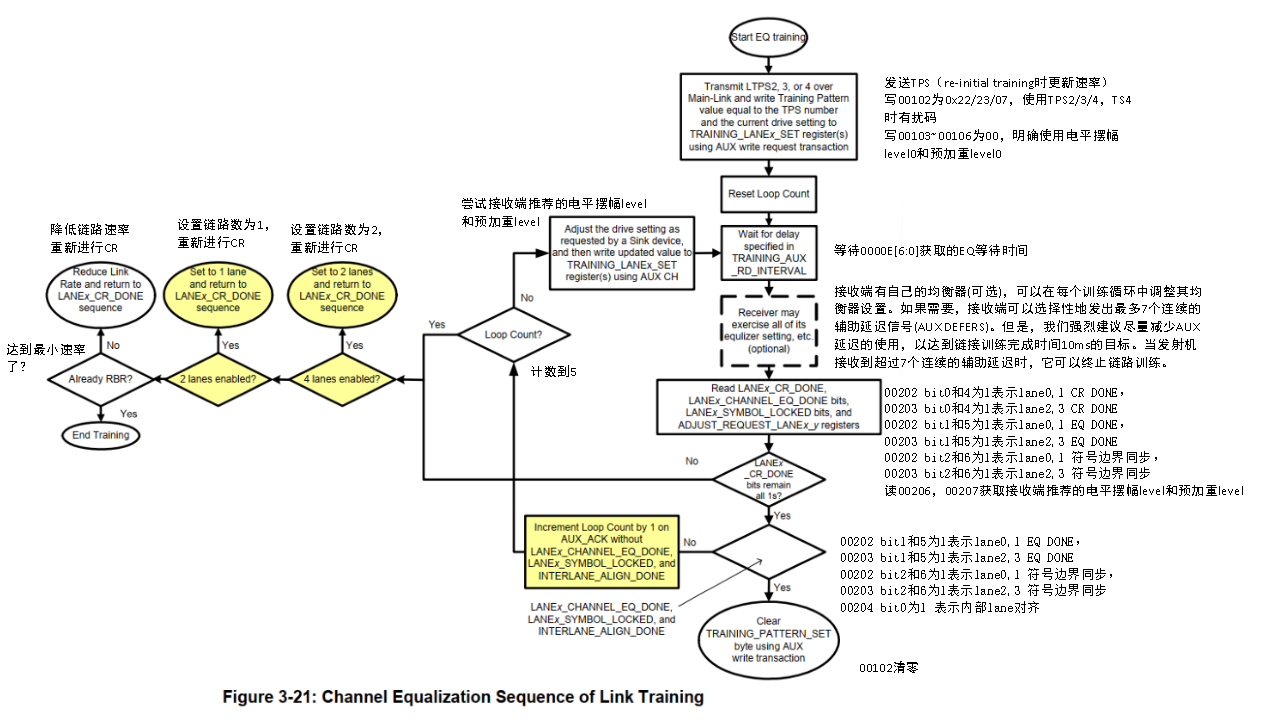

主机发送AUX指令配置DPCD为,设置为均衡训练模式

主机LANE发送均衡训练信号

主机发送AUX指令读取DPCD,确定均衡训练成功

主机发送AUX指令配置DPCD,设置为正常工作模式

主机LANE发送idle patten至少5个周期

主机LANE发送有效数据

HDP行为:

高电平有效

高电平持续超过2ms则判定线缆插入

接收方拉低0.5~1ms 表示接收方有一个中断请求

AUX行为:

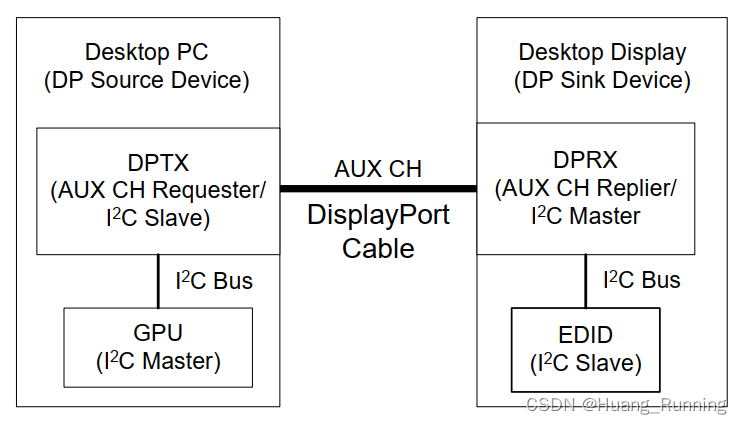

AUX负责发送方对接收方的寄存器读写包括EDID和DPCD

EDID内有显示器的显示能力和推荐时序等信息

DPCD内有DP接口的带宽等信息

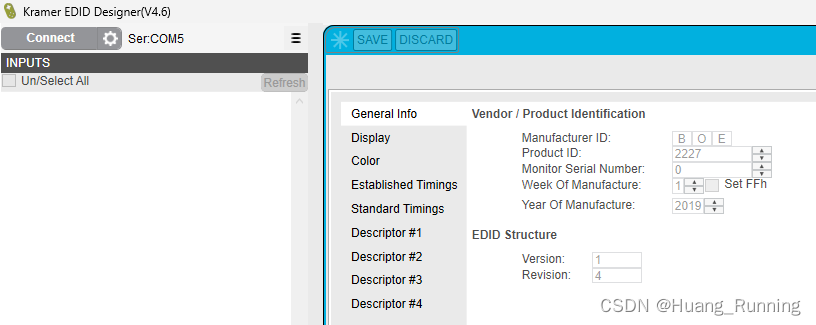

可以通过EDID Designer软件读取显示器的相关信息

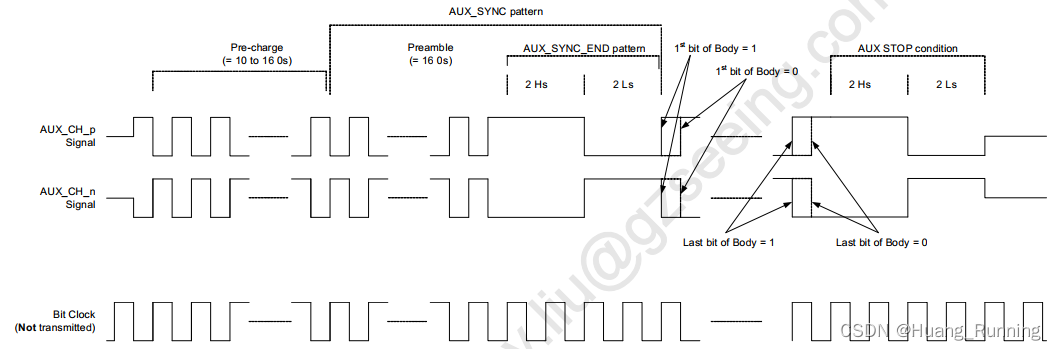

AUX物理层时序

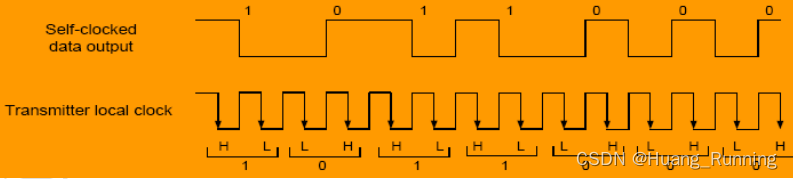

使用Manchester-II 编码两个时钟周期传递一个有效数据。

AUX物理时序

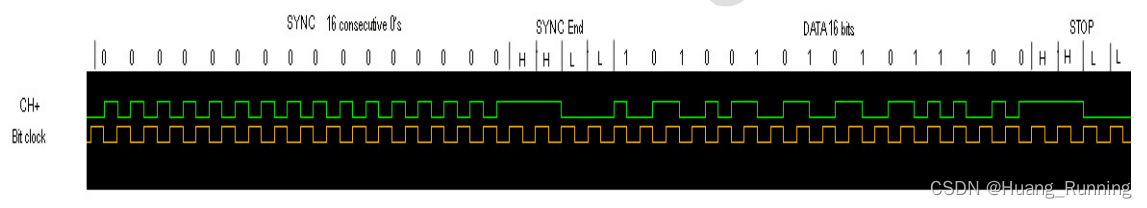

DP1.2:时序顺序

1.16个SYNC(16个0)

2.SYNC END(持续两个有效数据宽度的高电平,之后两个低电平)

3.DATA(一次AUX的DATA长度有限制)

4.STOP (持续两个有效数据宽度的高电平,之后两个低电平)

DP1.4:

与DP1.2相比,仅新增了预充电功能(10~16个0)

AUX语法(帧结构)

AUX是读写寄存器的接口,自然离不开读写指示,地址,数据这些东西。无非是为了可靠,增加了应答机制。

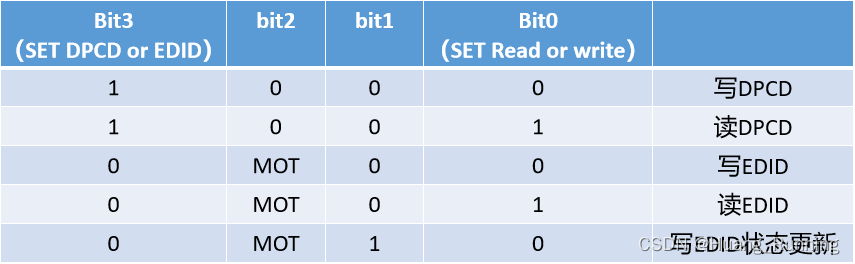

主机命令码

从机命令码

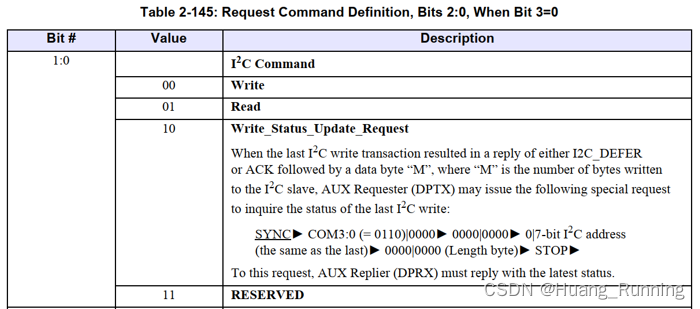

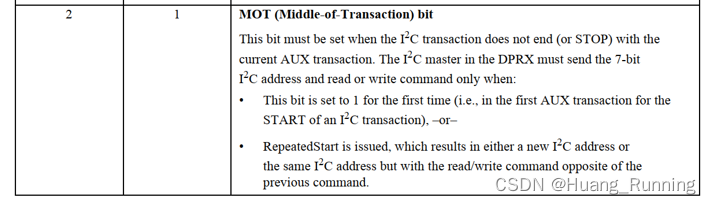

MOT与写状态更新具体描述

如上图,写命令下发后,从机应答未完成写操作之后主机发出write_Status_Update_Request从机应答最新的写操作状态。

如上图,表示一个完整的I2C over AUX操作还没完成DPRX里的I2C主机会发送7bit的I2C地址和1bit的读写位仅在下面两种情况发生

情况1:MOT第一次为1

情况2:MOT为1,读写位发生变化

主机写DPCD:

SYNC► 1000|ADDR19:16► ADDR15:8► ADDR7:0► LEN7:0► (DATA0_7:0► …)STOP

LEN7:0+1=写DATA个数。

从机应答写DPCD

SYNC◄ COMM3:0|0000◄ (DATA0_7:0◄ …) STOP

三种情况:

1 全部数据成功写入

SYNC◄ 00|AUX ACK|0000◄ STOP◄

AUX ACK=2’b00

2部分数据成功写入

SYNC◄ 00| NACK|0000◄ DATA0_7:0◄ STOP◄

AUX NACK=2’b01,DATA0表示已成功写入的字节数目

特殊情况:写地址不存在时DATA0为0

3从机BUSY

SYNC◄ 00|AUX_DEFER|0000◄ STOP◄

AUX DEFER=2’b10

主机读DPCD:

SYNC► 1001|ADDR19:16► ADDR15:8► ADDR7:0► LEN7:0► STOP

LEN7:0+1=读DATA个数

从机应答读DPCD

SYNC◄ COMM3:0|0000◄ (DATA0_7:0◄ …) STOP

4种情况

1从机BUSY

SYNC◄ 00|AUX DEFER|0000◄ STOP◄

2从机READY(此情况可能是读地址不存在)

SYNC◄ 00|AUX ACK|0000◄ STOP◄3从机只能被读取M个数据

SYNC◄ 00|AUX ACK|0000◄ DATA0_7:0◄ …DATAM_7:0◄ STOP◄

4从机能被读取全部N个数据

SYNC◄ 00|AUX ACK|0000◄ DATA0_7:0◄ …DATAN-1_7:0◄ STOP◄

特殊情况:读地址不存在,发送N个0

主机写I2C

I2C操作可以通过DPTX里的从机拉低SCL暂停

主机写I2C有如下情况

1 初始时发送没有长度字节的“Address-only”AUX事务

SYNC► 0100|0000► 00000000► 0|7-bit I2C address► STOP►

2 发送DATA(该DATA可以是I2C通信的寄存器地址或数据)

SYNC► 0X00|0000►00000000► 0|7-bit I2C address ► LEN7:0 ► Data0►… ► DataN ► STOP►

若I2C主机STOP,X(MOT)为0

3 发送结束(MOT为0)

SYNC► 0000|0000►00000000► 0|7-bit I2C address ►STOP►

4 要求从机汇报最新的写状态(用于从机应答表示没写完后)

SYNC► 0X10|0000►00000000► 0|7-bit I2C address ►STOP►

若I2C主机STOP,X(MOT)为0

从机应答写,有如下情况

1 成功

SYNC◄ 0000|0000◄STOP◄

2 BUSY(一个都没写入)

SYNC◄ 1000|0000◄STOP◄

3 部分完成

SYNC◄ I2C_ACK/I2C_NACK|00|0000◄ LEN7:0 ◄ STOP◄

LEN表示已写入的数据数目

300us内I2C可能没有写完,但是从机AUX必须发送响应,所以是I2C ACK但I2C部分完成

4 I2C设备地址无响应

SYNC◄ 0100|0000◄STOP◄

主机读I2C有如下情况

1 初始时发送没有长度字节的“Address-only”AUX事务

SYNC► 0101|0000► 00000000► 0|7-bit I2C address► STOP►

2 读DATA

SYNC► 0101|0000►00000000► 0|7-bit I2C address ► LEN7:0 ► STOP►

LEN7:0+1=读DATA个数

若从机应答不够DATA个数,主机会继续发同样的读指令

需要注意AUX设备一开始可能并不知道I2C主机要读多少个数,此时可设置LEN为一次AUX支持的最大值15。

3 读结束(MOT为0)

SYNC► 0001|0000►00000000► 0|7-bit I2C address ►STOP►

从机应答读,有如下情况

1 成功

SYNC◄ 0000|0000◄STOP◄

非数据指令,例如ACK,STOP

2 成功读出数据

SYNC◄ 0000|0000 ◄ DATA0_7:0◄ …DATAN-1_7:0◄STOP◄

3 I2C设备地址无响应

SYNC◄ 0100|0000◄STOP◄

DPRX里的I2C主机一定要ACK从机I2C的读数据,不能出现部分读出数据的I2C NACK情况

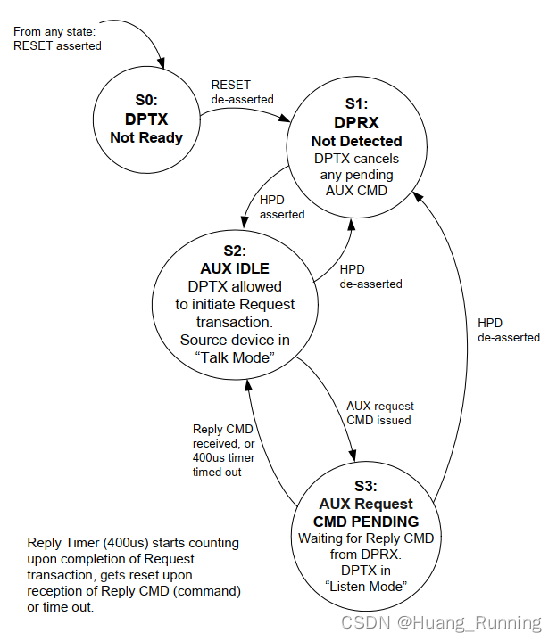

主机AUX状态机

RESET时进入S0

RESET后进入S1

HPD后进入S2

HPD消失进入S1

在S2状态发送AUX指令

在S3状态等待从机AUX响应,

若收到响应或超过400us没有收到响应,则进入S2

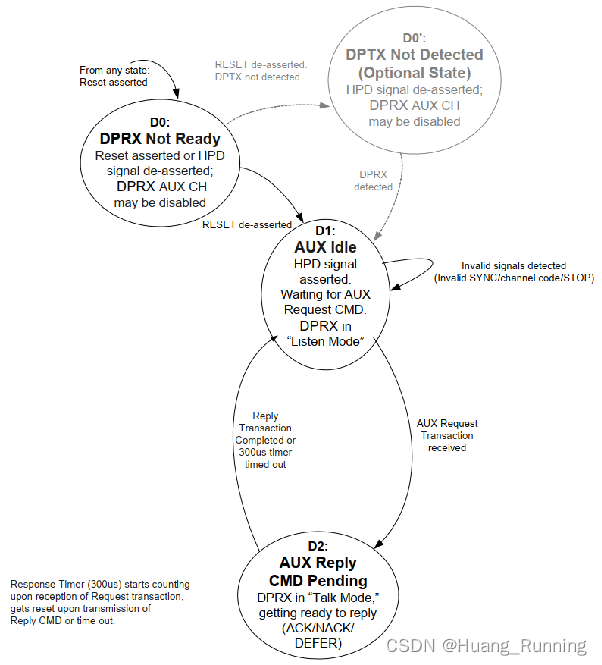

从机AUX状态机

复位进入D0

复位消失进入D1

接收到AUX指令后进入D2

发送完AUX应答后进入D1

300us内必须发出AUX应答

AUX配置DPCD

链路策略制定者必须通过AUX CH读取接收器能力和扩展接收器能力字段。然后,链路策略制定器必须根据DPRX的能力及其自身需求确定链路配置,然后写入以下链路配置参数:

•LINK_BW_SET寄存器(DPCD地址00100h)

•LANE_COUNT_SET寄存器中的LANE_COUT_SET字段(DPCD地址00101h,位4:0)

•DOWNSPREAD_CTRL寄存器(DPCD地址00107h)

•MAIN_LINK_CHANNEL_CODEG_SET寄存器(DPCD地址00108h)

在写入链路配置参数后,链路策略制定者必须通过AUX CH将21h写入training_PATTERN_SET寄存器(DPCD地址00102h)来开始链路训练,同时指示其发送器的逻辑PHY层开始发送训练模式。

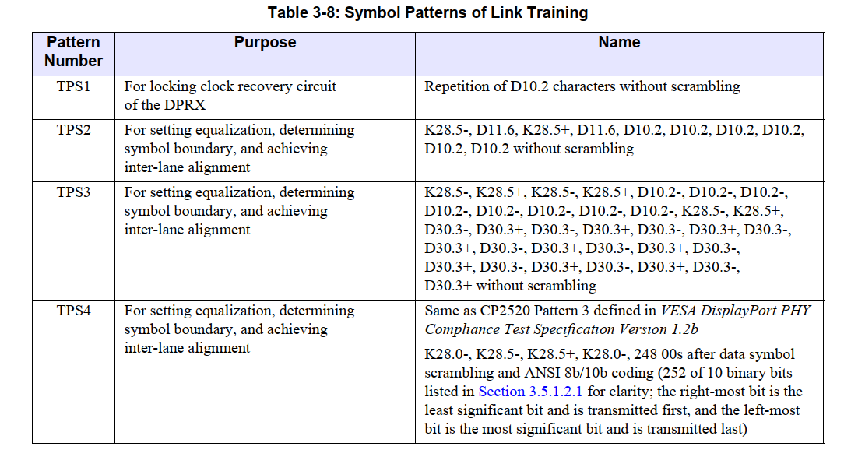

训练序列

TPS1用于时钟训练,TPS2是必须支持的均衡训练,TPS3,4是否支持,要读DPCD寄存器0x00002和0x00003。

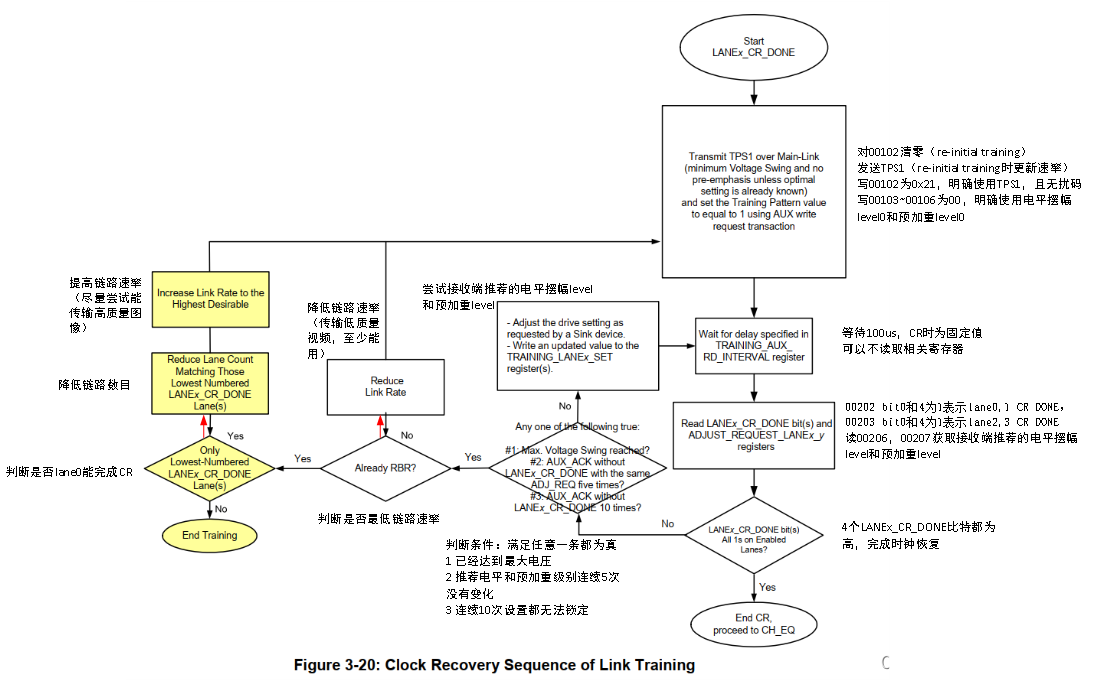

时钟训练和均衡训练

在写入链路配置参数后,链路策略制定者必须通过AUX CH将0x21h写入TRAINING_PATTERN_SET寄存器(DPCD地址00102h)来开始链路训练,同时指示其发送器的逻辑PHY层开始发送训练模式。

•时钟恢复–重复发送D10.2符号数据直到将DPRX CR(时钟恢复)PLL锁定

•信道均衡/符号锁定/lane对齐-如果成功,则必须在该序列结束时实现符号锁定和lane间对齐

链路维护

The downstream device must maintain the Link Status flags in the following registers duringnormal operation:

• LANEx_y_STATUS register(s) (DPCD Address(es) 00202h and 00203h)

• LANE_ALIGN__STATUS_UPDATED register (DPCD Address 00204h)

主机每隔一段时间查询上述3个寄存器,若异常则重新初始化。

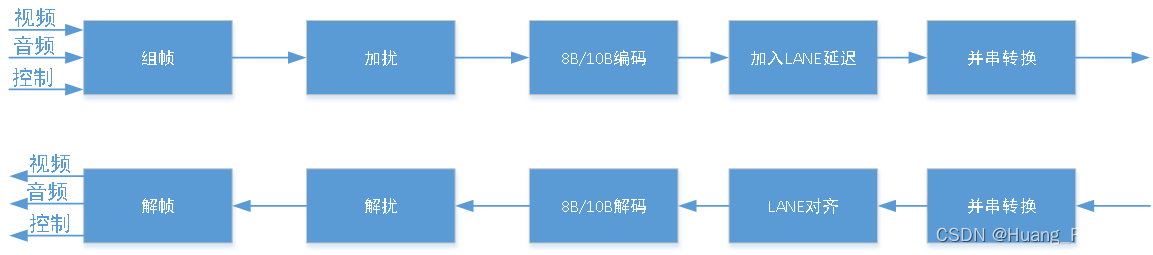

数据流处理流程

组帧

训练完成后,首先发送idle patten帧

有视频信号后根据视频扫描时序,每行一帧

这里帧是区别于视频帧的,或者说每行一帧是一个完整视频帧的子帧

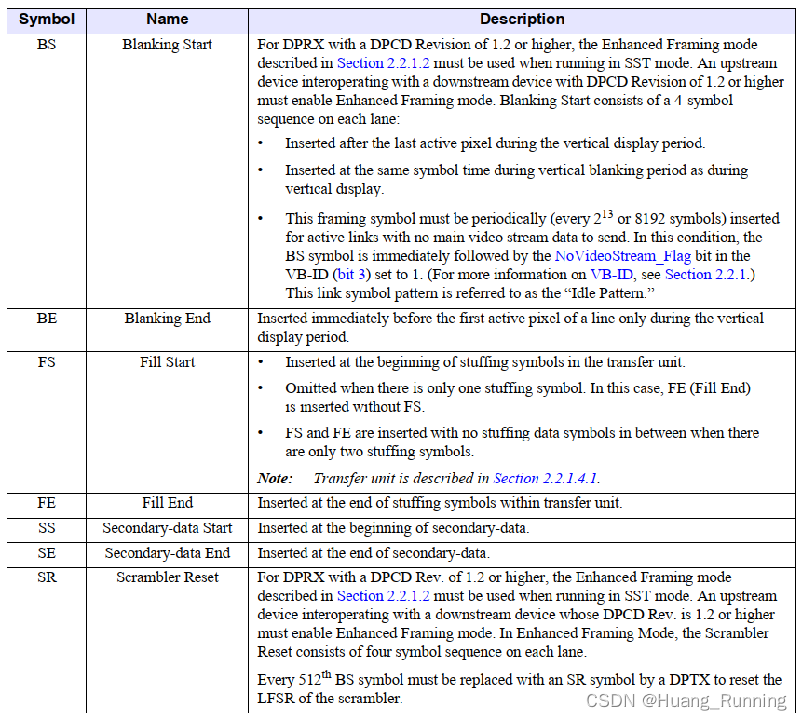

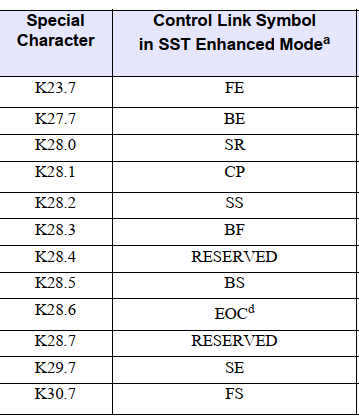

特殊字符定义

特殊字符使用的是8B/10B中的K码

增强帧头

从DP1.2版本开始,

1个字节的BS推荐改为4个字节,变为BS + BF + BF + BS

1个字节的SR推荐改为4个字节,变为SR + BF + BF + SR

A DPRX must support Enhanced Framing mode, and therefore must set the ENHANCED_FRAME_CAP bit in the MAX_LANE_COUNT register (DPCD Address 00002h, bit 7).

A DPTX must always enable Enhanced Framing mode by writing 1 to the ENHANCED_FRAME_EN bit in the LANE_COUNT_SET register (DPCD Address 00101h, bit 7)

帧头

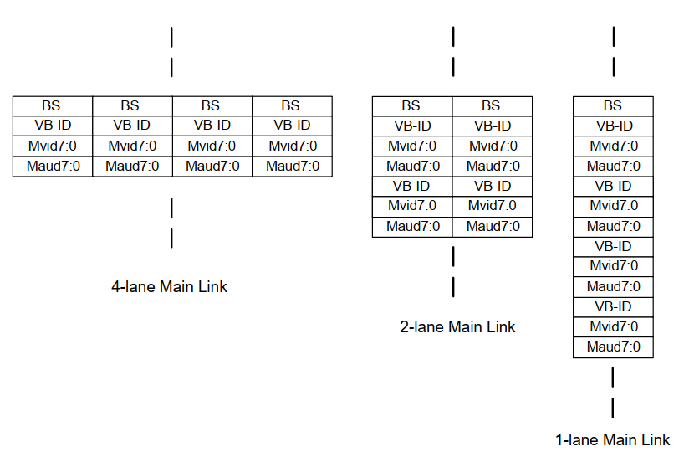

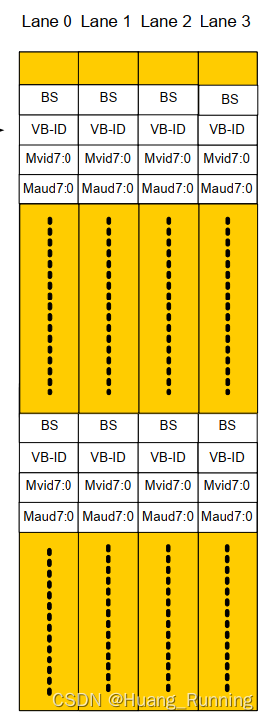

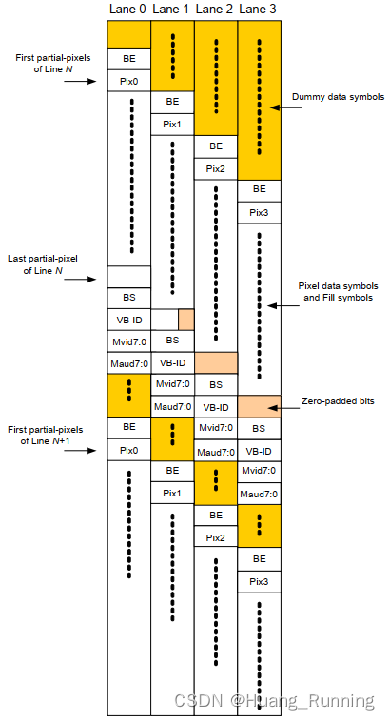

帧头由BS, VB-ID,Mvid,Maud组成, VB-ID,Mvid,Maud的含义参阅DP手册需注意,根据不同lane的数目,BS后的VB-ID,Mvid,Maud数目不同所有lane合计要有4组同样的VB-ID,Mvid,Maud。

Idle pattern帧

Before changing the timing of the main video stream, the Source device must transmit the “idle pattern” (BS symbol followed by the NoVideoStream_Flag and VerticalBlanking_Flag bits in the VB-ID (bits 3 and 0, respectively) both set to 1 every 213 or 8192 LS_Clk cycles) until it is ready to insert the new Main Stream Attribute data during the vertical blanking period of the main video stream. At the very minimum, the Source device must repeat the idle pattern five times before inserting the new Main Stream Attribute.

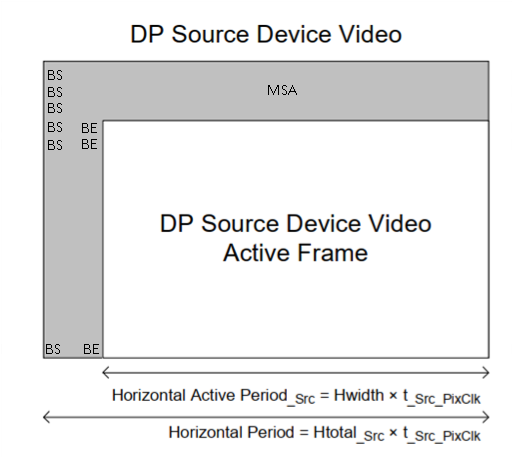

帧结构如上图所示,每8192个时钟为一帧。

视频行组帧

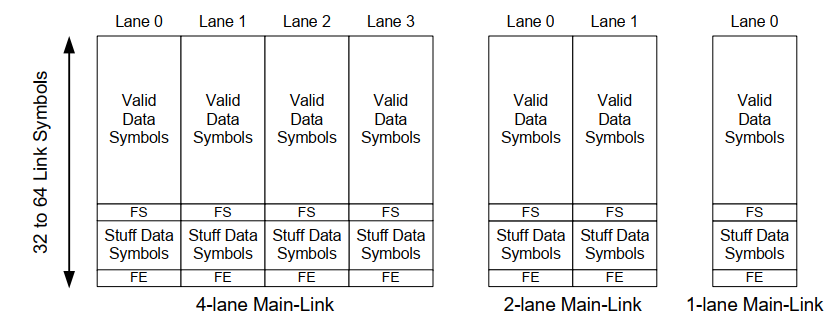

TU

由于DP的符号速率是大于原始视频流速率的,所以肯定需要填充多余符号。原始视频数据尽量均匀分布在符号流中,TU就是一种均匀分布的解决方案,TU中的FS和FE中间是填充的多余符号。每个TU为32到64个符号。要合理分配每个TU中的有效数据和填充数据,以免有效数据瞬间充满接收端缓存,从而导致图像显示出错。

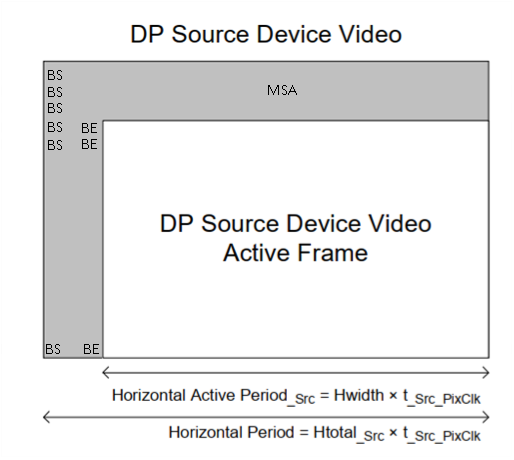

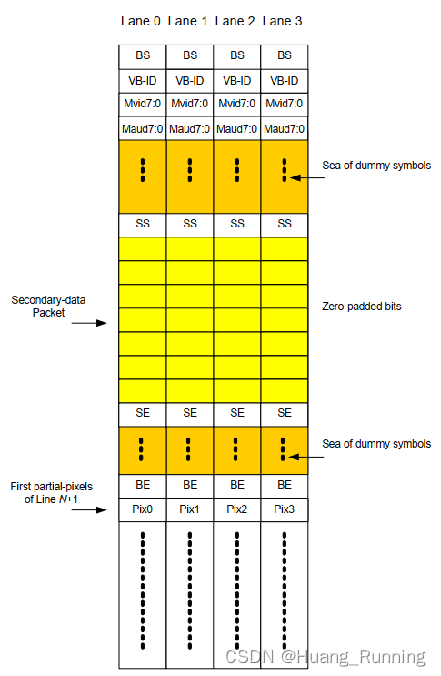

在列消隐期间,必须传递一个指示视频信息的控制数据子帧MSA。MSA帧结构如下图所示。具体字节定义见DP手册

在BS和BE间可插入音频或者控制数据,区别于MSA这些数据只用一个SS作为子帧头,如右图所示

扰码

每512行作为一个扰码周期,在BS时将扰码生成器置为到全1

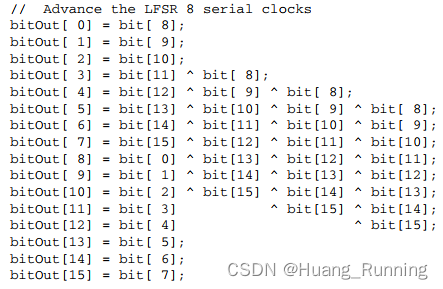

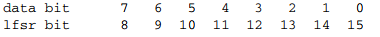

扰码生成多项式为 X16+x5+x4+x3+1(优快云显示的问题,实际上是第16位,第5位,第4位,第3位第1位做运算)

采用并行扰码,每个时钟周期更新8次后的扰码结果,计算方式如下

扰码数据与视频流data bit异或对应关系如下

LANE延时

LANE延时的加入应该是为了接收方LANE对齐因为多个LANE时,接收方使用不同的SERDES,SERDES里的缓存可能造成各个LANE延时不同

计算TU:

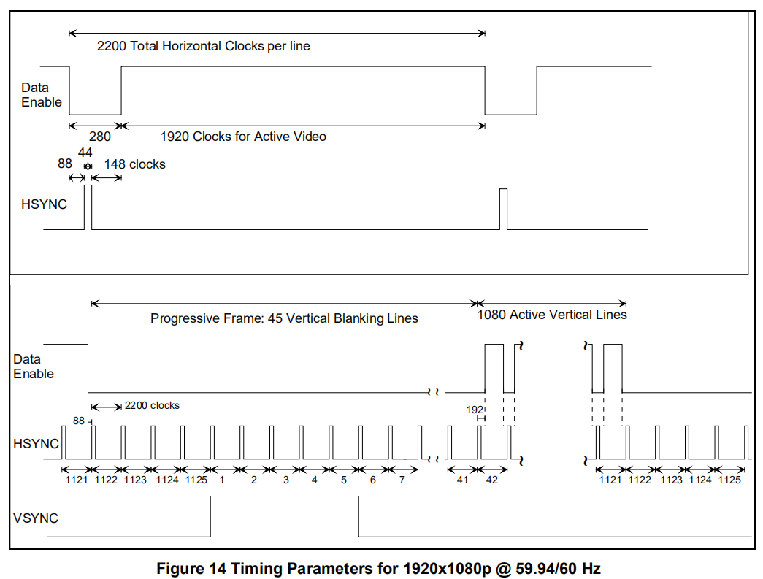

1,计算一行图像的数据量,视频格式以1920*1080,lane速率以8.1Gbps为例,需要先读取显示器的EDID获取显示器的参数

因为传输是用8B/10B,所以8.1Gbps/10=810MSymbol

算一行需要多少symbol,810M/60帧/(1080+45)行=12000symbol

2,算出一行实际需要的symbol,算出每条lane需要传输的数据量

1920pixel/4lane3byte=1440symbol

3,一行中有效的像素点与一行中总共的像素点的比值

1920/(1920+280)=x/12000,解得x=10473,此时x表示用10473个symbol来传输1920/4个像素点

4,每个TU长度假定为64symbol,这个长度可以从32~64,那么需要TU的数量为

10473/64≈163个

5,代码中每个TU有效数据最高为62/64,即最少也有两个填充。现在需要用163个TU,每个TU长度是64,来传输1440symbol,算出每个TU里面的有效数据,最后剩余的数据用填充字段TAIL

代码定义的是循环做163乘以62到1的模式,直到163x+b=1440,b为填充字段,不能大于163(这里有待确认,可能是64?)算出x=8,b=136,也就是说,总共有163个TU,每个TU的长度为64symbol有效数据为8个symbol,最后的填充字段是136个symbol

6,算出Blank长度,12000-163*64-136=1432symbol

7,

在要发送有效数据的行中,发送数据格式为BS->VB_ID->Mvid->Nvid->IDLE_SYMBOL(1432-5)->BE->TU(163个,每个TU有效数据为8symbol)->TAIL(136symbol)

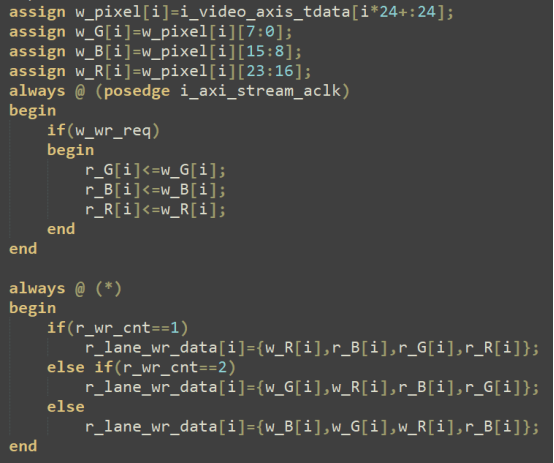

数据映射关系

2318

2318

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?