目录

1.算法仿真效果

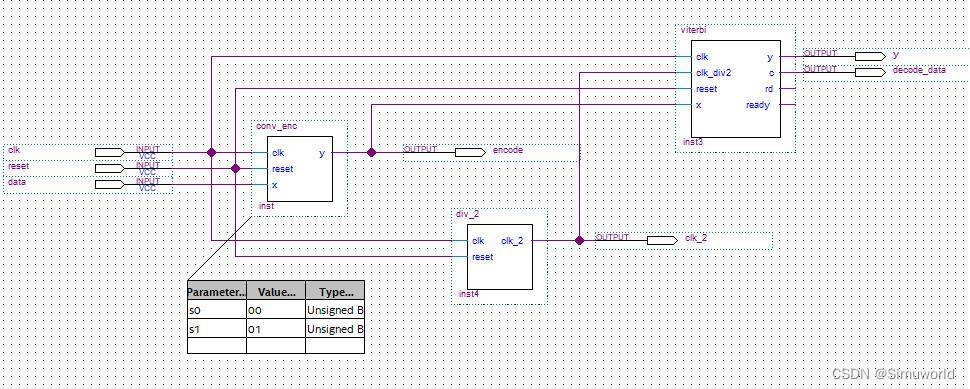

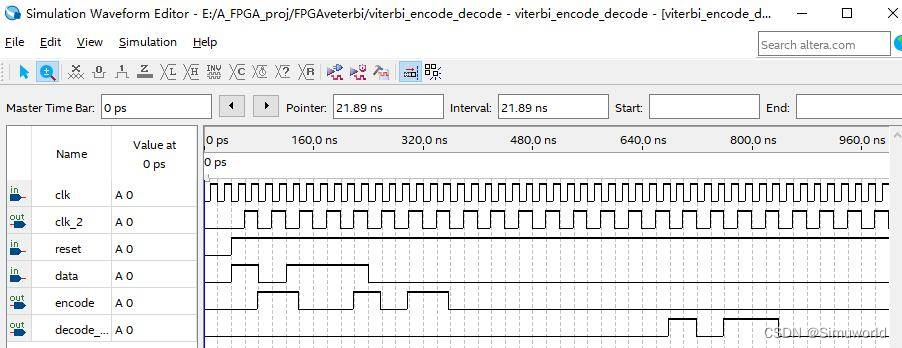

quartusii18.0仿真结果如下:

2.Verilog源码

%**********************************************************************************

%订阅用户如果对某一个算法感兴趣,可以私信留言文章链接和邮箱,分享任意一份完整代码,

%一般当天晚上或第二天下午4点前会将完整程序发到邮箱中。

%*********************************************************************************

always @(posedge clk) begin

if(!reset) begin //完成数

本文介绍了基于FPGA的维特比译码器Verilog实现,通过QuartusII18.0进行仿真。讨论了卷积码和Viterbi算法原理,强调了FPGA在译码器设计中的优势。提供了Verilog源码,并对比了软判决和硬判决译码的性能差异。

本文介绍了基于FPGA的维特比译码器Verilog实现,通过QuartusII18.0进行仿真。讨论了卷积码和Viterbi算法原理,强调了FPGA在译码器设计中的优势。提供了Verilog源码,并对比了软判决和硬判决译码的性能差异。

订阅专栏 解锁全文

订阅专栏 解锁全文

7105

7105

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?