题目1:FSM1(异步复位)

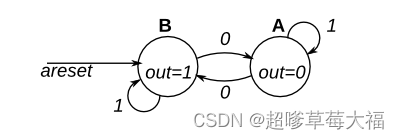

这是一个摩尔状态机,具有两个状态,一个输入和一个输出。实现此状态机。请注意,重置状态为 B。

此练习与fsm1s,但使用异步重置。

模块声明

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);

分析:

状态机的代码编写方式有三种:一段式,两段式和三段式。其中一段式不推荐,常用为两段式和三段式。两段式和三段式的区别在于三段式多了一个寄存器输出,在某些情形下能够消除电路中毛刺现象。

状态机有摩尔状态机和米利型状态机。其中摩尔状态机的电路输出只与触发器的状态有关,不受电路中输入信号的影响或者没有输入信号;而米利型状态机则不仅仅与触发器的状态有关,还受电路中的输入信号的影响。由此可知,摩尔状态机只是米利型状态机的特例。

代码使用两段式编写:

module top_module(

input clk,

input areset, // Asynchronous reset to state B,异步置零

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block,组合逻辑

// State transition logic

case(state)

A:next_state = in ? A : B;

B:next_state = in ? B : A;

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential al

Verilog 实现摩尔状态机:异步与同步复位

Verilog 实现摩尔状态机:异步与同步复位

这篇博客介绍了如何使用Verilog实现摩尔状态机,包括异步复位(FSM1,FSM2)和同步复位(FSM1S,FSM2S)。通过具体的代码示例展示了状态机的设计,强调了异步复位与同步复位的区别,并提供了完整的Verilog模块声明和逻辑实现。

这篇博客介绍了如何使用Verilog实现摩尔状态机,包括异步复位(FSM1,FSM2)和同步复位(FSM1S,FSM2S)。通过具体的代码示例展示了状态机的设计,强调了异步复位与同步复位的区别,并提供了完整的Verilog模块声明和逻辑实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?