错误 Error (10219): Verilog HDL Continuous Assignment error 不能将一个连续赋值(continuous assignment)应用于具有寄存器(reg)类型的对象。 在Verilog中,连续赋值使用 assign 关键字,它只能用于连接型(net type)变量(如 wire 类型、SystemVerilog 中增加的logic 类型)。 // 定义顶层模块

module top (

input wire clk, // 时钟信号

output reg [DATA_WIDTH-1:0] data_out // 数据输出

);

// 参数定义

parameter DATA_WIDTH = 8; // 数据宽度,根据需要调整

// 内部信号声明

wire [DATA_WIDTH-1:0] q_sig;

// 将顶层模块的端口连接到内部信号

assign data_out = q_sig;// Error (10219): Verilog HDL Continuous Assignment error at ***.v(36): object "data_out" on left-hand side of assignment must have a net type

// 实例化

//…………

endmodule

// 定义顶层模块

module top (

input wire clk,

output wire [DATA_WIDTH-1:0] data_out // 数据输出变为wire

);

parameter DATA_WIDTH = 8;

wire [DATA_WIDTH-1:0] q_sig;

assign data_out = q_sig;

// 实例化

//…………

endmodule

for (i = 0; i < DEPTH; i = i + 1) begin

if (bPeak) begin

peak_index = i;

next_state = CHECK_A;

i = DEPTH - 1; // 这里修改了循环次数

end

end

for (j = 1; j < 12; j = j + 1) begin

if (data_buffer[(i+j) % DEPTH] > data_buffer[i]) begin

bPeak = 0;

j = 12; // 希望实现 break;

end

end

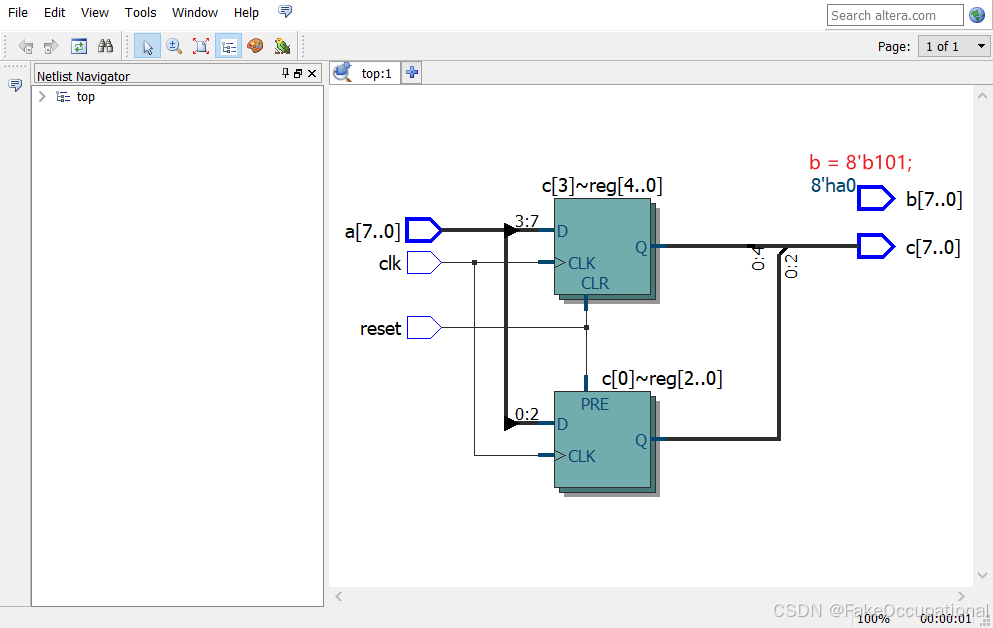

Initial Block Misuse in Synthesizable Code 综合工具通常(有时可以)不支持 initial 块(仅用于仿真),这里进行了讨论 。 module top (

input wire clk,

input wire reset,

input wire [7:0] a,

output reg [7:0] b,

output reg [7:0] c

);

initial begin

b = 8'b1;

c = 8'b1;

end

always @(posedge clk or posedge reset) begin

if (reset) begin

b = 8'b101;

c = 8'b111;

end else begin

c = a;

end

end

endmodule

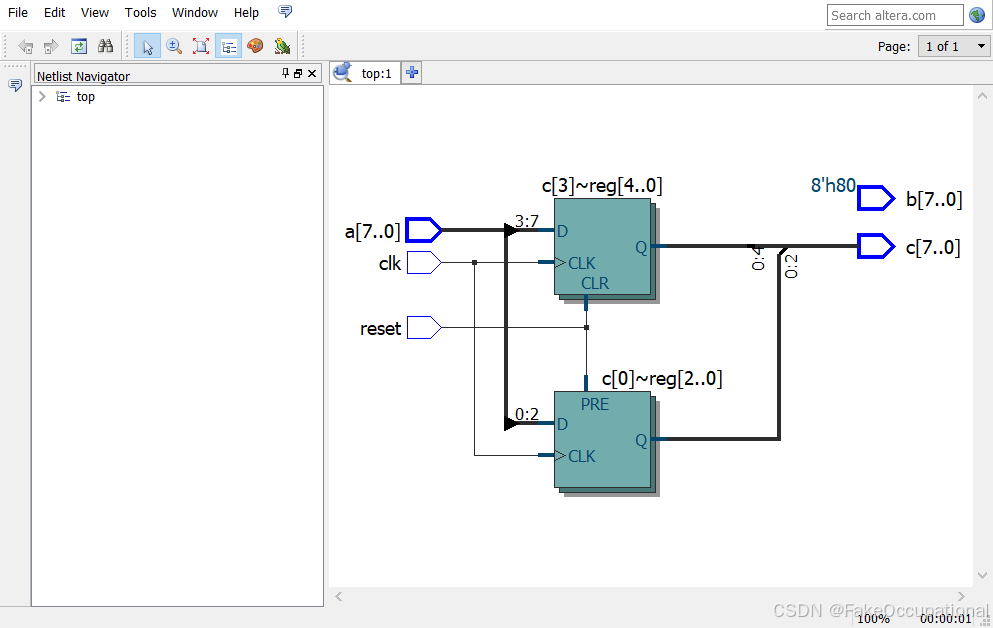

如果注释掉b = 8'b101;RTL结构如下(可以看到inital并没有被综合):

在综合代码中,用复位逻辑代替 initial 块。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?