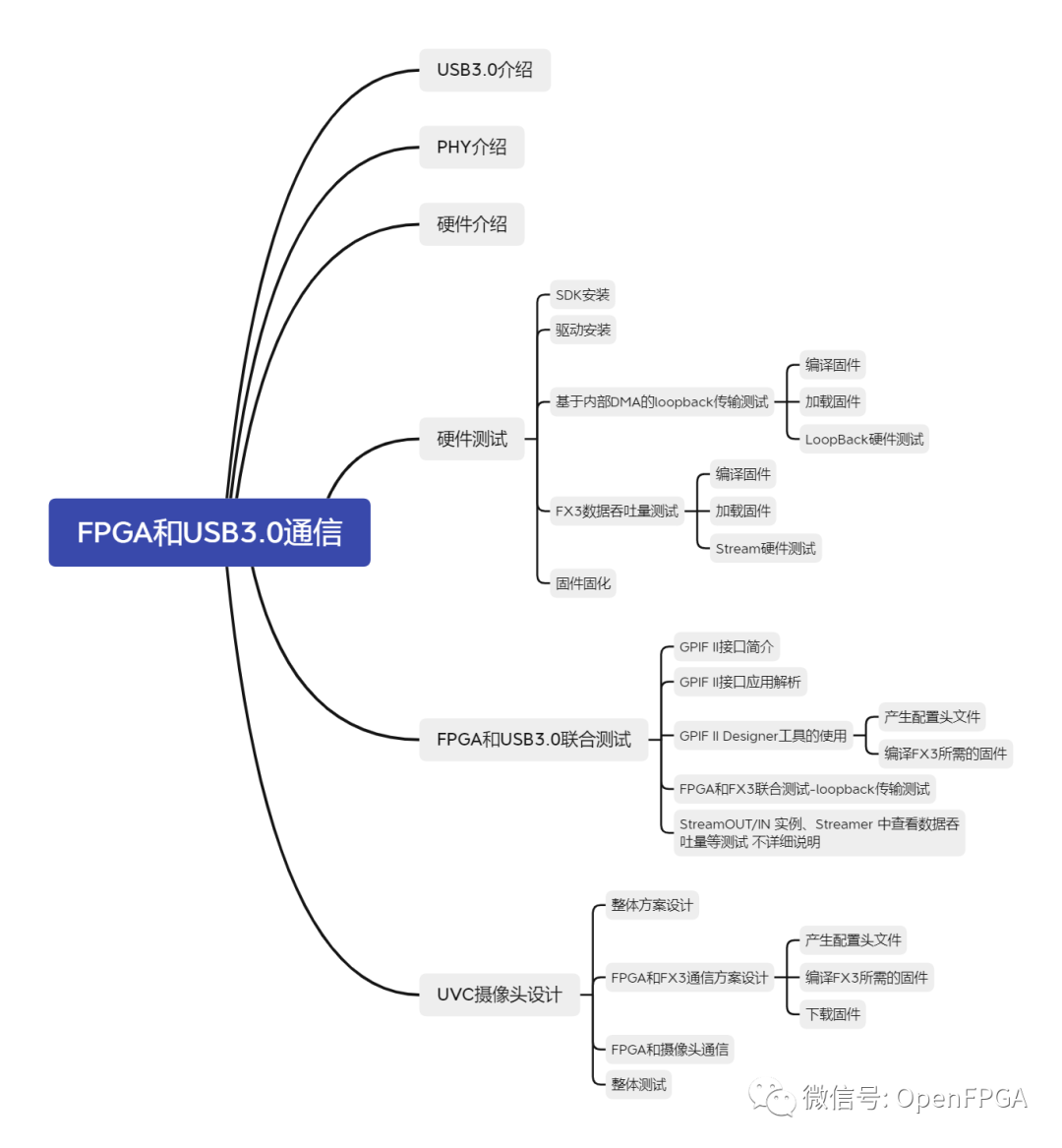

FPGA和USB3.0通信-联合测试(一)

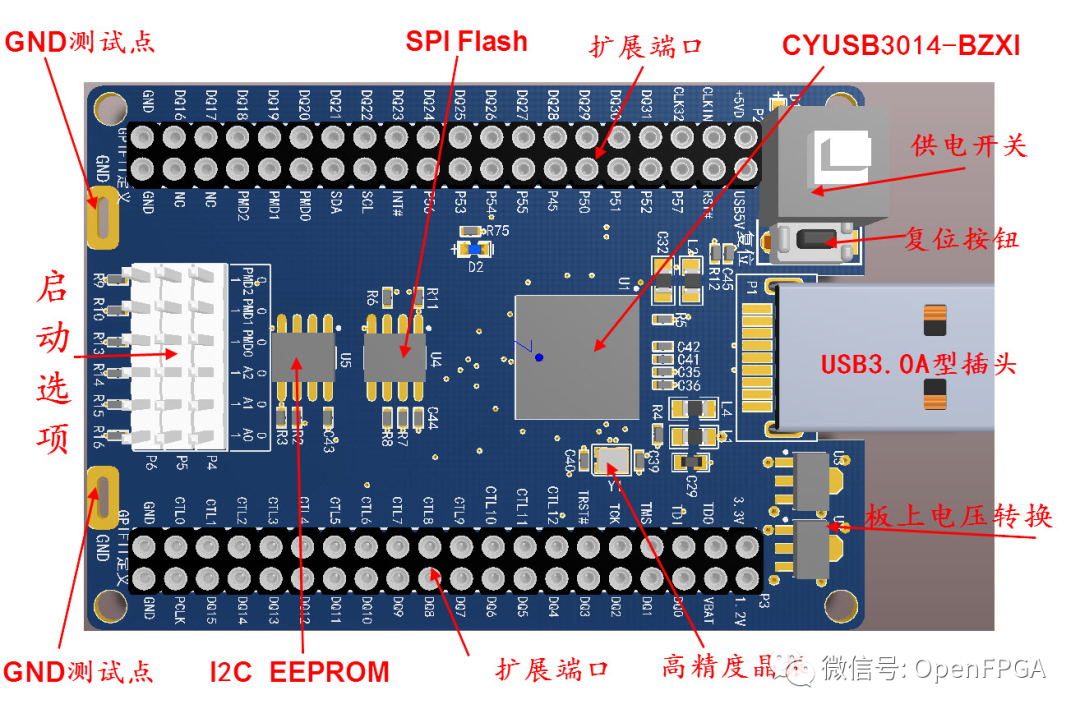

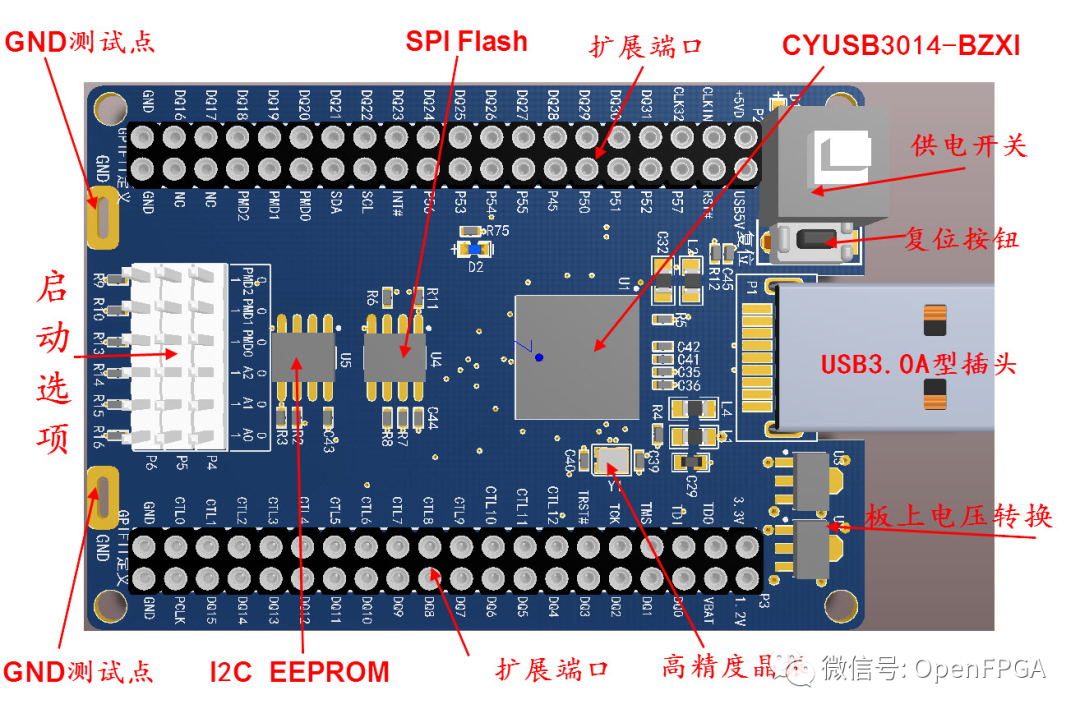

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写控制即可,同时该芯片还具有ARM核+I2S、I2C、SPI、UART等接口,大大增加了该芯片的使用范围。

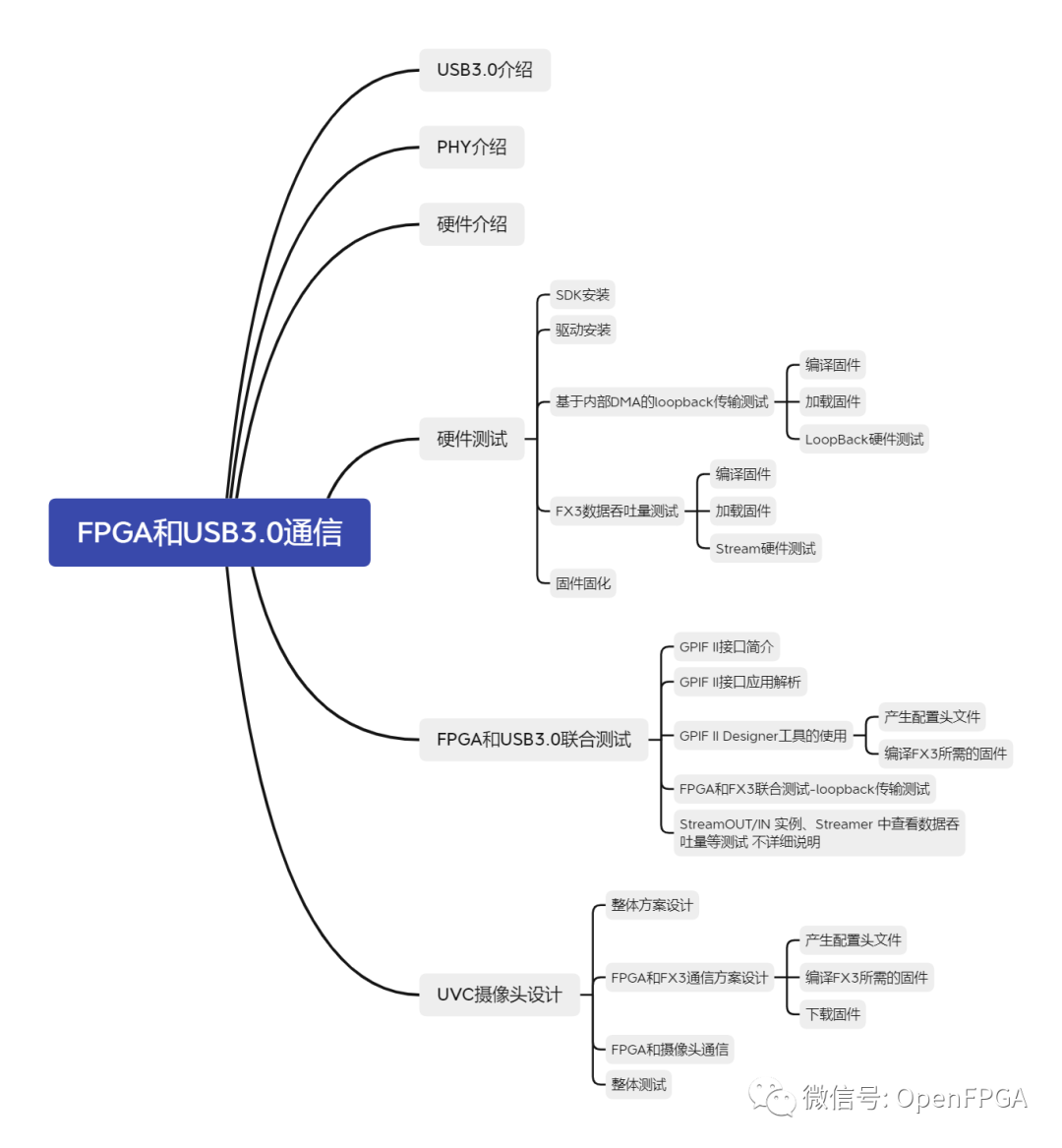

FX3应用中后半部分测试已经完成暨FX3和PC之间的通信:

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写控制即可,同时该芯片还具有ARM核+I2S、I2C、SPI、UART等接口,大大增加了该芯片的使用范围。

FX3应用中后半部分测试已经完成暨FX3和PC之间的通信:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?