小猫爪:S32K3学习笔记06-S32K3之BCTU

1 前言

大家好,又又又见面了,今天学习了以下S32K3的BCTU模块,BCTU其实就是一个专门的ADC硬件触发器,在ADC的文章中简单的介绍了一下,今天来对齐做个总结,如有错误的地方,希望大家留言指正。

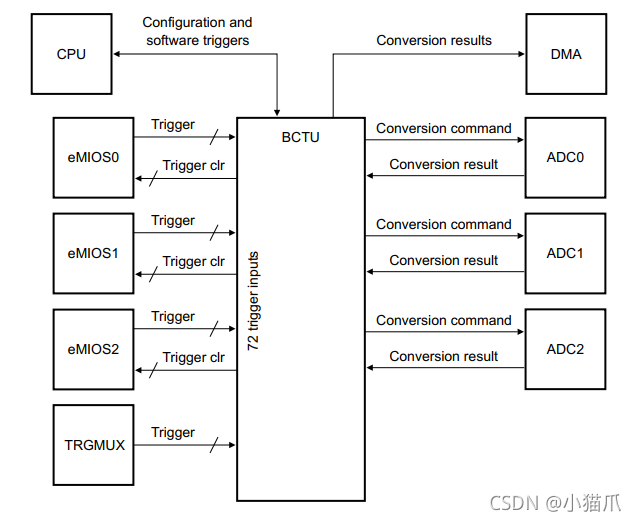

BCTU的功能实现如下所示:

BCTU接受来自CPU,eMIOS, TRGMUX的信号后产生ADC触发信号去触发ADC开始转换,ADC转换完成后再把结果返回给BCTU,BCTU可支持DMA搬运。

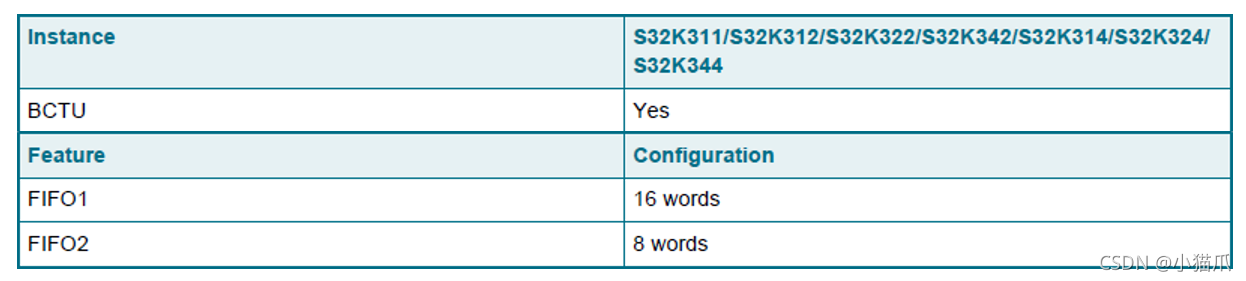

2 BCTU资源介绍

S32K3全系标配BCTU模块,除了三个结果寄存器之外,BCTU还有两个FIFO用来存储转换结果,并用来支持DMA传输。

3 功能介绍

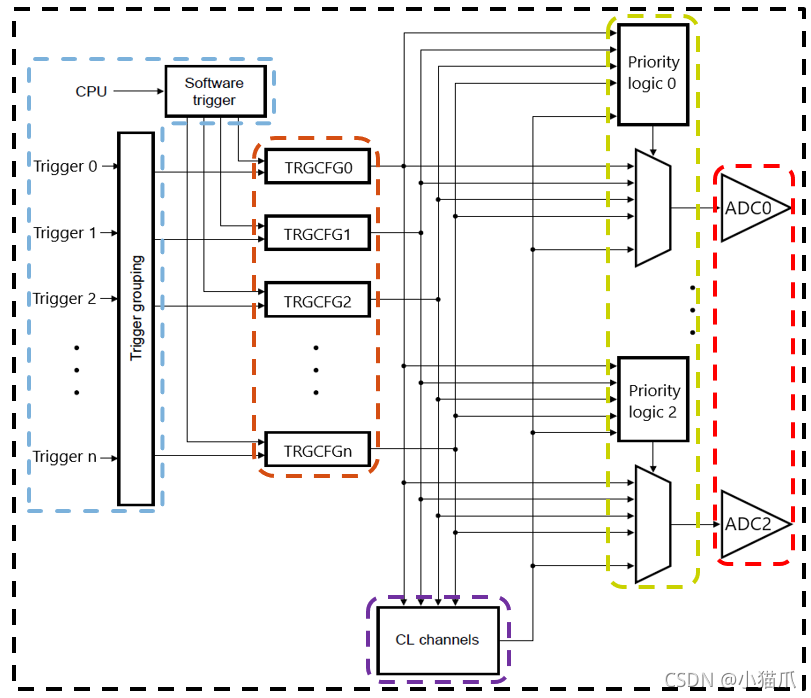

BCTU的功能框图如下:

上图非常简单,就不多作废话,下面补充几个上图没有的信息:

- BCTU一共支持72个触发信号,对应72个TRGCFG寄存器。

- 一个触发信号可以同时并行触发ADC0,ADC1,ADC2开始转换。

- K3处于STANDBY模式下, BCTU是不工作的。

- 可以通过使用CL来实现一个触发信号来触发一个转换队列。

3.1 触发信号

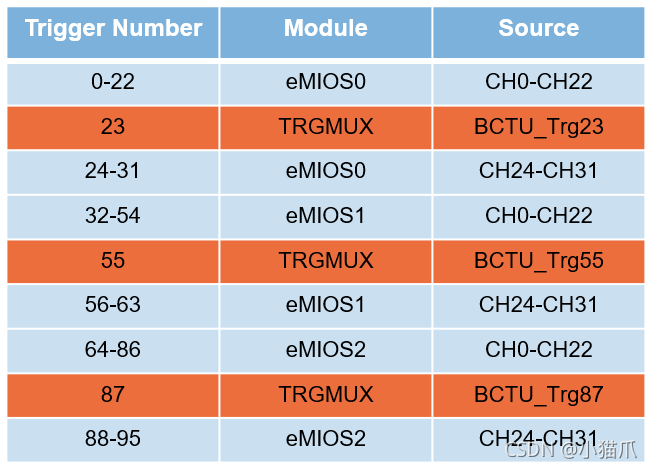

上面提到BCTU一共支持72个触发信号,那这72个信号分别是哪些呢?看下表:

从表格中可以非常的清楚的看到,大部分都是由eMIOS的输出信号来触发,还有3个则是由TRGMUX触发。

3.2 CL(Conversion list )

上面提到可以通过CL来实现一个触发信号来触发一个转换队列,其实意思很简单,我们只需要提前配置好这个转换队列,当这个触发信号过来后,BCTU就会根据这个转换队列来依次产生触发信号去触发ADC开始转换。这个队列最大支持32个。

在这里就不提具体是怎么实现的了,NXP的SDK包提供了非常方便的API借口来实现这个队列初始化功能,感兴趣的小伙伴可以去参考一下K3的RM手册BCTU章节。

3.3 DMA支持

BCTU的两个FIFO均支持申请DMA传输,我们可以预先设置好FIFO的watermask值,当FIFO里面的数据深度达到watermask值后就会产生DMA触发信号来申请DMA传输。

4 MCAL配置示例

待续。。。。。。

本文介绍了S32K3微控制器中的BCTU模块,它作为一个ADC硬件触发器,接收多种信号源触发ADC转换,并通过FIFO支持DMA传输。BCTU支持72个触发信号,每个信号可同时触发多个ADC,且具备转换队列(CL)功能,允许预配置转换顺序。此外,还详细说明了BCTU的资源、功能及配置示例。

本文介绍了S32K3微控制器中的BCTU模块,它作为一个ADC硬件触发器,接收多种信号源触发ADC转换,并通过FIFO支持DMA传输。BCTU支持72个触发信号,每个信号可同时触发多个ADC,且具备转换队列(CL)功能,允许预配置转换顺序。此外,还详细说明了BCTU的资源、功能及配置示例。

4257

4257

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?