五、常用电路的VHDL程序

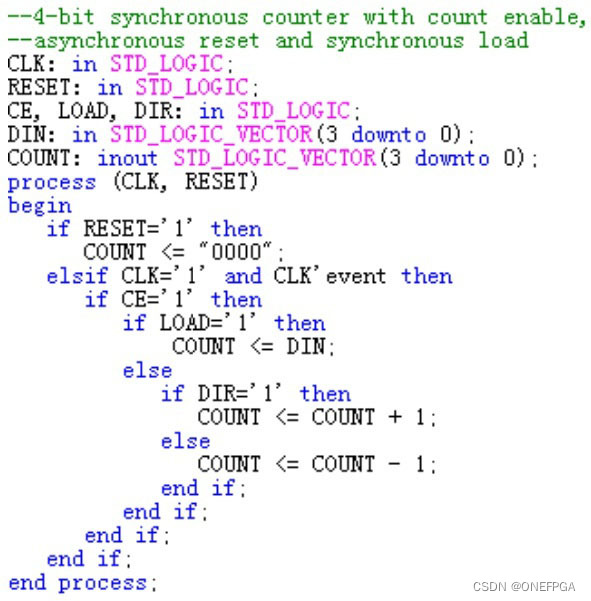

计数器:

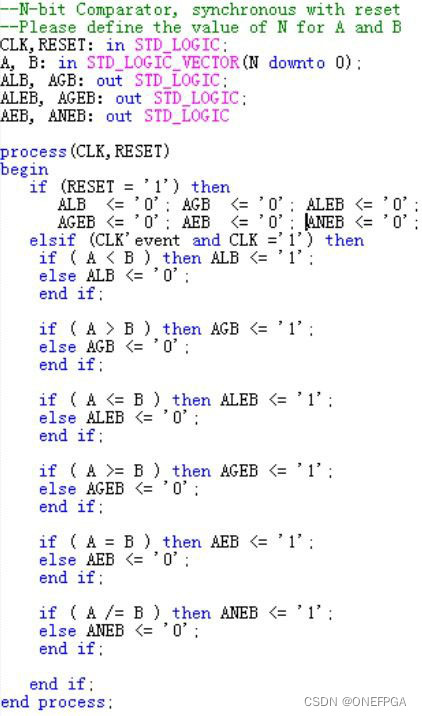

比较器:

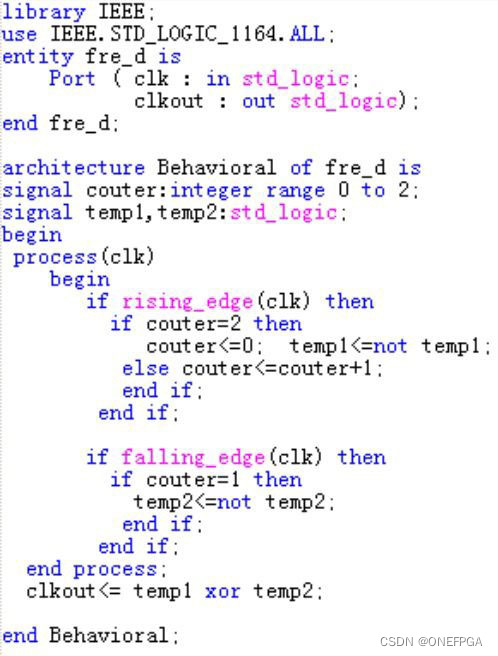

奇数倍分频:

8位奇偶校验电路:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY p_check IS

PORT (a: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

y: OUT STD_LOGIC);

END p_check;

ARCHITECTURE opt OF p_check IS

SIGNAL tmp: STD_LOGIC;

BEGIN

PROCESS (a)

BEGIN

tmp<='0';

FOR n IN 0 TO 7 LOOP --此循环语 句作为进程语句中的顺序语句使用 tmp <= tmp XOR a(n);

END LOOP;

y <= tmp

END..PROCESS;

END opt;

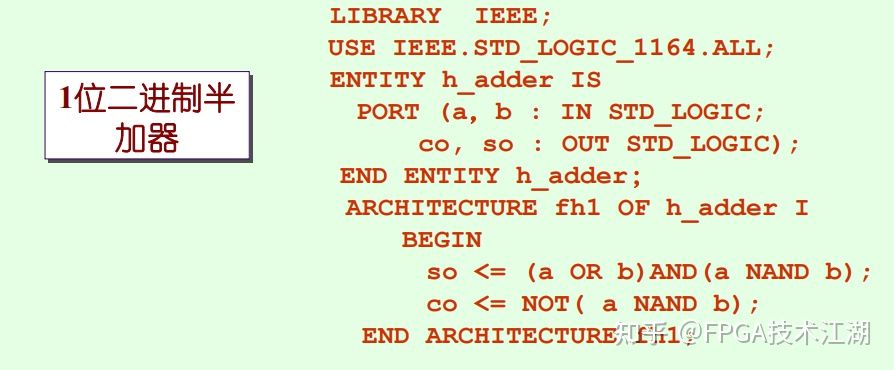

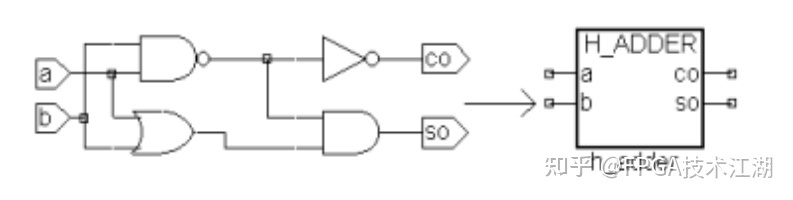

半加器:

1位半加器逻辑原理图:

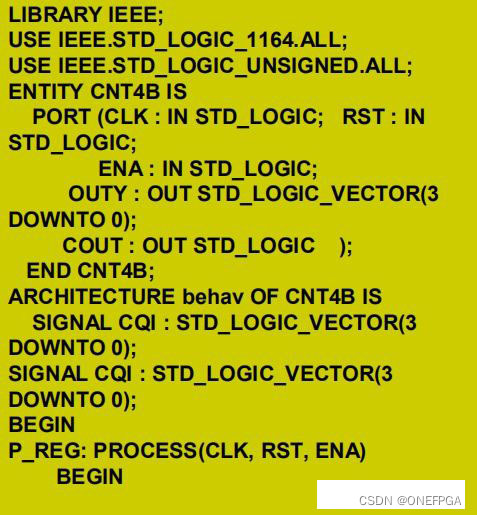

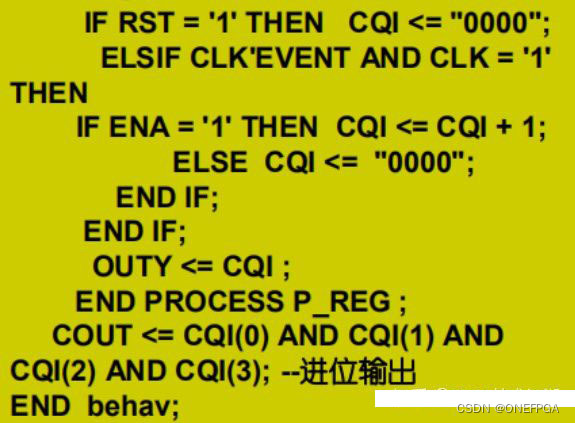

含异步清0和同步时钟使能的4位加法计数器:

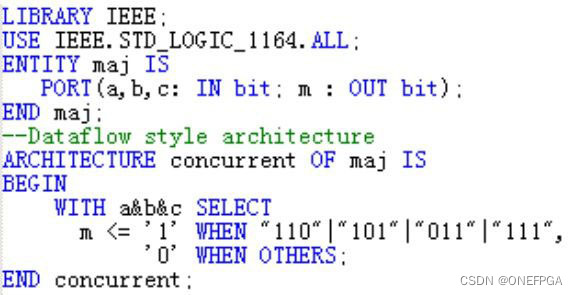

表决器:

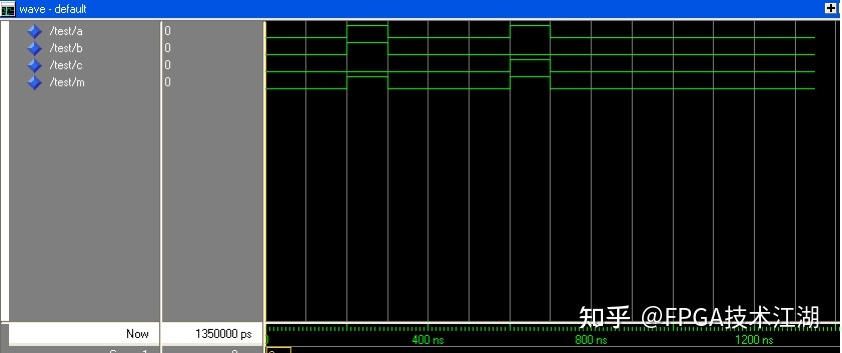

仿真波形图:

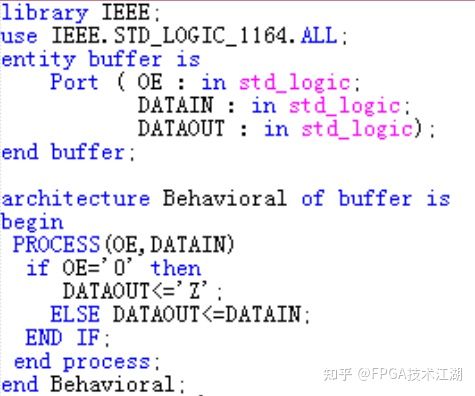

三态门:

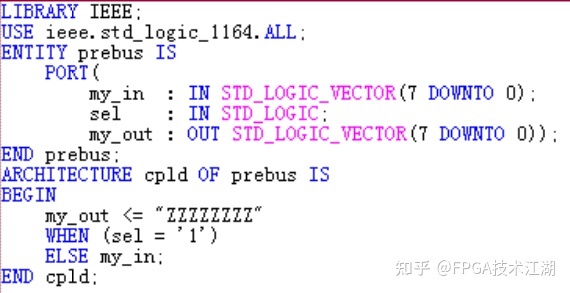

三态总线:

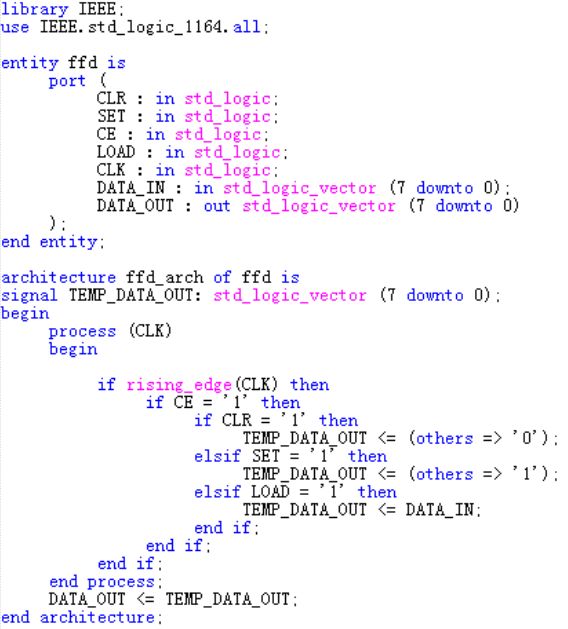

八位锁存器:

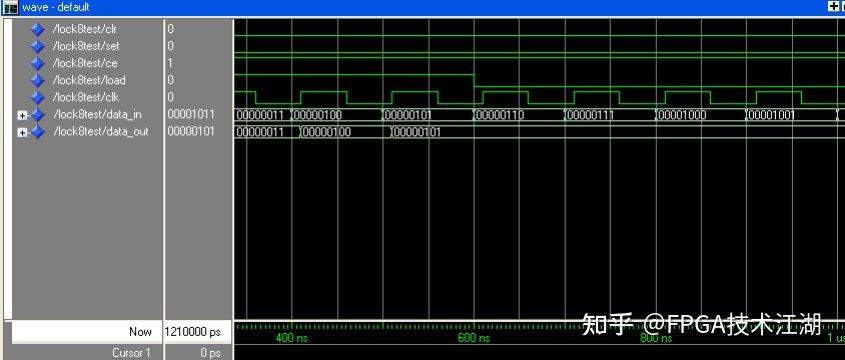

仿真波形图:

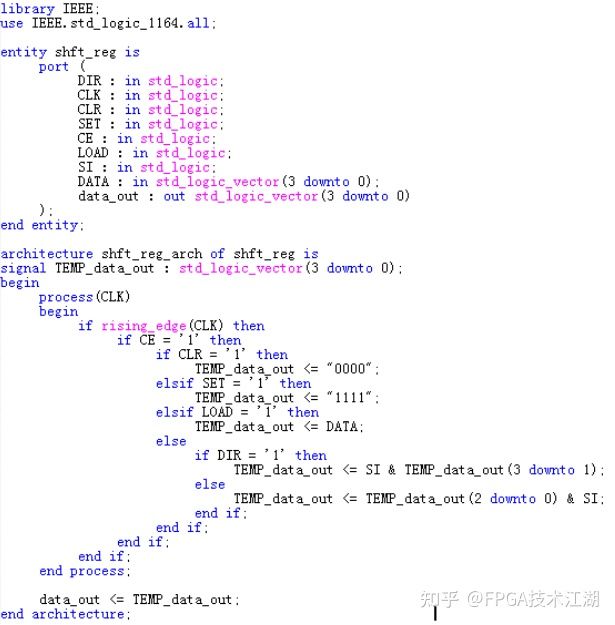

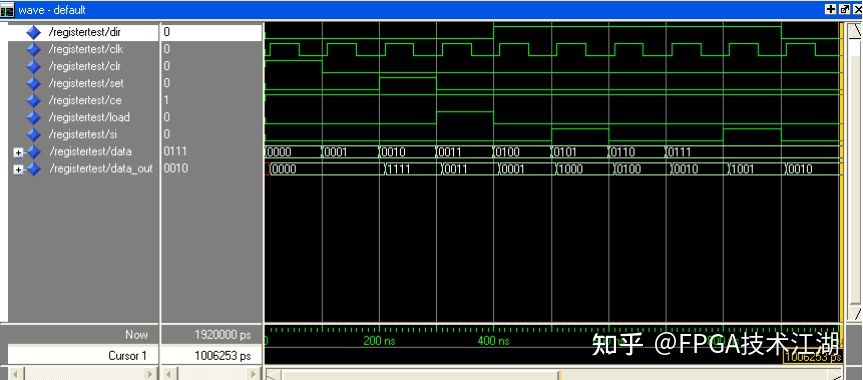

移位寄存器:

仿真波形图:

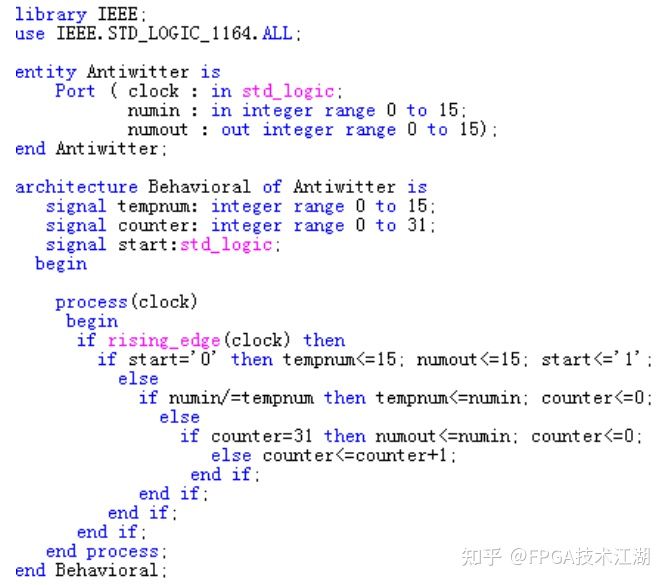

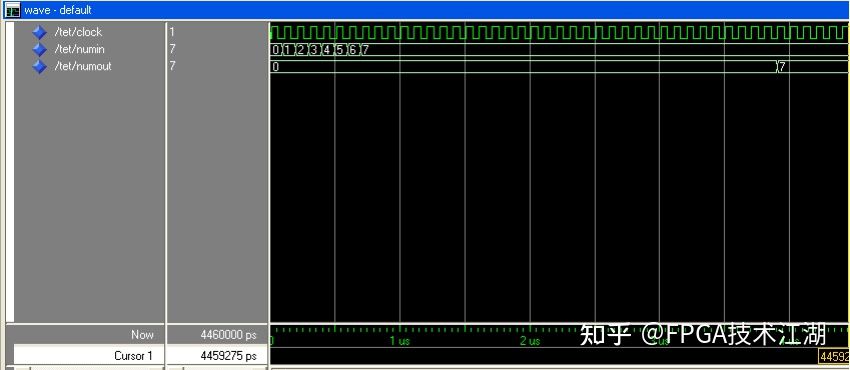

按键消抖电路:

仿真波形图:

Day 5 就到这里,Day 6 将带来 VHDL 仿真。

本文档详细介绍了VHDL编程在计数器、比较器、奇数倍分频、8位奇偶校验电路等基本电路的设计,以及半加器、加法计数器、表决器、三态门等电路的实现,并展示了相关电路的仿真波形。涵盖了从基础逻辑到复杂应用的VHDL编程实例。

本文档详细介绍了VHDL编程在计数器、比较器、奇数倍分频、8位奇偶校验电路等基本电路的设计,以及半加器、加法计数器、表决器、三态门等电路的实现,并展示了相关电路的仿真波形。涵盖了从基础逻辑到复杂应用的VHDL编程实例。

499

499

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?