一丶VGA显示原理

VGA(Video Grapghics Array),是一种使用模型信号进行视频传输的标准协议。

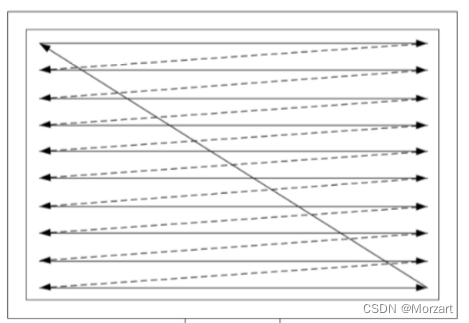

VGA 显示器显示图像,并不是直接让图像在显示器上显示出来,而是采用扫描的方式,VGA用的扫描的方式,一般是逐行扫描。

逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;

当扫描完所有的行,形成一帧后,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

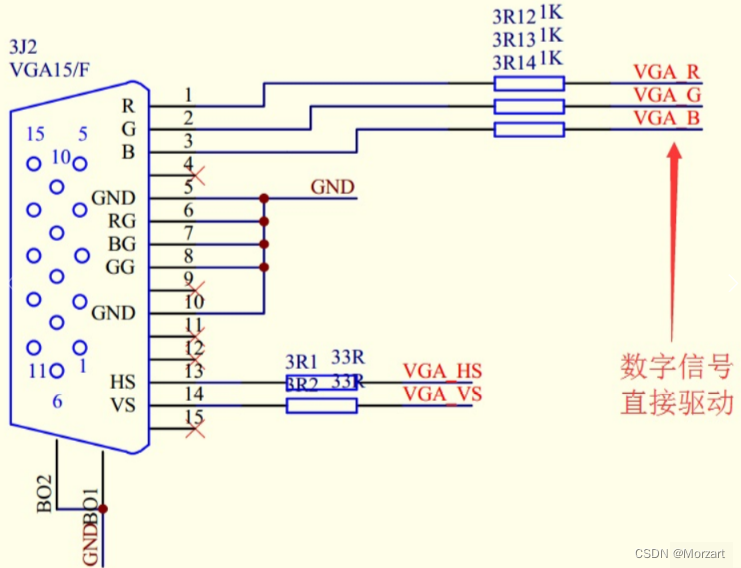

VGA端口的结构:

VGA端口是视频输出端口,端口一共包含15个管脚,如下图:

VGA原理:

在通常使用的连接方法里面,15个管脚里面的5个是最重要的,他们

包括3个基本红,绿,蓝三条基本色彩线和水平与垂直两条控制线

VGA接口标准:

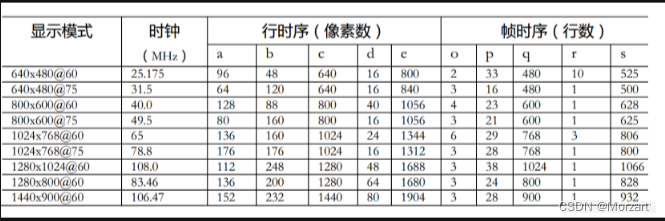

VGA工业标准所要求的频率:

• 时钟频率: 25.175MHz(像素输出的频率);

• 行频: 31469Hz;

• 场频: 59.94Hz。

显示器技术规格提供的行频一般在30kHz~45kHz(保守数据),场频一般在50Hz~75Hz(保守数据),针对以上保守数据,以30kHz的行频进行扫描时所需时钟频率为:30kHz×800(行周期)=24MHz,则场频为:30kHz÷525(场周期)=57.14Hz

在VGA视频传输标准中,视频图像被分解为红、绿、蓝三原色信号,经过数模转换之后,在行同步(HSYNC)和场同步(VSYNC)信号的同步下分别在三个独立通道传输。VGA在传输过程中的同步时序分为行时序和场时序

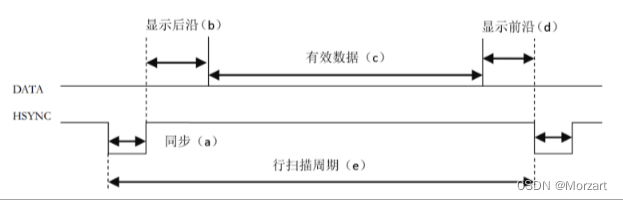

行同步时序:

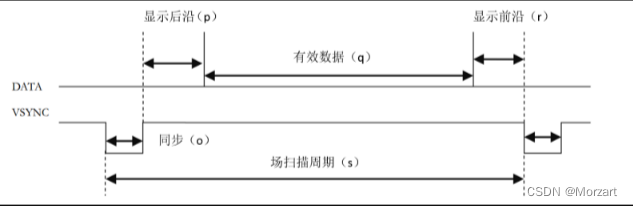

场同步时序:

从上面两幅图中我们可以看到VGA传输过程中的行同步时序和场同步时序非常类似,一行或一场(又称一帧)数据都分为四个部分:低电平同步脉冲、显示后沿、有效数据段以及显示前沿。

行同步信号HSYNC在一个行扫描周期中完成一行图像的显示,其中在a段维持一段时间的低电平用于数据同步,其余时间拉高;在有效数据期间(c段),红绿蓝三原色数据通道上输出一行图像信号其余时间数据无效。

与之类似,场同步信号在在一个场扫描周期中完成一帧图像的显示,不同的是行扫描周期的基本单位是像素点时钟,即完成一个像素点显示所需要的时间;而场扫描周期的基本单位是完成一行图像显示所需要的时间。

早期的VGA特指分辨率为640X480的显示模式,后来根据分辨率的不同,VGA又分为VGA(640x480)、SVGA(800x600)、XGA(1024x768)、SXGA(1280x1024)等。不同分辨率的VGA显示时序是类似的,仅存在参数上的差异,如图 18.1.5所示。

需要注意的是,即便分辨率相同,刷新速率(每秒钟图像更新次数)不一样时,对应的VGA像素时钟及时序参数也存在差异。例如,显示模式“640480@75”刷新速率为75hz,与相同分辨率下刷新速率为60hz的“640480@60”模式相比,像素时钟更快,其他时序参数也不尽相同。

二丶彩条显示

1.任务分析

本节实验任务是使用FPGA开发板上的VGA接口在显示器上显示彩条,要求分辨率为640*480,刷新速率为60hz。

2.代码设计

module VGA_colorbar_test(

OSC_50, //原CLK2_50时钟信号

VGA_CLK, //VGA自时钟

VGA_HS, //行同步信号

VGA_VS, //场同步信号

VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略

VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲

VGA_R, //VGA绿色

VGA_B, //VGA蓝色

VGA_G); //VGA绿色

input OSC_50; //外部时钟信号CLK2_50

output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC;

output [7:0] VGA_R,VGA_B,VGA_G;

parameter H_FRONT = 16; //行同步前沿信号周期长

parameter H_SYNC = 96; //行同步信号周期长

parameter H_BACK = 48; //行同步后沿信号周期长

parameter H_ACT = 640; //行显示周期长

parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长

parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时

parameter V_FRONT = 11; //场同步前沿信号周期长

parameter V_SYNC = 2; //场同步信号周期长

parameter V_BACK = 31; //场同步后沿信号周期长

parameter V_ACT = 480; //场显示周期长

parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长

parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时

reg [10:0] H_Cont; //行周期计数器

reg [10:0] V_Cont; //场周期计数器

wire [7:0] VGA_R; //VGA红色控制线

wire [7:0] VGA_G; //VGA绿色控制线

wire [7:0] VGA_B; //VGA蓝色控制线

reg VGA_HS;

reg VGA_VS;

reg [10:0] X; //当前行第几个像素点

reg [10:0] Y; //当前场第几行

reg CLK_25;

always@(posedge OSC_50)begin

CLK_25=~CLK_25; //时钟

end

assign VGA_SYNC = 1'b0; //同步信号低电平

assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平

assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反

assign CLK_to_DAC = CLK_25;

always@(posedge CLK_to_DAC)begin

if(H_Cont<H_TOTAL) //如果行计数器小于行总时长

H_Cont<=H_Cont+1'b1; //行计数器+1

else H_Cont<=0; //否则行计数器清零

if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1

VGA_HS<=1'b0; //行同步信号置0

if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1

VGA_HS<=1'b1; //行同步信号置1

if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长

X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点)

else X<=0; //否则X为0

end

always@(posedge VGA_HS)begin

if(V_Cont<V_TOTAL) //如果场计数器小于行总时长

V_Cont<=V_Cont+1'b1; //场计数器+1

else V_Cont<=0; //否则场计数器清零

if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1

VGA_VS<=1'b0; //场同步信号置0

if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1

VGA_VS<=1'b1; //场同步信号置1

if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长

Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行)

else Y<=0; //否则Y为0

end

reg valid_yr;

always@(posedge CLK_to_DAC)begin

if(V_Cont == 10'd32) //场计数器=32时

valid_yr<=1'b1; //行输入激活

else if(V_Cont==10'd512) //场计数器=512时

valid_yr<=1'b0; //行输入冻结

end

wire valid_y=valid_yr; //连线

reg valid_r;

always@(posedge CLK_to_DAC)begin

if((H_Cont == 10'd32)&&valid_y) //行计数器=32时

valid_r<=1'b1; //像素输入激活

else if((H_Cont==10'd512)&&valid_y) //行计数器=512时

valid_r<=1'b0; //像素输入冻结

end

wire valid = valid_r; //连线

assign x_dis=X; //连线X

assign y_dis=Y; //连线Y

// reg[7:0] char_bit;

// always@(posedge CLK_to_DAC)

// if(X==10'd144)char_bit<=9'd240; //当显示到144像素时准备开始输出图像数据

// else if(X>10'd144&&X<10'd384) //左边距屏幕144像素到416像素时 416=144+272(图像宽度)

// char_bit<=char_bit-1'b1; //倒着输出图像信息

reg[29:0] vga_rgb; //定义颜色缓存

always@(posedge CLK_to_DAC) begin

if(X>=0&&X<200)begin //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素

vga_rgb<=30'hffffffffff; //白色

end

else if(X>=200&&X<400)begin

vga_rgb<=30'hf00ff65f1f;

end

else if(X>=400&&X<600)begin

vga_rgb<=30'h9563486251;

end

else begin

vga_rgb<=30'h5864928654;

end

end

assign VGA_R=vga_rgb[23:16];

assign VGA_G=vga_rgb[15:8];

assign VGA_B=vga_rgb[7:0];

endmodule

三丶显示名字

1.任务分析

简单思考我们可以知道只需要将屏幕分成两种颜色,一种作为底色,一种作为名字的颜色来区分,即可显示名字。

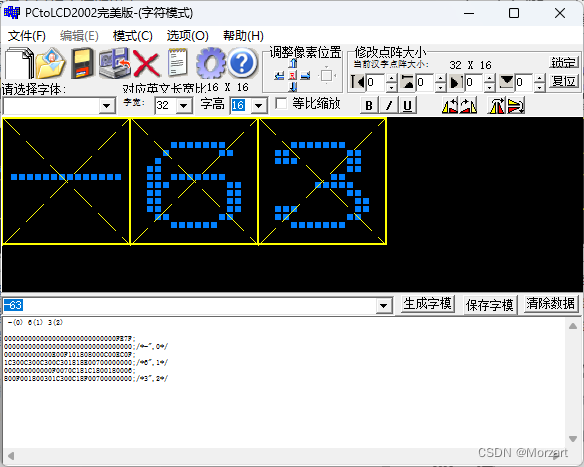

字符(包括汉字、字母和符号等)的本质都是点阵,在VGA屏幕上体现为字符显示区域内

像素点的集合。字符的大小决定了字符显示区域内像素点的数目,而字符的样式(字体、颜色

等)则决定了各像素点的颜色值。因此,在显示字符之前,我们需要先指定字符的大小、样式,

然后获取该字符的点阵,这个过程我们称之为“提取字模”,或简称“取模”。

我们一般使用0和1的组合来描述字符的点阵排列:点阵中每个像素点用一位(1 bit)数据来表示,其中用于表征字符的像素点用数字1来表示,其他的像素点作为背景用数字0来表示,如图 20.4.2所示。采用这种方式描述的字符是不含有颜色特征的,只能区分点阵中的字符和背景。

使用取字模工具将字模取出来

2.代码设计

`include "vga_param.v"

module data_gen_char(

input wire clk ,

input wire rst_n ,

input wire [10:0] h_addr , // 行地址--数据有效显示区域行地址

input wire [10:0] v_addr , // 场地址--数据有效显示区域场地址

output reg [23:0] data_display // 要显示的数据

);

parameter WIDTH_LEN = 64; // 字符总长度

parameter HEIGHT_LEN = 16; // 字符总高度

parameter WIDTH_REMAIN = (`H_Data_Time - WIDTH_LEN) / 2; //两边应该留的宽度

parameter HEIGHT_REMAIN = (`V_Data_Time - HEIGHT_LEN) / 2; //上下应该留的高度 232

// 每一行应该显示的数据(bit为1则显示)

reg [63:0] char_lines [15:0];

reg [4:0] now_line; // 当前为字符的第几行,0为不在

wire in_charline; // 在字符行

wire in_charcolumn; // 在字符列

reg [6:0] now_column; // 当前为字符的第几列

// 颜色

parameter

BLACK = 24'h000000,

RED = 24'hFF0000,

GREEN = 24'h00FF00,

BLUE = 24'h0000FF,

YELLOW = 24'hFFFF00,

CYANRAY = 24'h00FFFF,

PURPLE = 24'hFF00FF,

GRAY = 24'hC0C0C0,

WHITE = 24'hFFFFFF;

// 字符数据

always @(*) begin

char_lines[0 ] = 64'h0040_0000_0000_0200;

char_lines[1 ] = 64'h2040_00FC_FFFE_0200;

char_lines[2 ] = 64'h17FC_7C84_0100_0200;

char_lines[3 ] = 64'h1040_4484_0100_0200;

char_lines[4 ] = 64'h83F8_4484_0100_0200;

char_lines[5 ] = 64'h4040_44FC_7FFC_0200;

char_lines[6 ] = 64'h47FE_7C84_4104_03F8;

char_lines[7 ] = 64'h1000_4484_4104_0200;

char_lines[8 ] = 64'h13F8_4484_4944_0200;

char_lines[9 ] = 64'h2208_44FC_4524_0200;

char_lines[10] = 64'hE3F8_7C84_4104_0200;

char_lines[11] = 64'h2208_4484_4944_0200;

char_lines[12] = 64'h23F8_0104_4524_0200;

char_lines[13] = 64'h2208_0104_4104_0200;

char_lines[14] = 64'h2228_0214_4114_FEFE;

char_lines[15] = 64'h0210_0408_4008_0000;

end

// 字符第几行的判定

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

now_line <= 5'd0;

end

else if (in_charline && in_charcolumn) begin // 在字符范围内

now_line <= v_addr - HEIGHT_REMAIN + 1;

end

else begin

now_line <= 5'd0;

end

end

// 在字符行、列内

assign in_charcolumn = ((h_addr >= WIDTH_REMAIN) && (h_addr < WIDTH_REMAIN + WIDTH_LEN)) ;

assign in_charline = ((v_addr >= HEIGHT_REMAIN) && (v_addr < HEIGHT_REMAIN + HEIGHT_LEN)) ;

// 字符第几列的判定

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

now_column <= 7'd0;

end

else if (in_charline && in_charcolumn) begin // 在字符范围内

now_column <= h_addr - WIDTH_REMAIN;

end

else begin

now_column <= 7'd0;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

data_display <= WHITE;

end

else if (now_line != 5'd0 && now_column != 7'd0) begin // 在字符范围内

if (char_lines[now_line-1][WIDTH_LEN - now_column]) begin

// data_display <= {$random};

data_display <= CYANRAY;

end

else begin

data_display <= BLACK;

end

end

else begin

data_display <= BLACK;

end

end

endmodule

四丶VGA显示图像

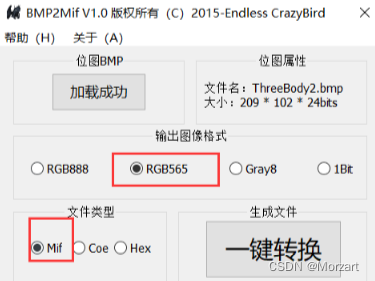

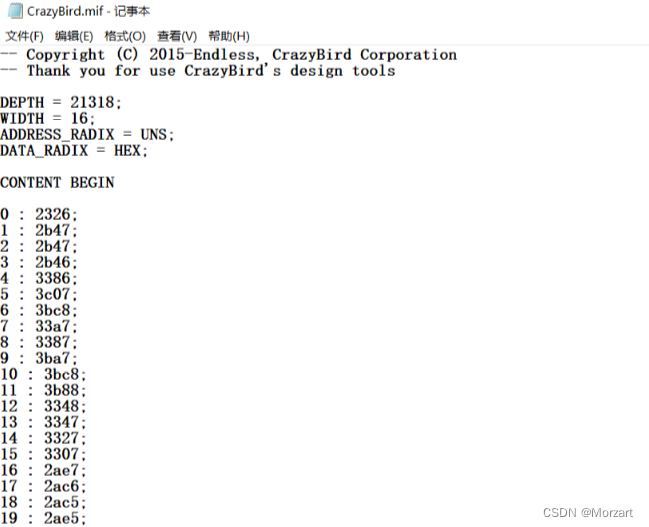

将bmp文件转换为mif文件:

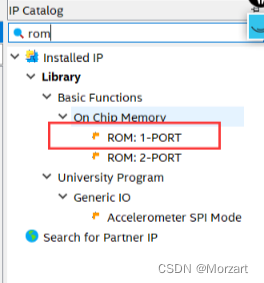

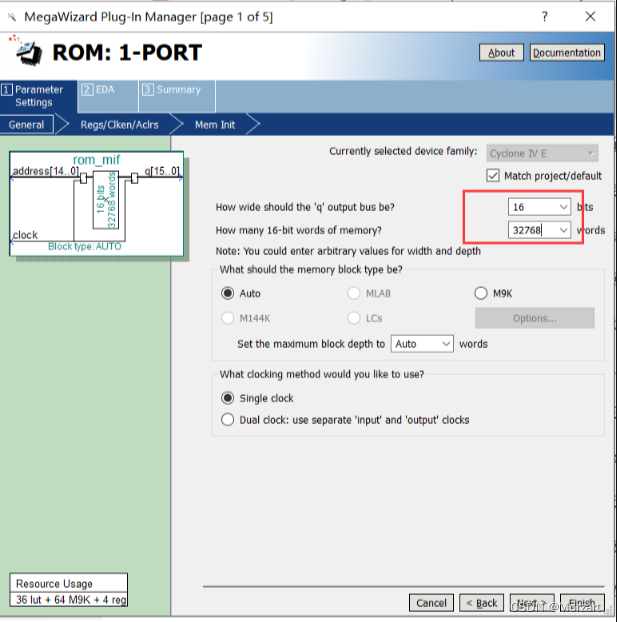

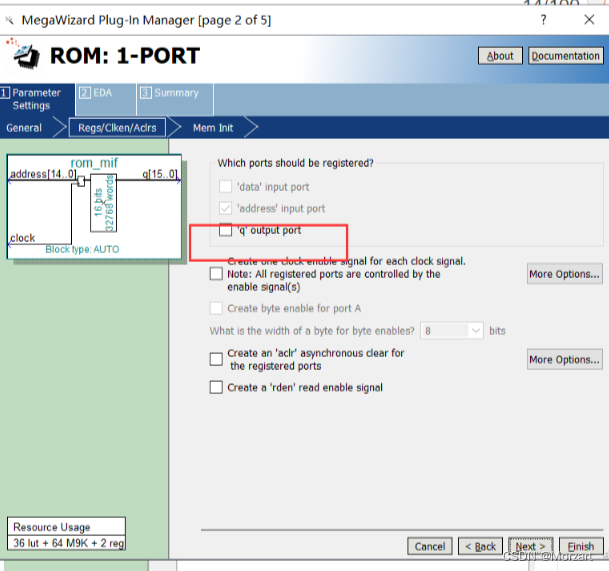

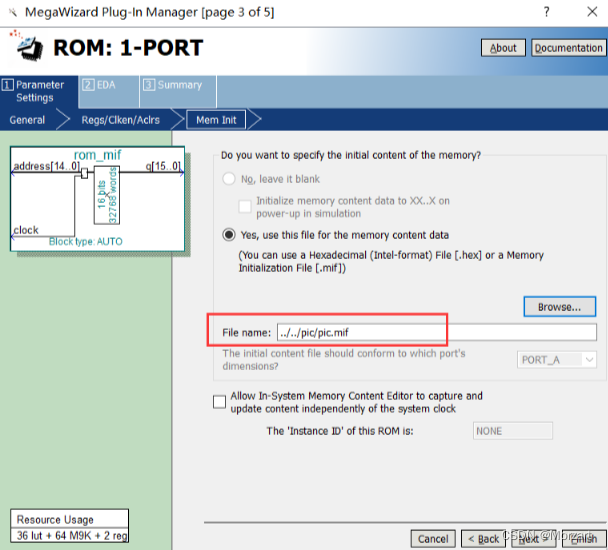

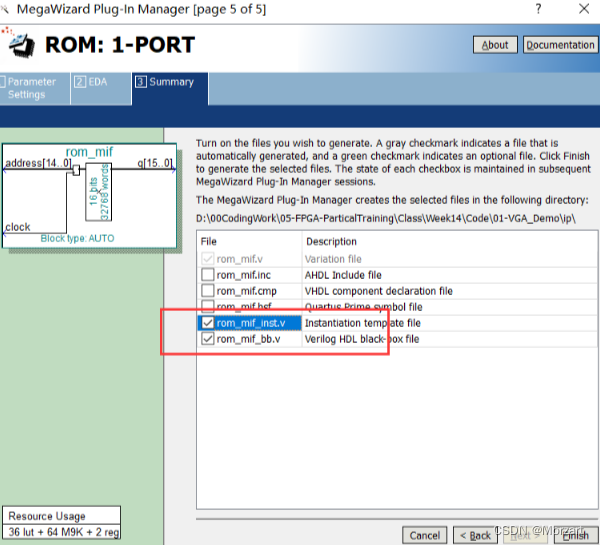

将生成的mif文件保存在ROM中。此时我们的ROM的位宽度为16位,深度的设置一定要大于图片的大小就行:

将生成的mif文件保存在ROM中。此时我们的ROM的位宽度为16位,深度的设置一定要大于图片的大小就行:

data_drive.v:

module data_drive (

input wire vga_clk,

input wire rst_n,

input wire [ 10:0 ] addr_h,

input wire [ 10:0 ] addr_v,

output reg [ 15:0 ] rgb_data

);

localparam black = 16'd0;

parameter height = 209; // 图片高度

parameter width = 102; // 图片宽度

reg [ 20:0 ] rom_address ; // ROM地址

wire [ 20:0 ] rom_data ; // 图片数据

wire flag_enable_out2 ; // 图片有效区域

wire flag_clear_rom_address ; // 地址清零

wire flag_begin_h ; // 图片显示行

wire flag_begin_v ; // 图片显示列

always @( posedge vga_clk or negedge rst_n) begin

if(!rst_n)begin

rgb_data = black;

end

else if ( flag_enable_out2 ) begin

rgb_data = rom_data;

end

else begin

rgb_data = black;

end

end

//ROM地址计数器

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

rom_address <= 0;

end

else if ( flag_clear_rom_address ) begin //计数满清零

rom_address <= 0;

end

else if ( flag_enable_out2 ) begin //在有效区域内+1

rom_address <= rom_address + 1;

end

else begin //无效区域保持

rom_address <= rom_address;

end

end

assign flag_clear_rom_address = rom_address == height * width - 1;

assign flag_begin_h = addr_h > ( ( 640 - width ) / 2 ) && addr_h < ( ( 640 - width ) / 2 ) + width + 1;

assign flag_begin_v = addr_v > ( ( 480 - height )/2 ) && addr_v <( ( 480 - height )/2 ) + height + 1;

assign flag_enable_out2 = flag_begin_h && flag_begin_v;

//实例化ROM

rom_mif rom_inst (

.address ( rom_address ),

.clock ( vga_clk ),

.q ( rom_data )

);

endmodule

data_drive.v:

module data_drive (

input wire vga_clk,

input wire rst_n,

input wire [ 10:0 ] addr_h,

input wire [ 10:0 ] addr_v,

output reg [ 15:0 ] rgb_data

);

localparam black = 16'd0;

parameter height = 209; // 图片高度

parameter width = 102; // 图片宽度

reg [ 20:0 ] rom_address ; // ROM地址

wire [ 20:0 ] rom_data ; // 图片数据

wire flag_enable_out2 ; // 图片有效区域

wire flag_clear_rom_address ; // 地址清零

wire flag_begin_h ; // 图片显示行

wire flag_begin_v ; // 图片显示列

always @( posedge vga_clk or negedge rst_n) begin

if(!rst_n)begin

rgb_data = black;

end

else if ( flag_enable_out2 ) begin

rgb_data = rom_data;

end

else begin

rgb_data = black;

end

end

//ROM地址计数器

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

rom_address <= 0;

end

else if ( flag_clear_rom_address ) begin //计数满清零

rom_address <= 0;

end

else if ( flag_enable_out2 ) begin //在有效区域内+1

rom_address <= rom_address + 1;

end

else begin //无效区域保持

rom_address <= rom_address;

end

end

assign flag_clear_rom_address = rom_address == height * width - 1;

assign flag_begin_h = addr_h > ( ( 640 - width ) / 2 ) && addr_h < ( ( 640 - width ) / 2 ) + width + 1;

assign flag_begin_v = addr_v > ( ( 480 - height )/2 ) && addr_v <( ( 480 - height )/2 ) + height + 1;

assign flag_enable_out2 = flag_begin_h && flag_begin_v;

//实例化ROM

rom_mif rom_inst (

.address ( rom_address ),

.clock ( vga_clk ),

.q ( rom_data )

);

endmodule

修改顶层文件:

/**

*

* 顶层文件

*/

module vga_top(

input wire clk,

input wire rst_n,

output wire hsync ,

output wire vsync ,

output wire [7:0] vga_r ,

output wire [7:0] vga_g ,

output wire [7:0] vga_b ,

// output wire vga_sync_n ,

output wire vga_black ,

output wire vga_clk

);

wire [23:0] data_display; // 要显示的数据

wire [10:0] h_addr ; // 行地址--数据有效显示区域行地

wire [10:0] v_addr ; // 场地址--数据有效显示区域场地

wire clk_25M;

clk_25M_get u_clk_25M_get(

.clk (clk ), //VGA时

.rst_n (rst_n ), //复位

.clk_25M (clk_25M)

);

// data_generate u_data_generate(

// /*input wire */ .clk (clk_25M ),

// /*input wire */ .rst_n (rst_n ),

// /*input wire [10:0] */ .h_addr (h_addr ), // 行地址--数据有效显示区域行地址

// /*input wire [10:0] */ .v_addr (v_addr ), // 场地址--数据有效显示区域场地址

// /*output wire [23:0] */ .data_display (data_display ) // 要显示的数据

// );

// 显示字符

// data_gen_char u_data_gen_char(

// /*input wire */ .clk (clk_25M ),

// /*input wire */ .rst_n (rst_n ),

// /*input wire [10:0] */ .h_addr (h_addr ), // 行地址--数据有效显示区域行地址

// /*input wire [10:0] */ .v_addr (v_addr ), // 场地址--数据有效显示区域场地址

// /*output wire [23:0] */ .data_display (data_display ) // 要显示的数据

// );

data_drive u_data_drive(

.vga_clk (clk_25M),

.rst_n (rst_n),

.addr_h (h_addr),

.addr_v (v_addr),

.rgb_data (data_display)

);

vga_ctrl u_vga_ctrl(

/*input wire */ .clk (clk_25M ),

/*input wire */ .rst_n (rst_n ),

/*input wire [23:0]*/ .data_display (data_display), // 要显示的数据

/*output wire [10:0]*/ .h_addr (h_addr ), // 行地址--数据有效显示区域行地址

/*output wire [10:0]*/ .v_addr (v_addr ), // 场地址--数据有效显示区域场地址

/*output reg */ .hsync (hsync ),

/*output reg */ .vsync (vsync ),

/*output reg [7:0] */ .vga_r (vga_r ), // R

/*output reg [7:0] */ .vga_g (vga_g ), // G

/*output reg [7:0] */ .vga_b (vga_b ), // B

// .vga_sync_n (vga_sync_n ),

.vga_black (vga_black ),

/*output wire */ .vga_clk (vga_clk ) // 时钟

);

endmodule

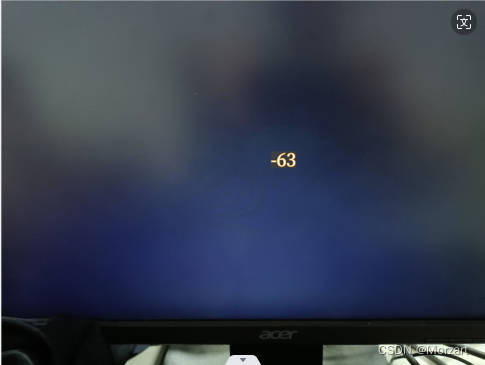

显示:

1723

1723

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?