module divider_odd

#(

parameter ODD = 3'd5

)

(

input wire sys_clk ,

input wire sys_rst_n ,

output wire clk_divider_odd

);

// cnt

reg [02:00] cnt ;

wire add_cnt ;

wire end_cnt ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt <= 0 ;

end else begin

if(add_cnt) begin

if(end_cnt) begin

cnt <= 0 ;

end else begin

cnt <= cnt + 3'b1 ;

end

end else begin

cnt <= cnt ;

end

end

end

assign add_cnt = 1'b1 ;

assign end_cnt = add_cnt && cnt == ( ODD - 1'b1 ) ;

// clk_p clk_n

reg clk_p ;

reg clk_n ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

clk_p <= 1'b0 ;

end else begin

if(cnt >= 3) begin

clk_p <= 1'b1 ;

end else begin

clk_p <= 1'b0 ;

end

end

end

always @(negedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

clk_n <= 1'b0 ;

end else begin

if(cnt >= 3) begin

clk_n <= 1'b1 ;

end else begin

clk_n <= 1'b0 ;

end

end

end

// clk_divider_odd

assign clk_divider_odd = clk_p || clk_n ;

endmodule

`timescale 1ns/1ns

module test();

reg sys_clk ;

reg sys_rst_n ;

wire clk_divider_odd ;

divider_odd

#(

.ODD (5)

)

divider_odd_insert

(

.sys_clk ( sys_clk ),

.sys_rst_n ( sys_rst_n ),

.clk_divider_odd ( clk_divider_odd )

);

parameter CYCLE = 20 ;

initial begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( 210 ) ;

sys_rst_n <= 1'b0 ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( CYCLE * 1000 ) ;

$stop ;

end

always #( CYCLE / 2 ) sys_clk = ~sys_clk ;

endmodule

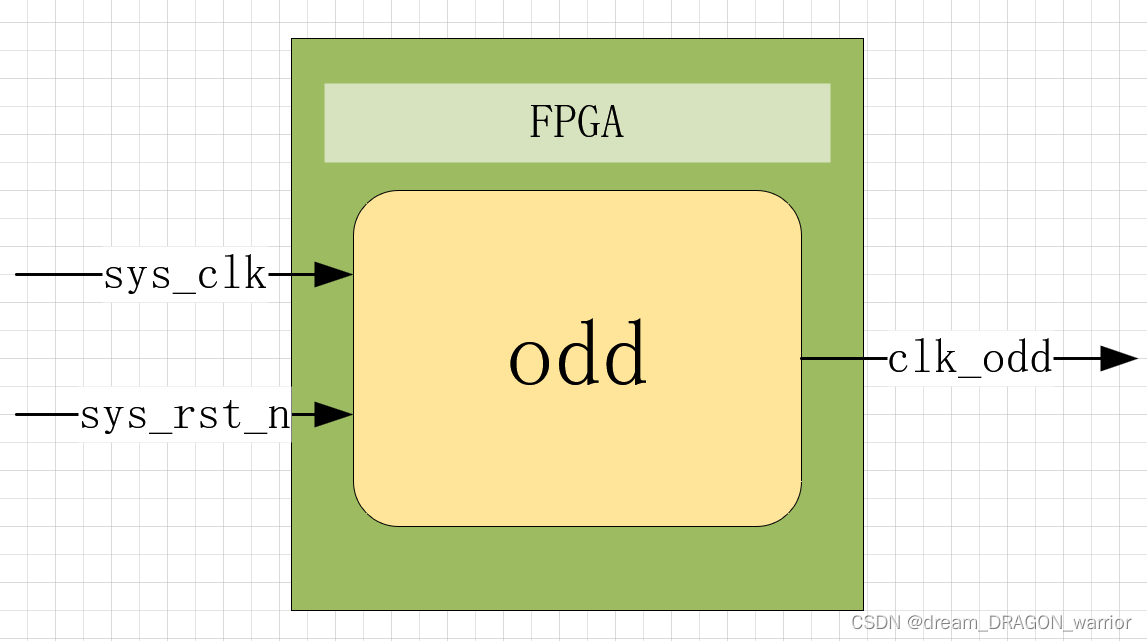

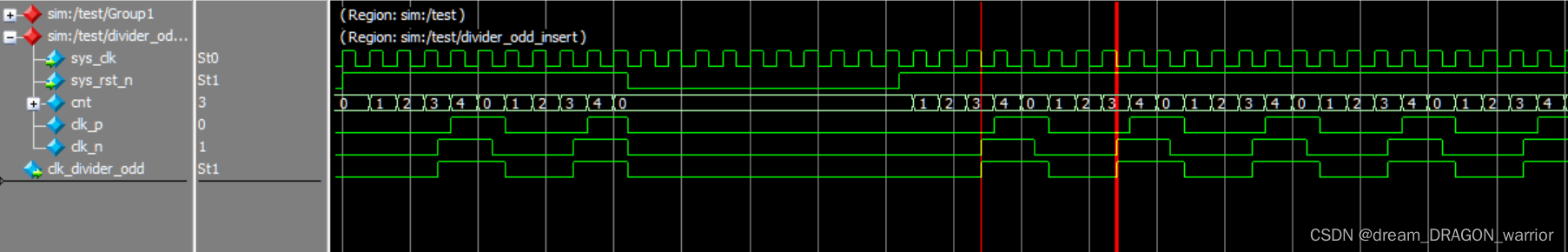

本文描述了一个Verilog设计,实现了一个可配置的分频器模块(divider_odd),使用计数器和时钟信号调整输出频率,配合测试模块进行时序分析。

本文描述了一个Verilog设计,实现了一个可配置的分频器模块(divider_odd),使用计数器和时钟信号调整输出频率,配合测试模块进行时序分析。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?