参考文档:野火F7 https://doc.embedfire.com/mcu/stm32/f767_h743_h750/hal_general/zh/latest/index.htmlc

参考文档:STM32F76xxx and STM32F77xxx_Reference manual (网上可以搜 F1 F4 F7 都可以)

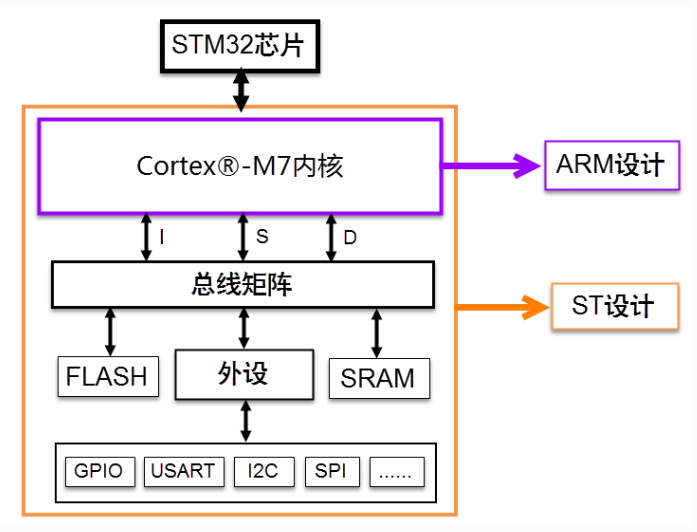

1.芯片结构

我们看到的STM32芯片已经是已经封装好的成品,主要由内核和片上外设组成。若与电脑类比,内核与外设就如同电脑上的CPU与主板、内存、显卡、硬盘的关系。

以 STM32F767为例, 他采用的是Cortex-M7内核,内核即CPU,由ARM公司设计ARM公司并不生产芯片,而是出售其芯片技术授权。

芯片生产厂商(SOC) 如ST、TI、NXP等,负责在内核之外设计部件并生产整个芯片,这些内核之外的部件被称为核外外设或片上外设。 如GPIO、USART(串口)、I2C、SPI等都叫做片上外设。

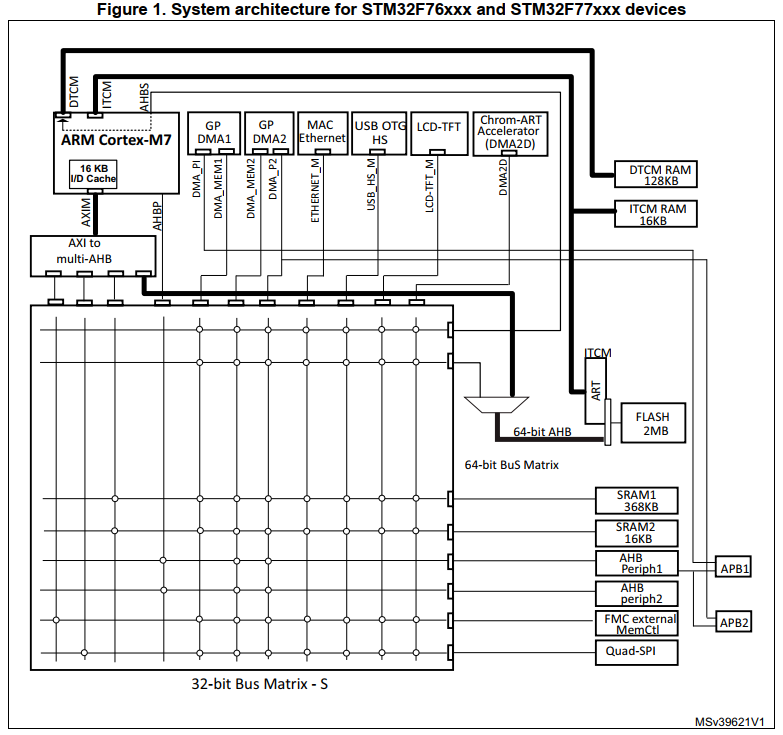

芯片主系统架构基于两个子系统,一个是AXI转多层AHB桥,多层AHB总线矩阵(参考下图)。

1.AXI 转多层 AHB 桥

AXI转多层AHB桥,从AXI4协议转成AHB-Lite协议, 其中包含3个AXI转32-bit AHB桥通过32-bit的AHB总线矩阵连接到外部存储器FMC接口、 外部存储器Quad SPI接口、内部SRAM(SRAM1 and SRAM2)。 还包含一个AXI转64-bit AHB桥通过64-bit总线矩阵连接到内部FLASH。

主设备有:

- ARM Cortex-M7(带 I-Cache、D-Cache、TCM)

128 KB ITCM RAM ← 指令紧耦合存储器,CPU取指零等待

16 KB DTCM RAM ← 数据紧耦合存储器,CPU数据零等待

这两块 TCM 不走 AXI,也不走总线矩阵,CPU 像访问 cache 一样直接访问 -

DMA1 / DMA2(通用 DMA)

-

DMA2D(Chrom-ART 图形加速器,专做 2D 搬图)

-

Ethernet MAC(带 DMA 主端口)

-

USB OTG HS(内置 DMA 主端口)

-

LCD-TFT 控制器(带 DMA 主端口)

以上所有主端口都先汇到 64-bit AXI 总线矩阵。

2.多层AHB总线矩阵

多层AHB总线矩阵,其中32-bit多层AHB总线矩阵互联11个主设备和8个从设备,64-bit多层AHB总线矩阵则是CPU通过AXI转AHB桥通过这个64-bit多层AHB总线矩阵连接到内部Flash。 DMA主设备通过32-bit AHB总线矩阵通过这个64-bit多层AHB总线矩阵连接到内部Flash。 主控总线通过一个总线矩阵来连接被控总线,总线矩阵用于主控总线之间的访问仲裁管理,仲裁采用循环调度算法。 总线之间交叉的时候如果有个圆圈则表示可以通信,没有圆圈则表示不可以通信。

1.AXI-to-64-bit-AHB Bridge

- 64-bit AHB Bus Matrix

- 2 MB 内部 Flash(64-bit 宽接口,CPU 取指主通道)

Flash 接口是 64 位,单周期可取 8 字节指令,最大化 M7 性能。

2.AXI-to-32-bit-AHB Bridge

- 32-bit AHB Bus Matrix

- SRAM1 368 KB

SRAM2 16 KB

FMC(外部 NOR/SRAM/SDRAM 并行存储器控制器)

Quad-SPI(外部串行 Flash 控制器)

图形 DMA、LCD、USB、以太网都要大量搬数据,它们走 AXI转32-bit AHB 桥,再分到 SRAM/外存,避免与 CPU 取指通道抢带宽。

3.AHB → APB 桥(把高速 AHB 再降速到 APB)

32-bit AHB Matrix 还分出两条桥:

-

AHB → APB1(低速外设,定时器、USART、I²C、SPI 等)

-

AHB → APB2(高速外设,ADC、TIM1/8、SPI1、EXTI 等)

4.带宽和性能

1.双通道并行

-

CPU 取指:ITCM + 64-bit Flash,几乎零等待。

-

数据搬运:DMA 们走 AXI→32-bit AHB→SRAM/外存,不占用 CPU 通道。

2.总线宽度匹配

-

Flash 64 位 → 取指带宽 8 B/周期。

-

SRAM/外设 32 位 → 满足 DMA 数据流即可,节省布线面积。

3.多层矩阵避免阻塞

AXI 矩阵、64-bit AHB 矩阵、32-bit AHB 矩阵三级并行,不同主设备访问不同从设备时可真正同时完成。

3.小结:

Cortex-M7 内核通过 64-bit AXI 总线矩阵 分成两路:

- 一路经 64-bit AHB 专供内部 Flash 指令/数据高速通道;

- 另一路经 32-bit AHB 矩阵把 SRAM、外部 FMC、Quad-SPI 和全部 APB 外设挂在一起,让 DMA、图形加速(DMA2D)、USB、以太网、LCD 等主设备可以并行搬数据,从而既保证 CPU 跑满 216 MHz,又保证外设数据流不冲突。

7256

7256

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?