讲解视频:

https://www.bilibili.com/video/BV1W1hrzQEZW/?spm_id_from=333.1387.homepage.video_card.click

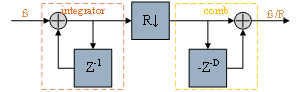

cic抽取滤波器是一种兼具低通抗混叠与降采样作用的高速率滤波器,内部不需要系数计算也不涉及乘法运算,仅有梳状器comb和积分器integrator组成,一阶cic抽取滤波器结构如下

R为抽取率,M为延迟因子,fs为输入采样率,fs/R为输出采样率,当阶数为N时,只需要将N个积分器串联在一起,N个梳状器串联在一起即可

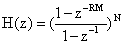

cic抽取滤波器的z域表达式如下

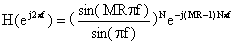

令z=可得频域表达式

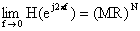

将f=0可得直流增益

因此相比于IIR、FIR数字滤波器,cic的直流增益随着M、R、N的增加指数级上升,因此在数字电路设计位宽时cic输出位宽可根据直流增益的位宽与输入位宽来确定。

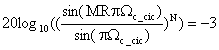

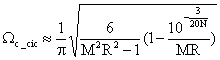

cic抽取滤波器截止频率无法精确计算,但可以获取近似值,假设对其进行了直流增益补偿,即整体输出除以直流增益,幅频特性-3db为截止频率点

可见归一化截止频率始终小于归一化那奎斯特频率0.5,同时随着MRN增加而减少,因此可知cic抽取滤波器具有良好的抗混叠能力

因此同时具备抗混叠与降采样功能的cic抽取滤波器广泛应用于数字抗混叠滤波器的设计

在matlab中使用fdatool设计如下

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3908

3908

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?