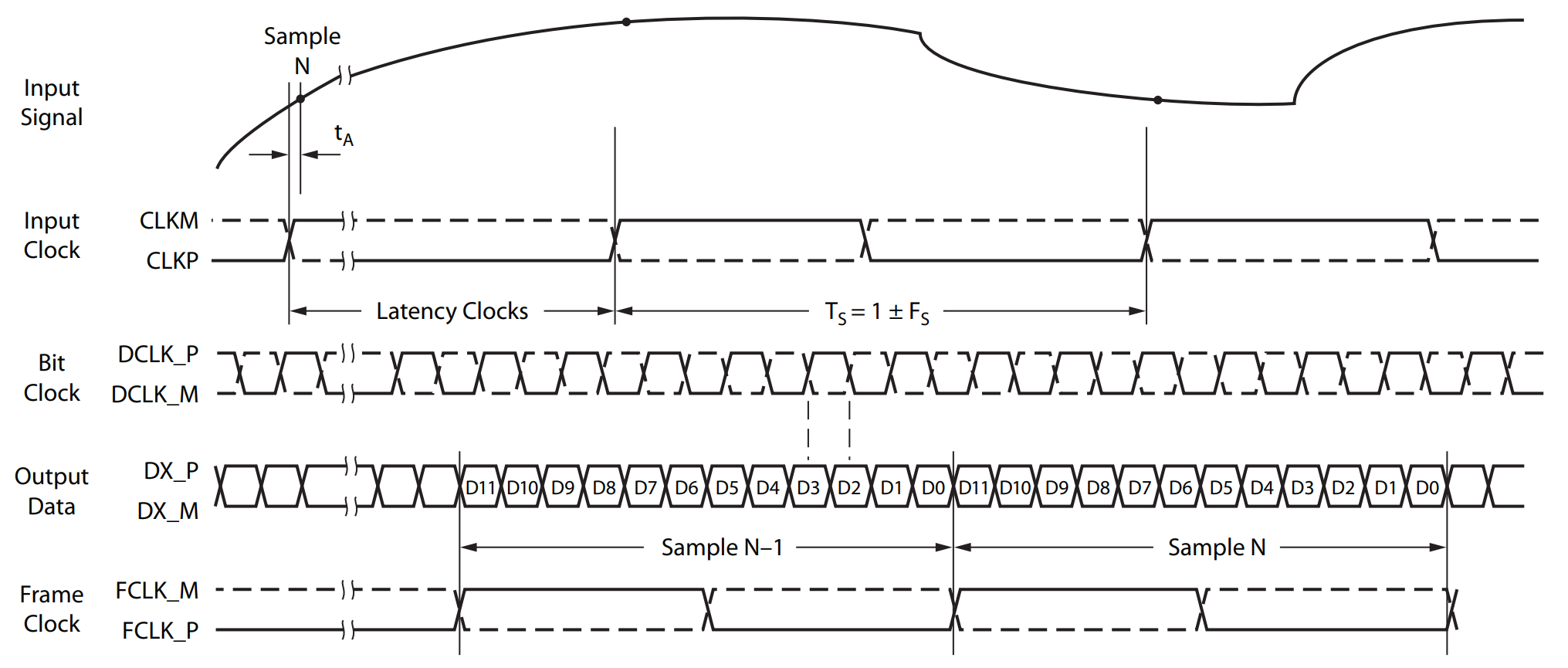

常见的是VESA和JEIDA标准的LVDS,除此之外还1:4、1:8、1:12等等,特别是高速场景的ADC采集、视频传输等等。如下图ADC采集时序图:

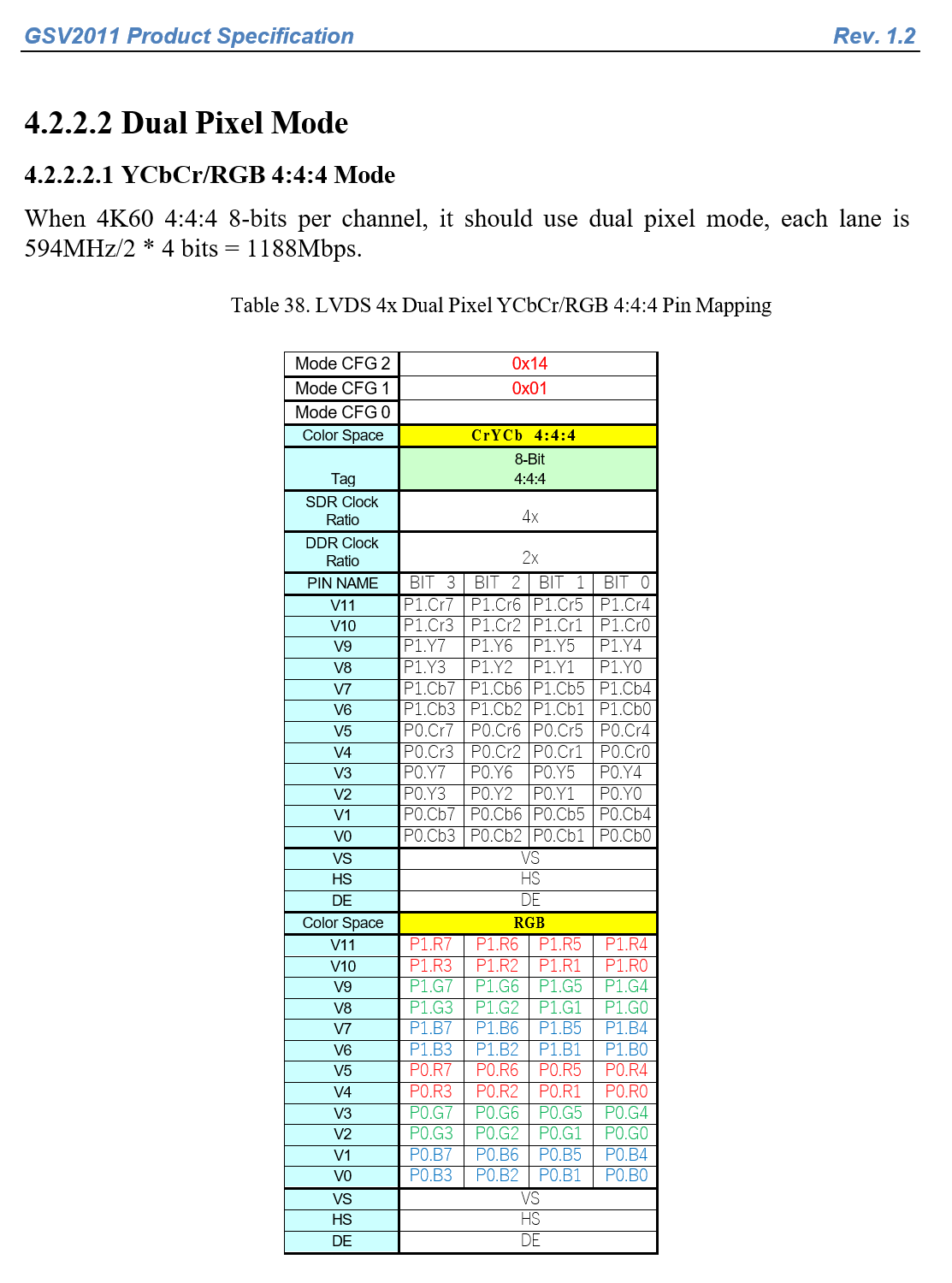

一、本次主要讲是用FPGA调试GSV2011遇到的问题,刚拿这个芯片资料看到12对LVDS脑子嗡嗡的,之前没有这样用过,一时没有参考。不经意看到xapp524的ADC采集,受到启发。

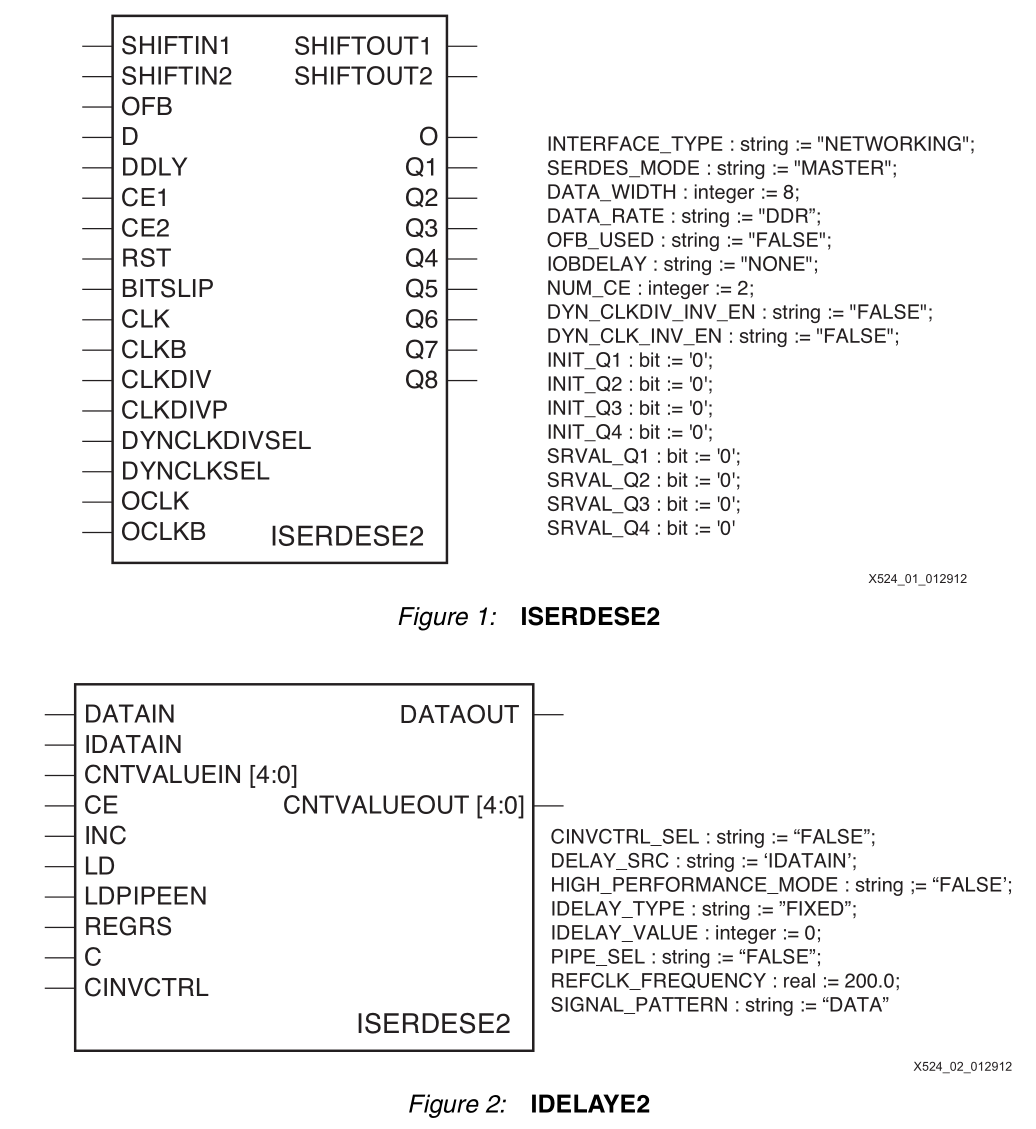

二、根据xapp524-serial-lvds-adc-interface.pdf使用ISERDESE2+IDELAYE2来解嵌GSV2011的12路LVDS。

三、实际测试发现拔插信号很容易出现数据错位,导致图像异色/花屏。一时没有找到数据对齐的标志信号,经过不懈努力终于有一个可以用的程序。若有更好的解决办法,欢迎大神赐教!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?