集成电路封装测试是确保芯片性能与可靠性的核心环节,主要包括晶圆级测试(CP测试)和封装后测试(FT测试)两大阶段,流程如下:

一、晶圆级测试(CP测试)

1.测试目的:在晶圆切割前筛选出功能缺陷或性能不达标的晶粒(Die),避免后续封装环节的资源浪费,显著降低制造成本。

2.核心设备与操作

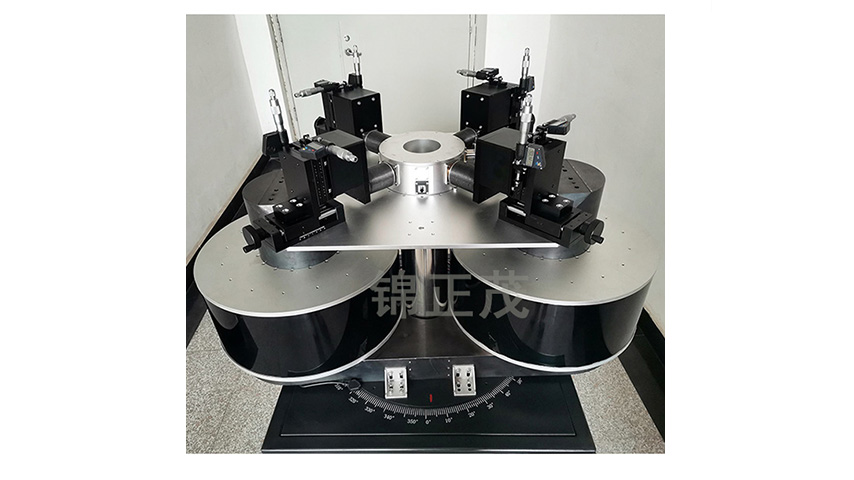

- 探针台(Prober):通过高精度移动平台将探针与晶粒的Pad精准接触,实现电气连接。

- ATE测试机:提供测试电源、信号输入及功能向量,接收晶粒反馈信号以判定其良率(例如检测漏电流、阈值电压等参数)。

- 探针卡(Probe Card):根据芯片Pad布局定制,确保ATE信号与晶粒引脚导通。

3.输出结果

生成晶圆缺陷图(Wafer Map),标记不良晶粒(如打墨点),供后续封装环节剔除。

二、封装流程关键步骤

1.前段处理

- 晶圆减薄:通过背面研磨将晶圆厚度调整至封装要求(如100μm以下),并粘贴保护胶带防止电路损伤。

- 晶圆切割:用金刚石刀片或激光切割将晶圆分割为独立晶粒,清洗后去除残留碎屑。

2.核心封装工艺

- 芯片贴装(Die Attach):将晶粒固定在基板或框架上,通过银浆或焊料实现机械固定与导热。

- 引线键合(Wire Bonding):用金线/铜线连接晶粒Pad与封装基板引脚,确保信号导通。

- 塑封成型(Molding):使用环氧树脂(EMC)包裹芯片,保护内部结构免受物理和化学损害。

3.后段处理

- 激光打标:在封装表面刻印型号、批次等信息。

- 电镀与切割:对引脚进行电镀处理(如镀锡/镍),增强可焊性,并切除多余塑封材料。

三、封装后测试(FT测试)

1.功能验证

- 检测封装后芯片的电气性能(如工作频率、功耗、I/O信号完整性),确保符合设计规格。

- 通过边界扫描(Boundary Scan)等技术验证内部逻辑功能。

2.可靠性测试

- 环境应力测试:包括高温/低温循环(-55℃至+150℃)、高湿高压(如85℃/85%RH)等,验证芯片寿命与稳定性。

- 机械强度测试:如振动、冲击测试,评估封装结构可靠性。

3.量产终测

自动化测试设备(ATE)批量执行测试程序,生成测试报告(含良率、失效模式等数据)。

四、技术演进与效率优化

- 自动化升级:通过视觉定位系统与机械臂实现探针快速校准,提升CP测试效率(如每小时测试晶圆数量提升30%)。

- 多芯片并行测试:支持存储器等芯片的多点同步测试,降低单颗测试成本。

集成电路封装测试通过晶圆筛选-封装保护-功能验证的闭环流程,确保芯片性能达标与长期可靠性。晶圆级测试(CP)与封装后测试(FT)的分段实施,显著降低制造成本(不良品处理成本相差10倍以上)。随着探针台精度提升(达±0.1μm)与测试设备智能化,该流程正加速向高集成度、高可靠性方向演进。

5086

5086

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?