基础工程创建

基础工程创建可以参考以下链接:

正点原子领航者ZYNQ7020开发板 GMAC1 EMIO调试记录

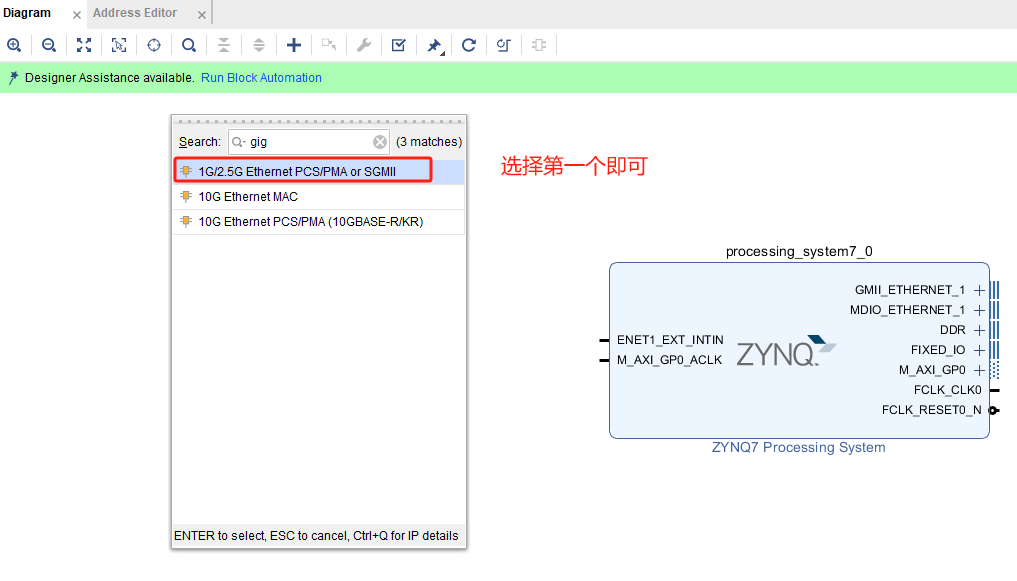

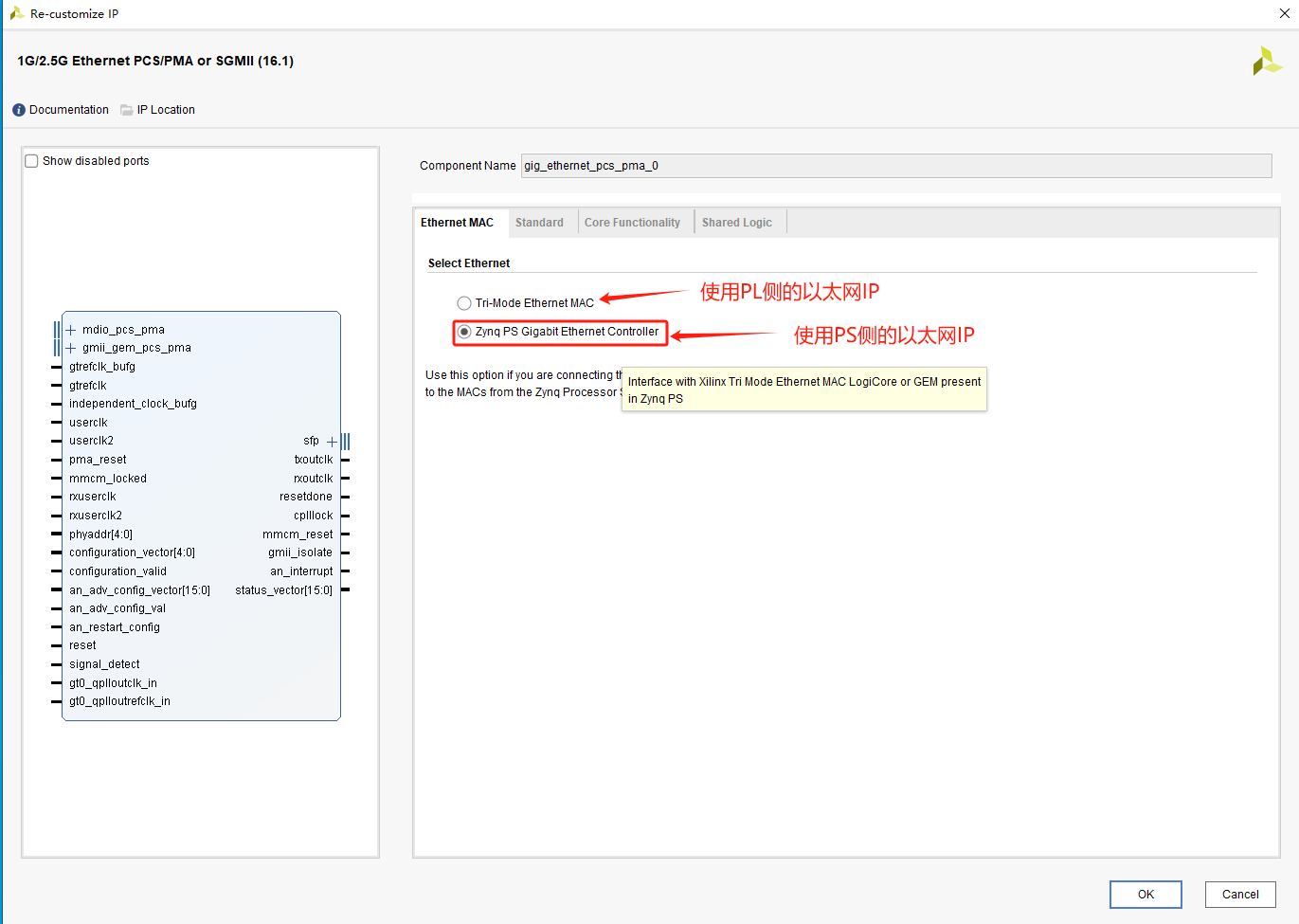

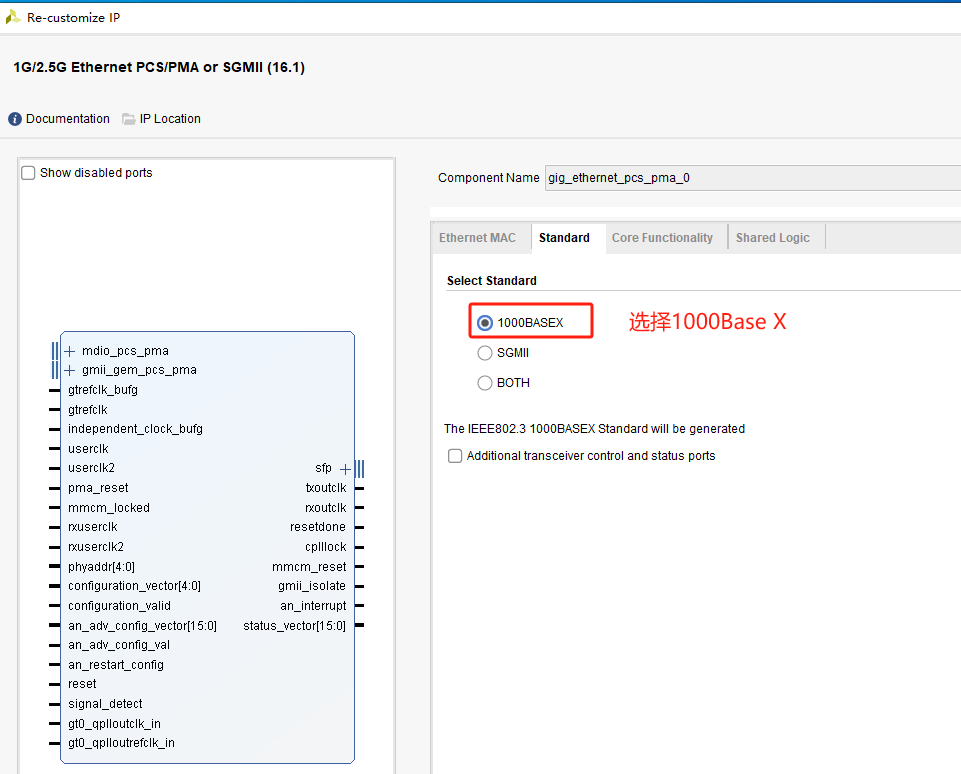

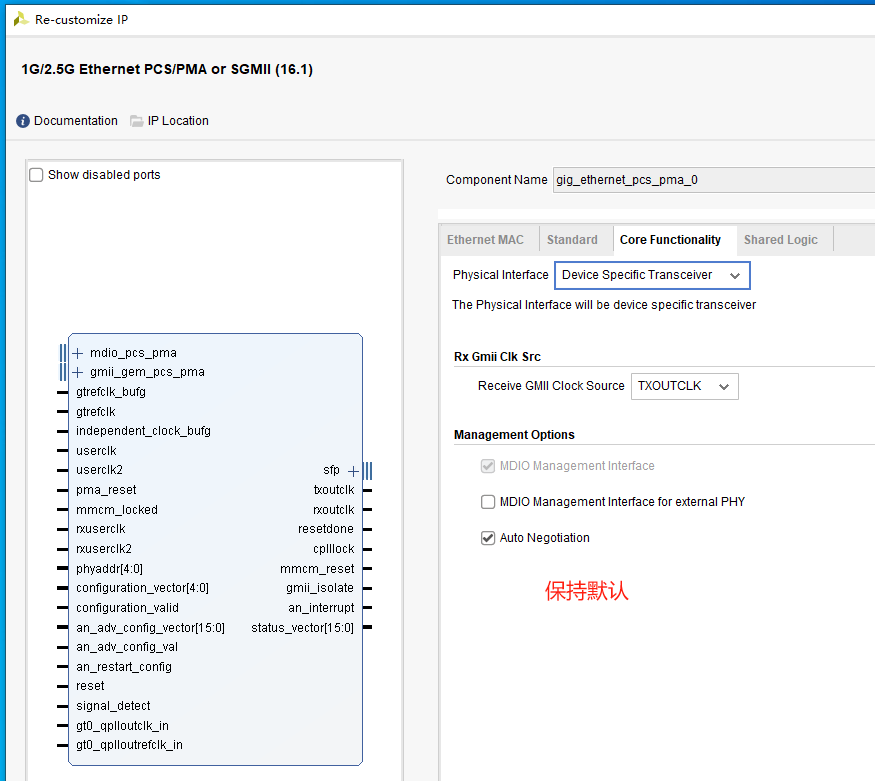

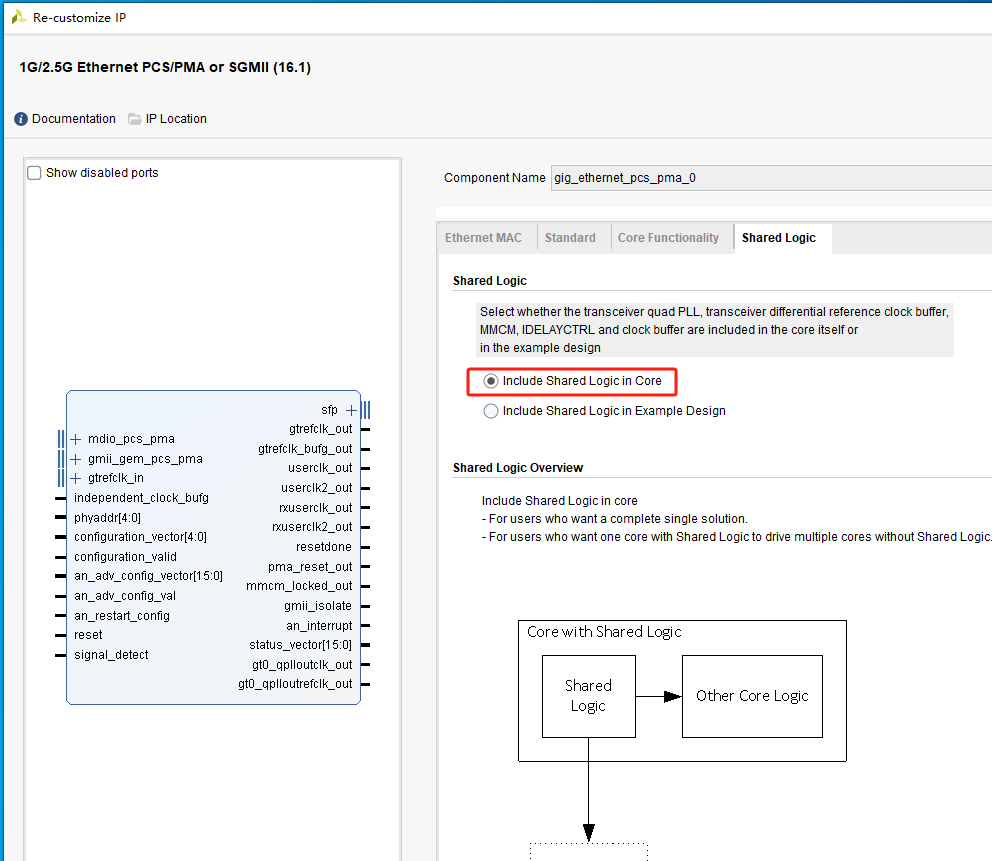

SFP IP添加与设置

双击IP进行设置,选择使用PS侧的以太网IP

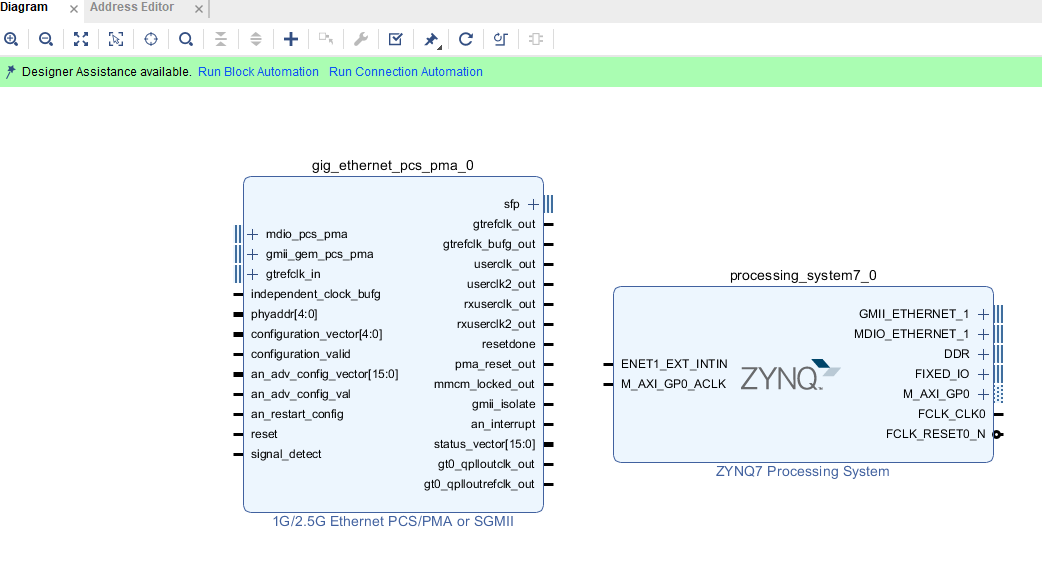

以上设置完成后点击OK,如下图

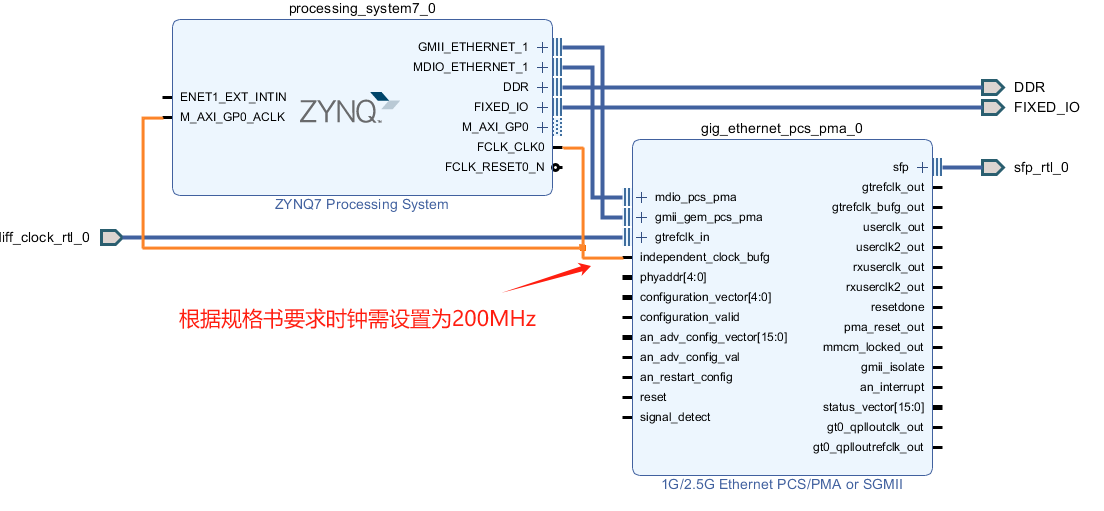

基础连线与配置

- 手动基础连线

- 手动配置项

| 信号名称 | 配置 |

|---|---|

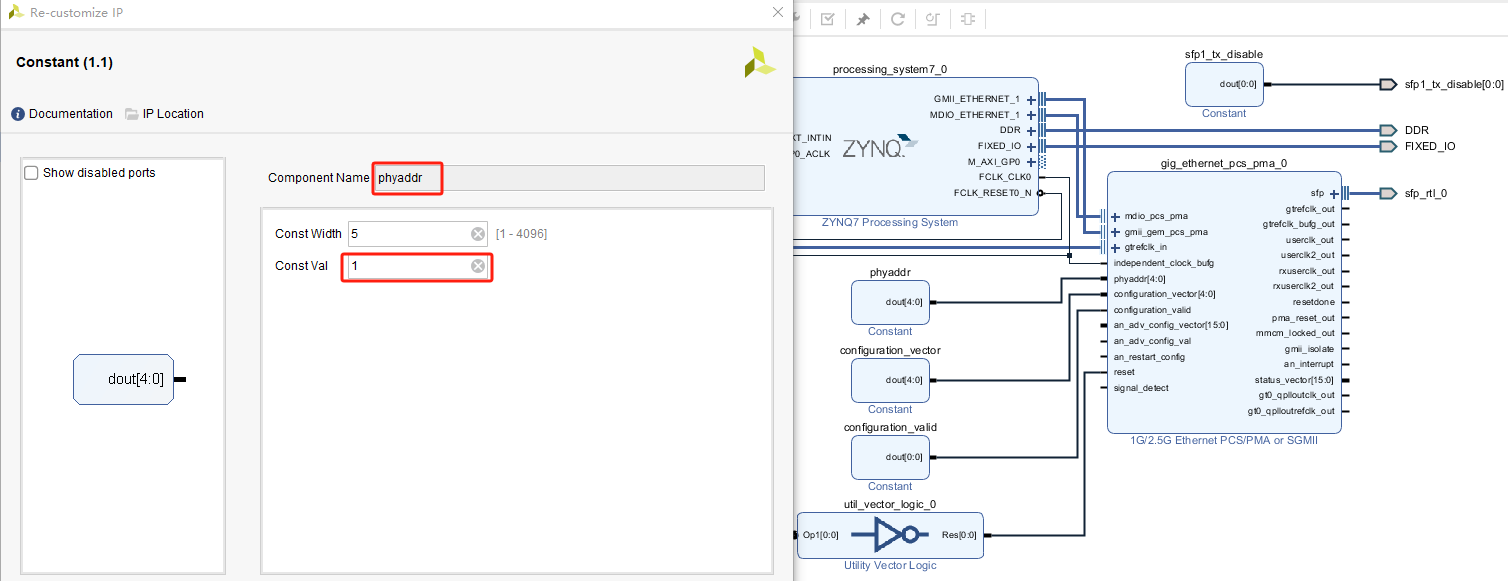

| phyaddr[4:0] | phy地址范围0~31 |

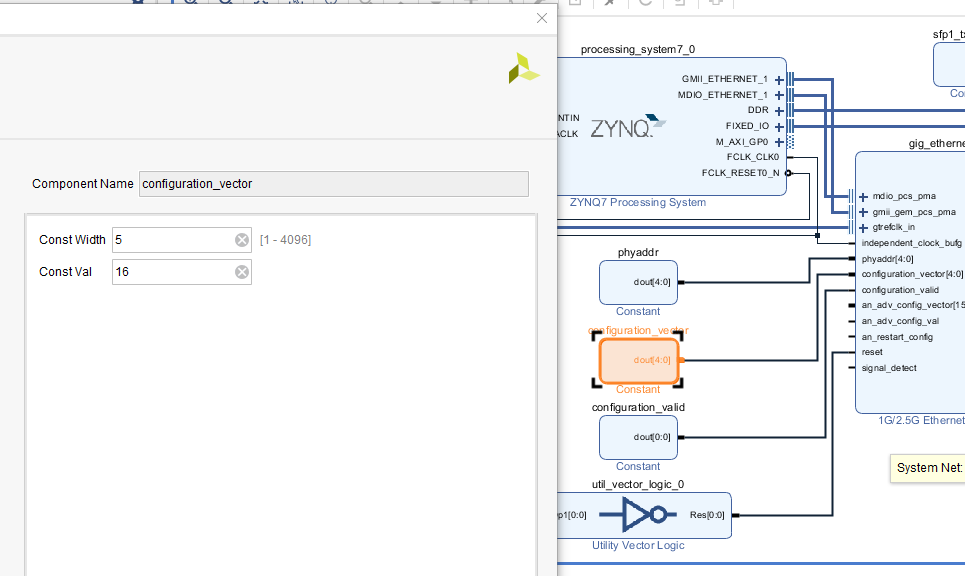

| configuration_vector[4:0] | 针对PHY寄存器0配置的附加配置接口 |

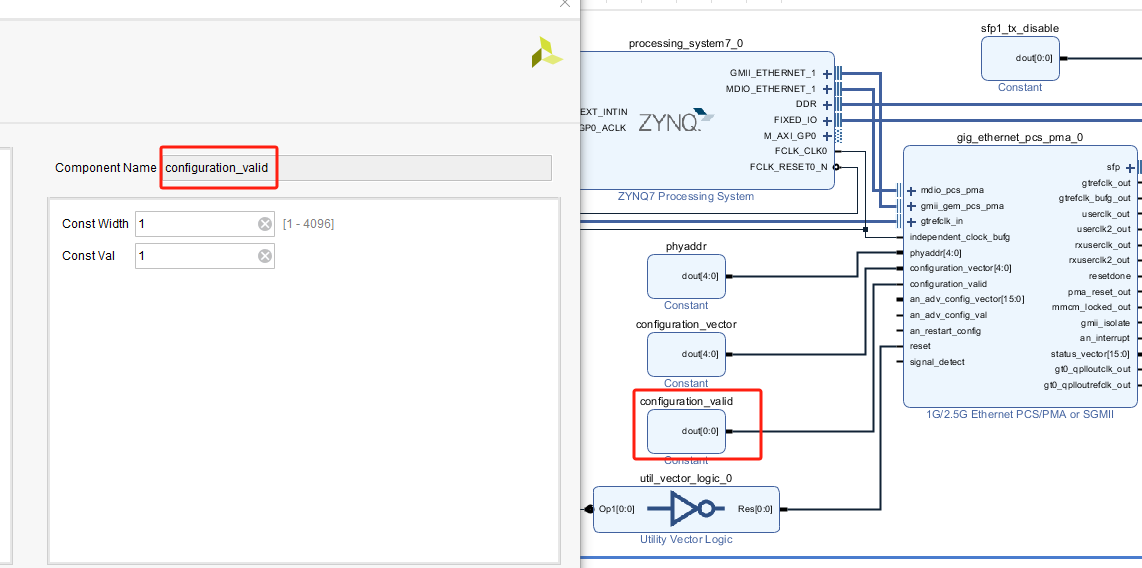

| configuration_valid | 该信号仅在MDIO接口存在时有效。此信号的上升沿是覆盖通过MDIO接口写入的寄存器0内容的使能信号。若要通过配置向量(configuration_vector)触发寄存器0的重新更新,需先取消该信号断言再重新断言。 |

| reset | IP复位信号,高电平有效 |

上述配置项可以通过constant模块进行配置,具体数值如下:

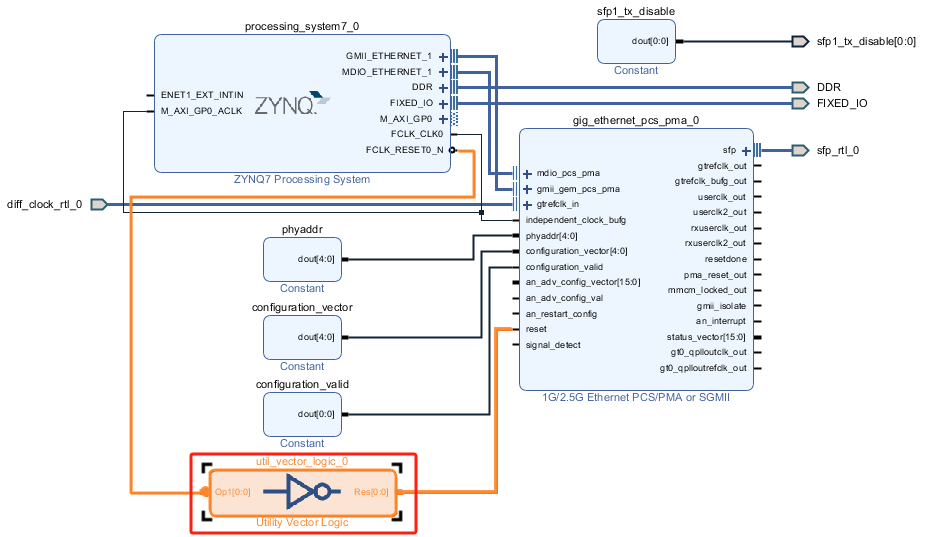

reset信号由于是高电平有效,所以可以直接使用constant模块置0或者通过反相器接入fclk_reset0_n,这里通过反相器接入fclk_reset0_n信号,如下:

最终连线完如上图。

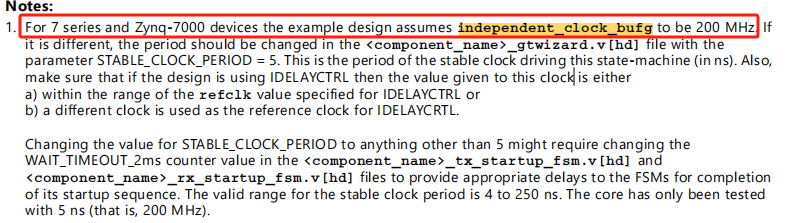

其他注意项:

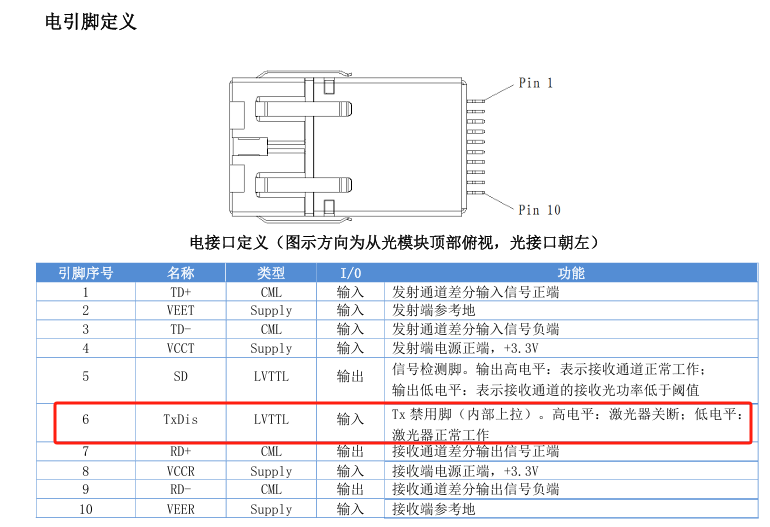

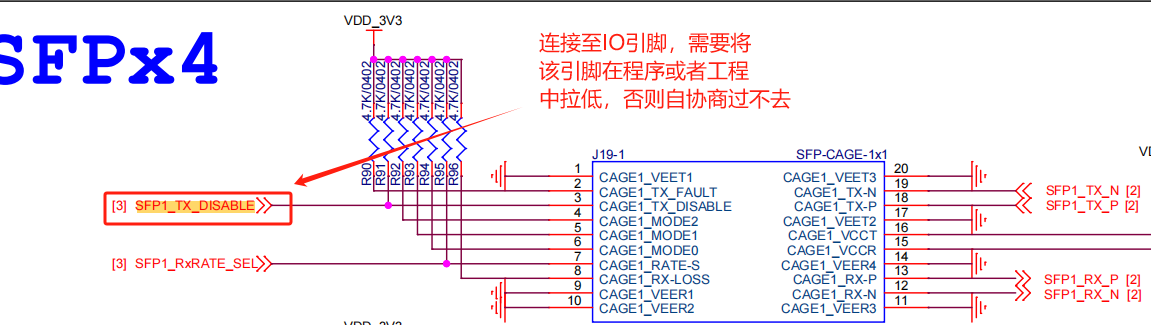

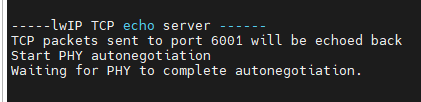

个别电路的SFP模块会将tx_disable信号接入emio引脚,需要在工程中将该引脚约束并拉低,否则以太网测试过程中会卡在自协商阶段,如下图:

以上配置完成后进入SDK工程测试即可。

完整工程

以上完整工程创建可以通过以下tcl文件进行创建,步骤如下:

zynq7z045_gmac1_sfp.tcl

- 将tcl文件存放在新建的英文名称文件夹下

- 打开vivado软件

- 进入vivado tcl命令行,通过命令行进入存放tcl文件的文件夹下

- 继续输入以下命令完成工程的基础创建

source zynq7z045_gmac1_sfp.tcl - 创建工程的引脚约束

- 生成bit并导出硬件设计到sdk

- 通过sdk测试硬件功能

参考文档:

《pg047-gig-eth-pcs-pma.pdf》

6718

6718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?