关注、星标公众号,精彩内容每日送达

来源:网络素材液晶屏有RGB TTL、LVDS、MIPI、HDMI接口,这些接口区别于信号的类型(种类),也区别于信号内容。

具体RGB TTL接口信号类型是TTL电平,信号的内容是RGB666或者RGB888还有行场同步和时钟;

LVDS接口信号类型是LVDS信号(低电压差分对),信号的内容是RGB数据还有行场同步和时钟;

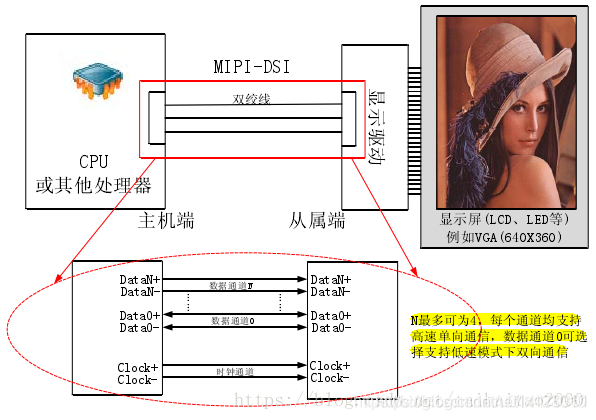

MIPI DSI接口信号类型是LVDS信号,信号的内容是视频流数据和控制指令。

简单理解,LVDS 和MIPI的物理接线是一样的,都是5组差分对,但是传输的内容是不一样的,即软件的报文格式不一样。

各种接口对比如下图所示:

| 接口类型 | 信号线 | 极限速率 | 最大速率 | 抗干扰能力 | 适用摄像头像素 | PCB laypuit | |

| MIPI CSI-2 | 串口 CLKP/N、DATAP/N 最大支持4-lane 一般2-lane可以搞定 | Gbps | 低压差分信号,产生的干扰小,抗干扰能力也强 | 支持800W以上 | lvds接口耦合,走线必须差分等长 | ||

| DVP | 并口 PCLK、VSYNC、HSYNC D[0:11] 支持8/10/12bit数据 | PCLK极限96M左右 | PCLK最好控制在72M以下 | 最大500W | 阻抗要求低 | ||

| FPD-Link III LVDS | 串口 | 阻抗要求高 | |||||

| GMSL | 串口 | Gbps | 阻抗要求高 |

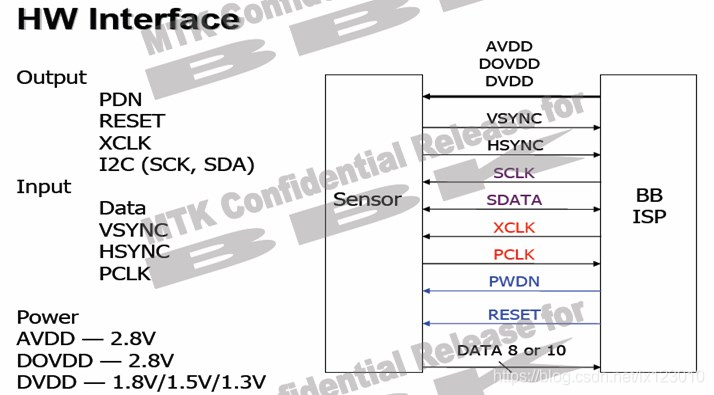

DVP接口

DVP分为三个部分:输出总线;输入总线;电源总线;

>>输入总线介绍

a>PWDN是camera的使能管脚,有两种配置方式,一种为standby,一种是normal work,设置为standby的时候,一切对camera的操作都是无效的,包括复位。所以在RESET之前,一定要将PWDN管脚设置为normal模式,否则RESET无效。

b>RESET是camera的复位管脚,此方式为硬复位模式,camera的各个IO口恢复到出厂默认状态。只有在XCLK开启后,将RESET置为低,硬复位才有效,否则复位无效。

c>XCLK是camera的工作时钟管脚,此管脚为BB提供camera的工作时钟。

d>IIC是camera和BB通信的总线通道。

>>输出总线介绍

a>data为camera的数据管脚。此数据脚可以输出的格式有YUV、RGB、JPEG等。

b>VSYNC为camera的帧同步信号管脚。一个VYSNC信号结束表示一帧(即一个画面)的数据已经输出完毕。

c>HSYNC为camera行同步信号管脚。一个HSYNC信号结束表示一行的数据已经输出完毕。

d>PCLK为像素同步信号管脚。一个PCLK信号结束表示一个像素点的数据已经输出完毕。

>>Power线介绍

a>AVDD为camera的模拟电压。

b>DOVDD为camera的GPIO口数字电压。

c>DVDD为camera的核工作电压。

DVP接口在信号完整性方面受限制,速率也受限制。500W还可以勉强用DVP,800W及以上都采用MIPI接口。

MIPI接口

MIPI(Mobile Industry Processor Interface)移动产业处理器接口是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

其优点是;更低功耗、更高数据传输率和更小的PCB占位空间,并且专门为移动设备进行的优化,因而更适合手机和智能平板的连接。

MIPI CSI和DPI是MIPI标准的一种,因为MIPI在移动领域应用范围太广了,各种外围设备都可以用它来传输信息,所以,MIPI联盟给不同的外设接口定义了版本名,CSI是for Camera的,DPI是for Display的。而且这些标准不单包括物理层的时序定义,还包括上层的传输协议/数据处理协议和应用层协议。

C-PHY:C-PHY主要时为了提高传输的带宽,C-PHY没有同步时钟,时钟时嵌套在数据中。其中物理层和D-PHY完全不同,线路上采用A/B/C三线系统等等。

D-PHY:提供了对DSI (串行显示接口)和CSI(串行摄像头接口)在物理层上的定义,采用一个差分时钟和1-4对差分数据线来传输数据。D-PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号,用于传输图像信号,数据传输采用DDR方式,即在时钟的上下边沿都有数据传输,数据传输速率为80M~2.5Gbps,功耗较高。LP模式下采用单端信号(LVCMOS信号),用于传输初始化控制信号,数据速率小于10Mbps,功耗较低。目前MIPI中运用的最多。

lane:MIPI里面的基本信息传输单元。两块使用MIPI连接的芯片,中间使用差分信号对进行连接,收发端各有一个Lane模块,完成数据收发。有时我们经常说的几个lane传输数据,可理解成几对差分对传输数据。注意:lane并不是差分对,它是收发器里面的一个模块,它包括低功耗发射器(LP-TX),低功耗接收器(LP-RX),高速发射器(HS-TX),高速接收器(HS-RX),低功耗竞争检测器(LP-CD)。

工作模式

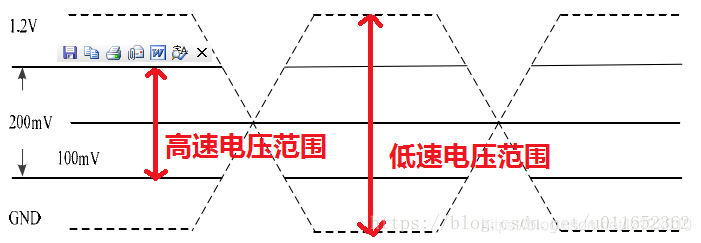

D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。全部数据通道都可以用于单向的高速传输,但只有第一个数据通道才可用于低速双向传输,

HS模式下采用低压差分信号,电平范围为100mv-300mv,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps);在该模式下传输时,当差分线正端收到 1.2V 信号,负端收到 0V信号时,这时接收端识别为 1。反之为0。

LP 低功耗模式,用于传输控制指令,异步传输,信号线为单端,电平范围是0-1.2v,没有用时钟线,时钟是通过两个数据线异或而来的,速度只有10Mbps。在该模式下传输时,当正端接收到300m V,负端接收到100m V 时接收端识别为1,反之则识别为0.

MIPI接口比DVP的接口信号线少,由于是低压差分信号,产生的干扰小,抗干扰能力也强。

两种模式的结合保证了MIPI总线在需要传输大量数据(如图像) 时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

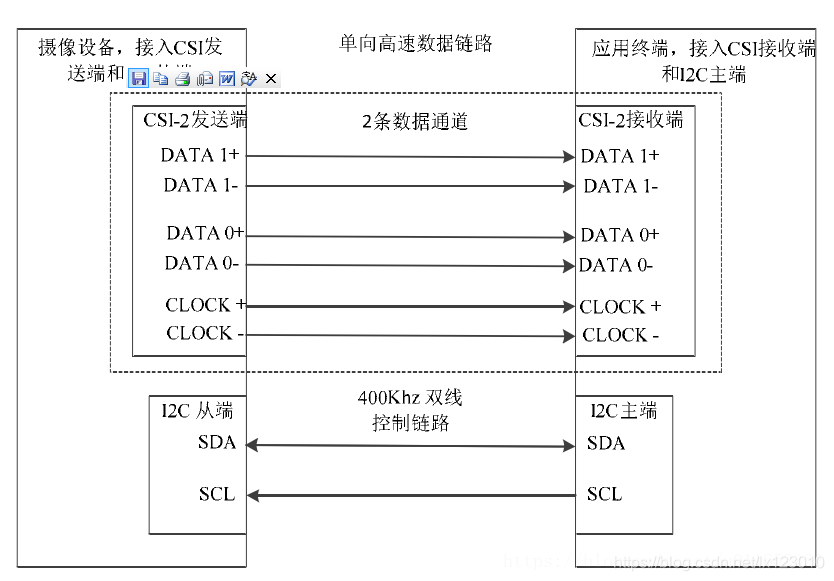

MIPI CSI2的物理连接

除地线外,MIPI CSI2一般会有1对I2C通信引脚,1对MIPI差分时钟引脚和1~4对MIPI差分数据信号引脚,如图所示。

CSI(Camera Serial Interface)是由MIPI联盟下Camera工作组指定的接口标准。单线传输速度高达1Gb/s。

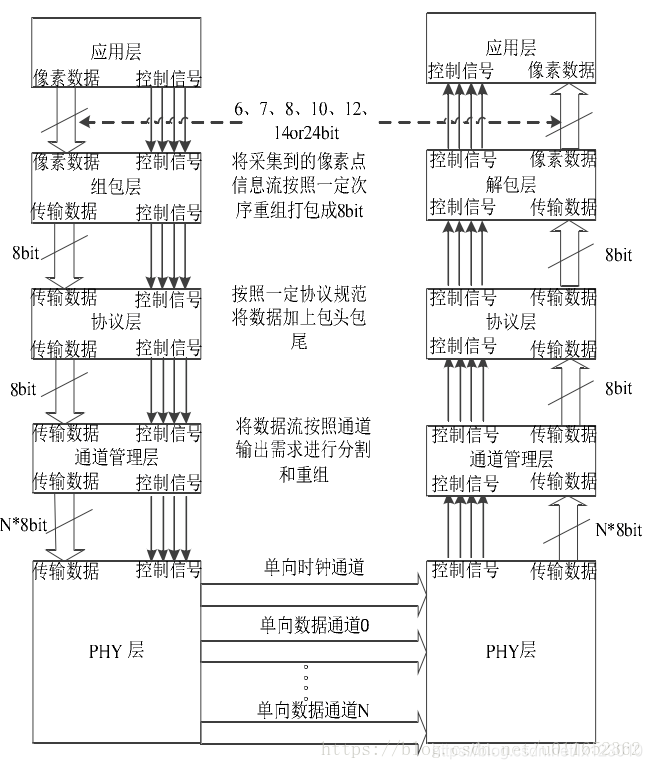

MIPI CSI2的分层方法有好几种,根据MIPI联盟的规范,CSI2可分为5层,分别为:应用层、组包/解包层、底层协议层(Low Level Protocol)、通道管理层和物理层。

详细的来说,链路的工作顺序如下:

首先原始的图像数据会在应用层做相应的图像处理,包括白平衡、噪声去除、色彩还原等。

处理过后的数据进入组包层做数据分割和重组,再传给协议层。

协议层根据数据类型产生包头,根据数据内容产生构成包尾的 校验序列,之后将包头、数据本身、包尾组合起来发送给通道管理模块。

通道管理模块按照通道的选通情况,合理分配数据到每个通道,之后数据经过数模转换进入物理层传输,接收端在收到物理层的数据后,再按照之前的逆序解包出原始的图像数据。

MIPI-DSI接口

LVDS接口

LVDS(Low Voltage Differential Signaling):低电压差分信号,属于平衡传输信号。

这种技术的核心是采用极低的电压摆幅高速差动传输数据,LVDS的传输距离推荐的最高数据传输速率是655Mbps,而理论上可以达到1.923Gbps。

由于电压信号幅度较低,而且采用恒流源模式驱动,故只产生极低的噪声,消耗非常小的功率,甚至不论频率高低功耗都几乎不变。此外,由于LVDS以差分方式传送数据,所以不易受共模噪音影响,属于平衡传输信号。

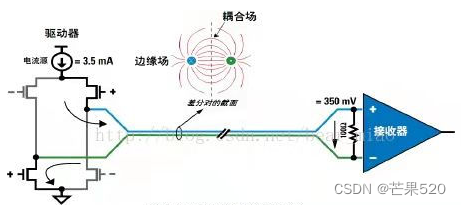

LVDS传输原理:

LVDS的基本工作原理如上图所示。其源端驱动器由一个3.5mA的恒流源驱动一对差分信号线组成。接收端的接收器为高输入阻抗,所以几乎全部的驱动电流都流经100Ω的终端匹配电阻,并在接收器输入端产生约350mV的电压。当源端驱动状态反转变化时,流经匹配电阻的电流方向改变,于是在接收端产生高低逻辑状态的变化。即输出直流偏置为1.2V,输出差分摆幅为-350mV—+350mV。

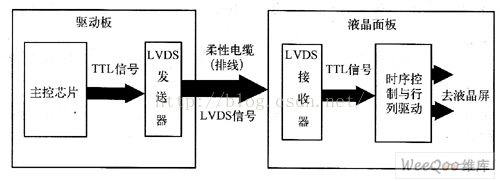

LVDS发送器将驱动板主控芯片输出的TTL电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

本质:并/串转换(SerDes),电平转换(RGB TTL / LVDS);以RGB666为例,采用并行接口往往需要22根线,而采用FPD-Link却只需要四对差分线(一对时钟,三对数据)

LVDS接口分类

单路6位LVDS:采用单路方式传输,每个基色采用6位数据,共18位RGB数据;

双路6位LVDS:采用双路方式传输,每个基色采用6位数据,奇路数据为18位,偶路

数据为18位,共36位RGB数据;

单路8位LVDS:采用单路方式传输,每个基色采用8位数据,共24位RGB数据;

双路8位LVDS:采用双路方式传输,每个基色采用8位数据,奇路数据为24位,偶路

数据为24位,共48位RGB数据;

LVDS发送芯片介绍

典型之LVDS发送芯片分为四通道、五通道和十通道几种。

四通道LVDS发送芯片

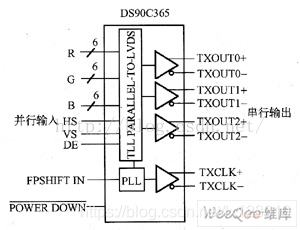

下图所示为四通道LVDS发送芯片内部框图。包含了三个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。

4通道LVDS发送芯片主要用于驱动6bit液晶面板。使用四通道LVDS发送芯片可以构成单路6bit LVDS接自电路和奇/偶双路6bit LVDS接口电路。

五通道LVDS发送芯片

下图所示为五通道LVDS发送芯片(DS90C385)内部框图。包含了四个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和一个时钟信号发送通道。

五通道LVDS发送芯片主要用于驱动8bit液晶面板。使用五通道LVDS发送芯片主要用来构成单路8bit LVDS接口电路和奇/偶双路8bitLVDS接口电路。

十通道LVDS发送芯片

图4所示为十通道LVDS发送芯片(DS90C387)内部框图。包含了八个数据信号(其中包括RGB、数据使能DE、行同步信号HS、场同步信号VS)通道和两个时钟信号发送通道。

十通道LVDS发送芯片主要用于驱动8bit液晶面板。使用十通道LVDS发送芯片主要用来构成奇/偶双路8bit LVDS位接口电路。

在十通道LVDS发送芯片中,设置了两个时钟脉冲输出通道,这样做目的是可以更加灵活之适应不同类型之LVDS接收芯片。

LVDS发送芯片的输入信号

LVDS发送芯片的输入信号来自主控芯片,输入信号包含RGB数据信号、时钟信号和控制信号三大类。为了说明方便,将RGB信号以及数据选通DE和行场同步信号都算作数据信号。

输入数据信号

在供6bit液晶面板使用之四通道LVDS发送芯片中,共有十八个RGB信号输入引脚;一个显示数据使能信号DE(数据有效信号)输入引脚;一个行同步信号HS输入引脚;一个场同步信号VS输入引脚。也就是说,在四通道LYDS发送芯片中,共有二十一个数据信号输入引脚。

在供8bit液晶面板使用之五通道LVDS发送芯片中,共有二十四个RGB信号输入引脚;一个显示数据使能信号DE(数据有效信号)输入引脚;一个行同步信号HS输入引脚;一个场同步信号VS输入引脚;也就是说,在五通道LVDS发送芯片中,共有二十八个数据信号输入引脚。

应该注意的是,液晶面板的输入信号中都必须要有DE信号,但有的液晶面板只使用单一的DE信号而不使用行场同步信号。因此,应用于不同的液晶面板时,有的LVDS发送芯片可能只需输入DE信号,而有的需要同时输入DE和行场同步信号。

输入时钟信号

即像素时钟信号,也称为数据移位时钟(在LVDS发送芯片中,将输入之并行RGB数据转换成串行数据时要使用移位寄存器)。像素时钟信号是传输数据和对数据信号进行读取之基准。

控制信号(POWER DOWN)

当此信号有效时(一般为低电平时),将关闭LVDS发送芯片中时钟PLL锁相环电路之供电,停止IC之输出。

LVDS与MIPI的区别主要有两点:

1、LVDS接口只用于传输视频数据,MIPI DSI不仅能够传输视频数据,还能传输控制指令;

2、LVDS接口主要是将RGB TTL信号按照SPWG/JEIDA格式转换成LVDS信号进行传输,

MIPI DSI接口则按照特定的握手顺序和指令规则传输屏幕控制所需的视频数据和控制数据。

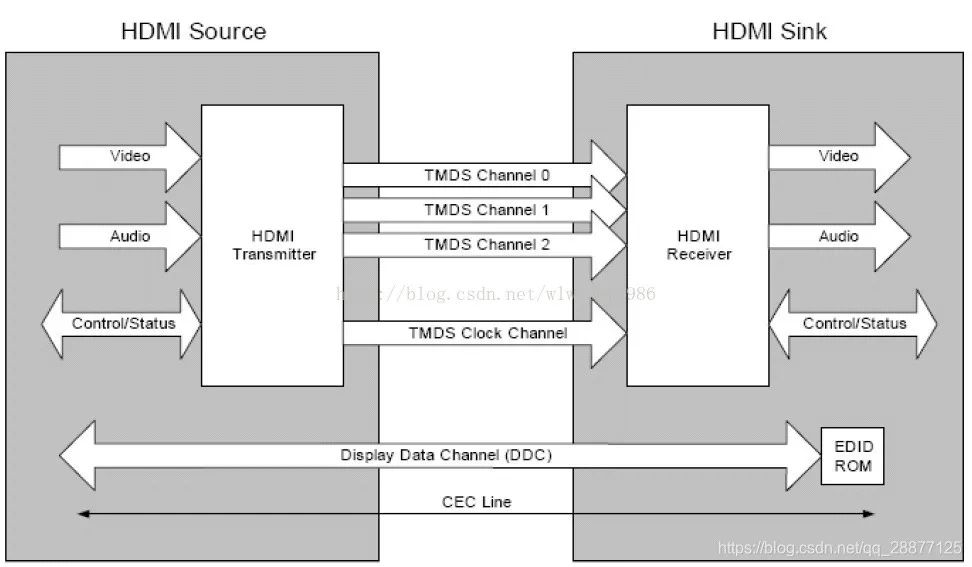

HDMI接口

(1)接口定义

a. High-Definition Multimedia Interface

b. 数字接口,同时传输视频和音频

c. 传输非压缩视频数据和压缩/非压缩的数字音频数据

(2)发展历史

a. 2002年4月,日立、松下、飞利浦、Silicon Image、sony、汤姆逊、东芝共7家公司成立了HDMI组织,开始制定新的专用于数字视频/音频传输标准。

b. 2002年12月,发布HDMI 1.0

c. 2005年8月,发布HDMI 1.2

d. 2006年6月,发布HDMI 1.3

e. 2009年11月,发布HDMI 1.4

f. 2013年9月,发布HDMI 2.0

| HDMI Version | 1.0 | 1.1 | 1.2 | 1.3 | 1.4 | 2.0 |

|---|---|---|---|---|---|---|

| Max TMDS Throughput | 1.65Gbps | 1.65Gbps | 1.65Gbps | 3.4Gbps | 3.4Gbps | 6Gbps |

| Max Audio Throughput | 36.86Mbps | 36.86Mbps | 36.86Mbps | 36.86Mbps | 36.86Mbps | 49.152Mbps |

| Max Color Depth | 24bit | 24bit | 24bit | 48bit | 48bit | 48bit |

| Max Resolution | 1920x1200@p60 | 1920x1200@p60 | 1920x1200@p60 | 2560x1600@p75 | 4096x2160@p30 | 4096x2160@p60 |

(3)HDMI特点

a. TMDS

Transition Minimized Differential Signal

8bit~10bit直流平衡编码

每个时钟周期传输10bit数据

b. EDID and DDC

实现设备间只能连接

c. Transfer Video and Audio

更低成本、连接更方便

d. HDCP

High-Bandwidth Digital Content Protection

(4)HDMI接口类型

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

404

404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?