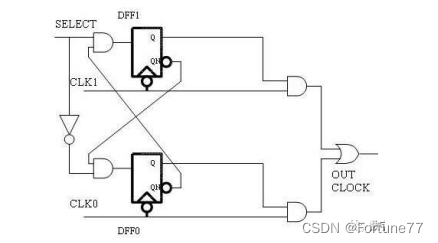

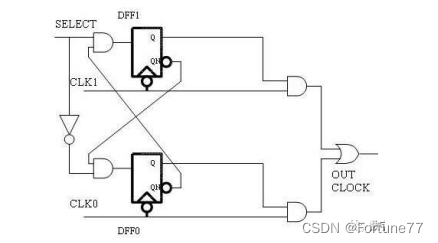

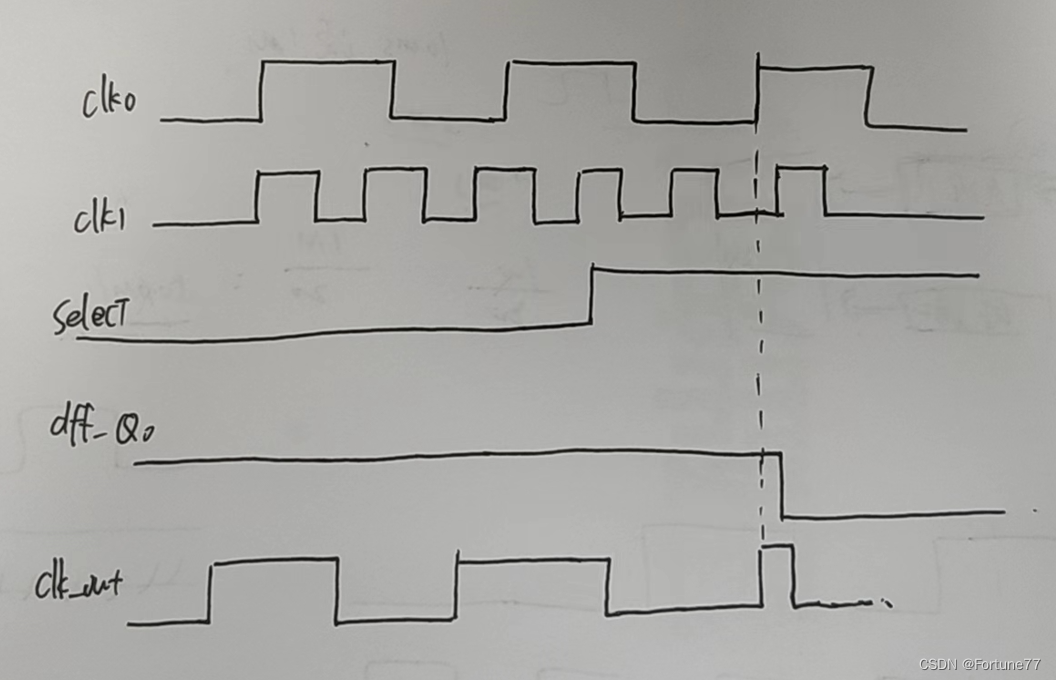

在时钟切换电路中为什么用两个下降沿的触发器会避免毛刺的出现,原因在后面的与门。

假设为上升沿变化,以clk0为例,按理来说经过DFF之后,Q的变化沿和clk0的变化沿是同步变化,但是DFF可能会出现延迟,所以Q端的信号可能会晚到,这样还在上升沿变化的话,晚到的Q端会和CLK0相与,出现毛刺。但是用下降沿的话可以避免这个问题,就算晚到了,也是和0进行相与,所以没影响。

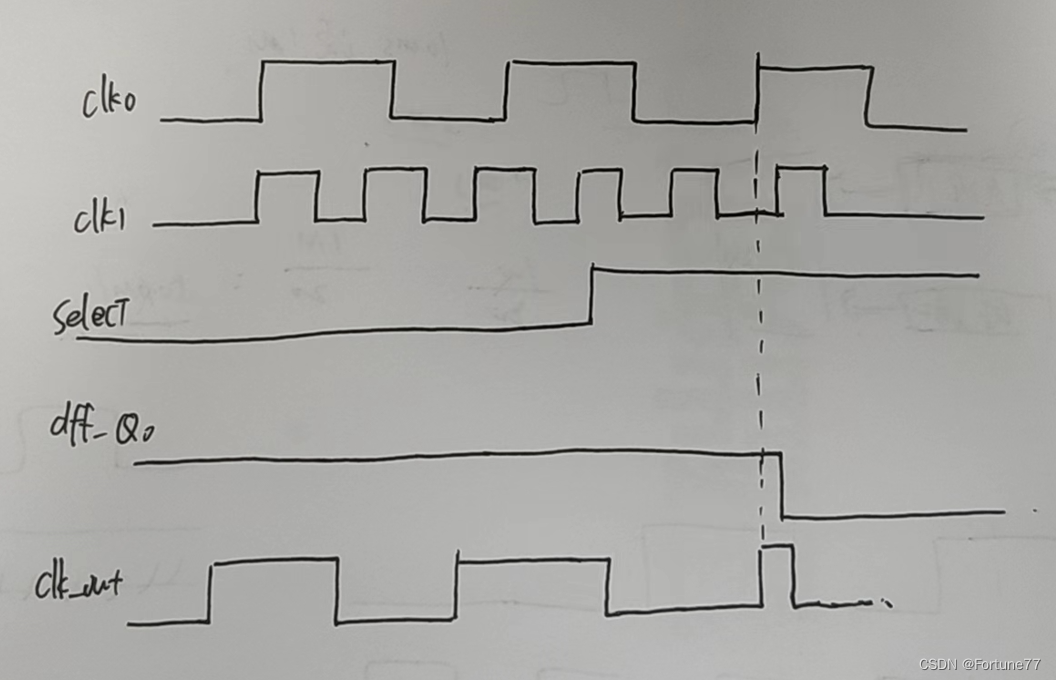

示意图如下所示:

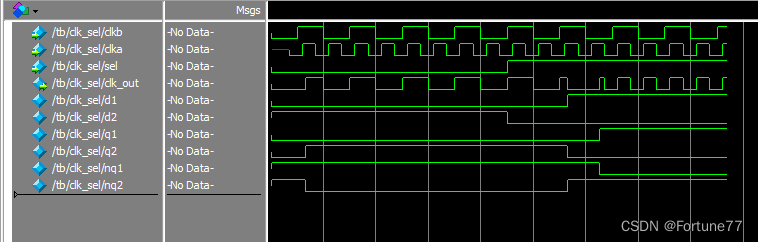

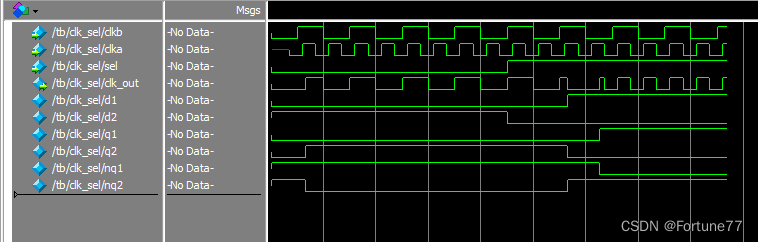

具体的仿真图如下所示

在时钟切换电路中为什么用两个下降沿的触发器会避免毛刺的出现,原因在后面的与门。

假设为上升沿变化,以clk0为例,按理来说经过DFF之后,Q的变化沿和clk0的变化沿是同步变化,但是DFF可能会出现延迟,所以Q端的信号可能会晚到,这样还在上升沿变化的话,晚到的Q端会和CLK0相与,出现毛刺。但是用下降沿的话可以避免这个问题,就算晚到了,也是和0进行相与,所以没影响。

示意图如下所示:

具体的仿真图如下所示

1218

1218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?