更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们

这次我们来谈谈硬件架构,其实没啥好说的,就是科普的东西。因为这个玩意儿真的没啥新意

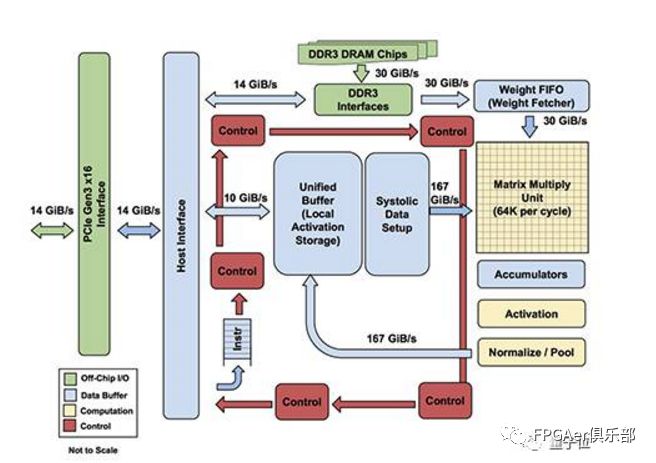

第一款:google的TPU 架构

图中DDR3仅仅是用来传送数据量小的权重,因为DDR3的速度实在是跟不上啊。而激活值采用167GiB/S 的速度传入和传出,中间那个矩阵乘法器是65536个 ,运算力相当野蛮吧。中间就是一些控制逻辑——不同层控制不同,还有就是一些为了保障速度的辅助逻辑。

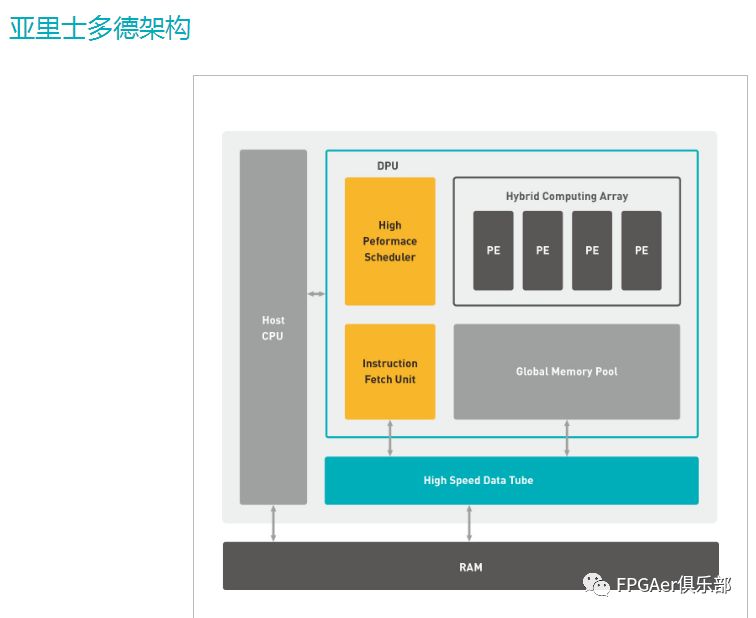

第二款: 深鉴科技的DPU

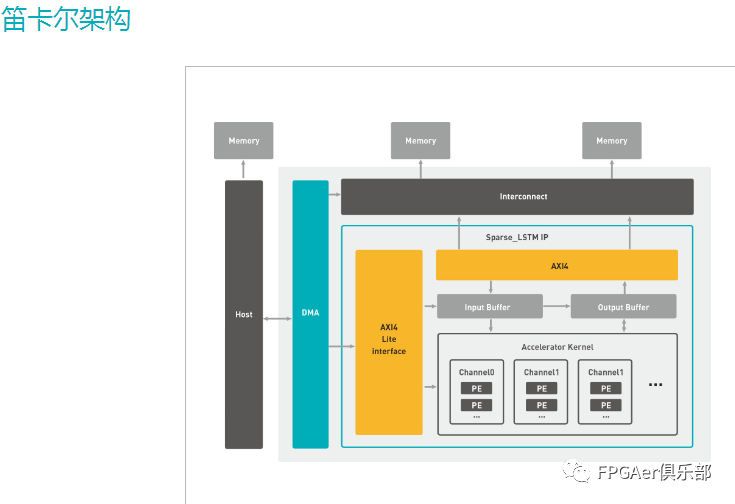

由上面的TPU过渡到下面的DPU 感觉如何,上一博文中说了,就是input buffer, 处理,output buffer ,然后看这两个buffer里面的数据怎么来最快,怎么去的最快。over。有多少资源就设计多大的处理器,资源决定了你流水多少。如此,你的latency的出来了,嗯,于是你的整个项目性能就大概出来了。

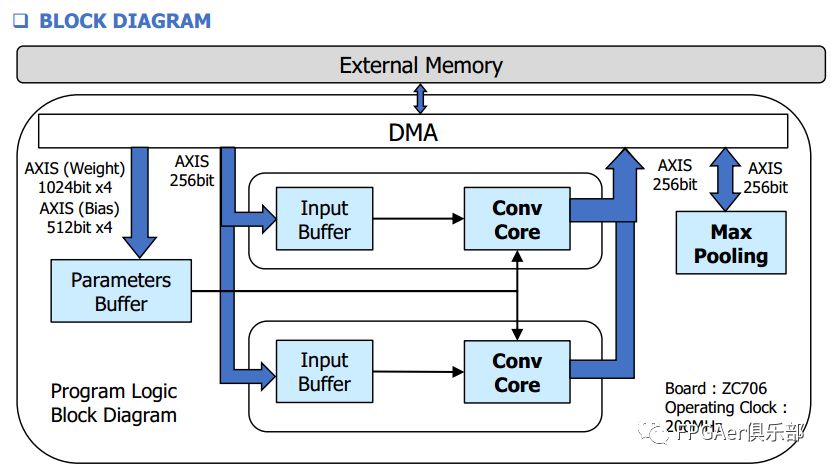

第三款:某公司用ZC706做的项目架构

呵呵,上面都说完了,这个图的文案我都不知道扯啥了。

哦,这个是用HLS 做的,应该是卷积和pooling是两个独立IP ,没有合并起来,所以对AXI总线多了两次操作,或许可以合并的呢

本文转载自:http://www.cnblogs.com/sepeng/p/8572762.html,如涉及版权,请私信小编删除。

============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。

这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办FPGA技术讲座,分享相关研究文献。

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。

538

538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?