1.学习目标:设计3—8译码器

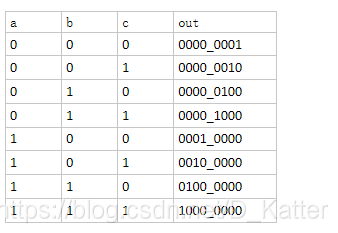

2.真值表

3.编写verilog代码

//声明

module decoder3_8(

a,b,c,

out

);

//说明

input a;

input b;

input c;

output [7:0]out;

reg [7:0] out; //因为out在always块中使用,要定义成reg类型

//时序逻辑

always @(a,b,c) //always@(*)

begin

case({a,b,c})

3'b000: out=8'b0000_0001;

3'b001: out=8'b0000_0010;

3'b010: out=8'b0000_0100;

3'b011: out=8'b0000_1000;

3'b100: out=8'b0001_0000;

3'b101: out=8'b0010_0000;

3'b110: out=8'b0100

这篇博客主要介绍了在学习FPGA过程中设计3-8译码器的步骤,包括理解真值表,编写Verilog代码,以及遇到的关于数据类型的问题。在Verilog中,数据表示有三种形式,如8'b0000_0001,且在case语句中未指定位宽会导致错误。此外,文章还提及了x和z的特殊含义,以及如何书写具有可读性的数字。参考文献包括两本FPGA相关书籍。

这篇博客主要介绍了在学习FPGA过程中设计3-8译码器的步骤,包括理解真值表,编写Verilog代码,以及遇到的关于数据类型的问题。在Verilog中,数据表示有三种形式,如8'b0000_0001,且在case语句中未指定位宽会导致错误。此外,文章还提及了x和z的特殊含义,以及如何书写具有可读性的数字。参考文献包括两本FPGA相关书籍。

订阅专栏 解锁全文

订阅专栏 解锁全文

16万+

16万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?